Устройство для контроля полупроводниковой памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социапистическнк

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22)Заявлено 16.01.81 (21) 3239 91у18 24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 23. 07. 82. Бюллетень № 27

Дата опубликования описания 25. 07. 82 (51)M. Кл.

G 11 С 29/00

1Ьоударотеенкы5 комитет

СССР по делам изобретений н открытей (53) УЛK681. .327(088.8) А. И. Волох, В. Г. Рябцев, В. В. Кулак

Н.И. Холохолов и А.Ф. Шамарин в, НВфффцр»

>к ° °

,10.

Т ГУР .,„ авляЬ йе11уцыисли е (72) Авторы изобретения

Научно-исследовательский институт машин льных (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОВОДНИКОВОЙ

ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля полупроводниковой памяти, которое содержит блоки сопряжения, блок управления, генераторы импульсов и блок формирования временной диаграммы (1).

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля полупроводниковой памяти, содержащее блок управления, блок формирования данных и блок формирования адреса, состоящий из регистра текущего адреса, вспомогательного регистра, регистра начального адреса, регистра конечного адреса и устройства для сравнения адресов Е23.

Недостатком этого устройства является низкое быстродействие, т.е. для изменения значений, начального и ко2 нечного адресов проверяемого массива требуется дополнительное время для перепрограммирования.

Целью изобретения является повышение быстродействия устройства.

5 Поставленная цель достигается тем, что в устройство для контроля полупроводниковой памяти, содержащее блок управления, входы и один из выходов которого подключены соответственно к одним из выходов и входов первого и второго блоков сопряжения, блока формирования данных и первого блока формирования адреса, введены второй блок формирования адреса и коммутаторы, один из входов которых соединены с одними из выходов второго блока формирования адреса, один из входов которого подключены к другим выходам первого блока го формирования адреса и другим входам коммутаторов, а другие входы и выходы являются управляющими, другие входы и выходы второго блока сопря945904

3 жения соединены соответственно с выходами коммутаторов и другими входами блока формирования данных.

Второй блок формирования адреса содержит адресные регистры и схему сравнения, входы которой подключены к выходам первого и второго адресных регистров соответственно, одни из входов первого и второго адресных регистров объединены и являются 10 одними из входов блока, выходы второго адресного регистра и схемы сравнения являются выходами блока, другие входы адресных регистров объединены и являются другими входами 1з блока.

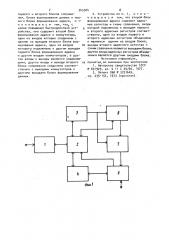

: На фиг, 1 приведена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема второго блока формирования адреса; на фиг. 3 - функциональная схема блока управления; на фиг. 4 — функциональная схема первого блока формирования адреса; на фиг. 5 - схема блока формирования данных.

Устройство содержит первый блок 1 сопряжения, предназначенный для ввода .программ с ЭВМ и передачи результатов контроля на ЭВМ для их обработки и вывода на печать, блок 2 управления, первый блок 3 формирования адреса, предназначенный .для формирования кода адреса ячеек памяти микросхемы (БИС, ОЗУ), входящей в состав информационного разряда проверяемой памяти, блок

4 формирования данных, предназначенный для формирования кода информации слова, поступающего на проверяемую память, второй блок 5 сопряжения, предназначенный для передачи кода адреса, кода данных (информационного

40 слова) и управляющих сигналов на проверяемую память и для приема считанной информации, второй блок 6 формирования адреса, предназначенный для формирования начального кода адреса микросхемы, входящей в информационный разряд проверяемой памяти, и коммутаторы 7.

Второй блок формирования адреса содержит первый 8 и второй 9 адресные регистры, предназначенные соответственно для хранения конечного адреса ячейки памяти информационного разряда и начального адреса одной иэ проверяемых микросхем, входящих в состав информационного разряда проверяемой памяти, и первую схему 10 сравнения.

Блок управления содержит дешифратор 11 команд, -накопитель 12, программные регистры 13 и формирователь

14 синхроимпульсов.

Первый блок формирования адреса содержит первый информационный регистр 15, вторую схему 16 сравнения, третий 17, четвертый 18 и пятый 19 адресные регистры.

Блок формирования данных содержит регистр 20 длины слова, второй 21, третий 22 и четвертый 23 информационные регистры и третью схему 24 сравнения.

Устройство работает следующим образом.

Перед началом работы в накопитель

12 блока 2 управления заносится программа проверки либо с панели управления устройства (на фиг. 1 не показан), либо из ЭВМ, либо периферийного устройства через блок 1. Если, например, каждый информационный разряд проверяемой памяти содержит несколько микросхем памяти, то в командах загрузки регистров информация для занесения содержит в регистре 18 все "0", в регистре 17 код последнего адреса ячейки памяти одной микросхемы, а в регистре 8 - код последнего адреса ячейки памяти всего информационного разряда.

Например, если емкость разряда проверяемого изделия составляет шестнадцать бит и содержит четыре микросхемы по четыре К бит, то код регистра 17 содержит 0000111111111111, а регистра 8 †.00111111111111.

В программе проверки также должна быть занесена команда, по которой производится анализ сигнала сравнения регистров 17 и 9.

По сигналу пуска устройства в одном иэ программных регистров 13 устанавливается адрес ячейки памяти, с которого начинается программа проверки. Код адреса поступает в накопитель 12 для выборки информации.

Информация из накопителя 12 поступает на дешифратор 11, где определяется признак команды и условия для считывания следующей команды, которые поступают на регистры 13, запоминаются там и выдаются в накопитель

12, из которого .новая информация снова поступает на дешифратор 11. В процессе считывания информации устанавливаются начальный и конечный адреса ячеек памяти проверяемой мик94590 росхемы, конечный адрес информационного разряда, частота обращения к проверяемой памяти в формирователе

14, код информационного слова в регистре 22, после чего начинается

5 выполнение программы тестов, в процессе которой по определенным сигналам из дешифратора 11 производится запись или считывание информации из проверяемой памяти, изменение >0 данных, записываемых в нее и изменение адресов ячеек памяти. Также в соответствии с кодом команды опрашиваются другие блоки и регистры устройства, анализируется их состояние и выдаются сигналы управления на регистры 13, управляющие работой как накопителя 12, так и дешифратора 11.

После проверки одной микросхемы памяти в каждом информационном разряде по всем тестам производится анализ состояния схемы 10 сравнения, в которой сравнивается информация 25 регистра 8 и регистра 9 и в случае неравенства информации на регистр

9 поступает счетный импульс и происходит подключение следующей микросхемы информационного разряда к про-- 30 верке и переход на начало выполнения тестов. При получении сигнала совпадения информации в регистрах 8 и 9 (когда закончится проверка последней микросхемы памяти в каждом информа55 ционном разряде) формируется адрес ячейки накопителя 12, в которой хранится команда конца. проверки. По этой команде прекращается проверка контролируемой памяти.

40 считанная из проверяемой памяти информация запоминается на некоторое время в регистре 21 и передается на схему 24 сравнения, где она сравнивается с информацией, присутствующей на регистре 22 при наличии разрешающего сигнала с регистра 20 и стробирующего импульса с формирователя 10,. В случае несовпадения ин50 формации, содержащейся на регистре

22 и регистре 21, схема 24 сравнения выдает импульс ошибки на дешифратор

11, который производит переход на ячейку с командой "Брак", происходит останов работы устройства.

S$

Так как память может проверяться с разной информационной разрядностью, то регистр 22 разрешает сравнение

4 6 только выбранных разрядов, т.е. тех разрядов, при загрузке которых в регистр 22 занесены "1".

В процессе выполнения сложных тестов возникает необходимость за— помнить информацию с последующим восстановлением в регистре 22. Запоминание производится регистром 23.

Изменение адреса ячейки контролируемой памяти производится регистром 19. Пределы изменения адреса, ячейки памяти ограничены значениями регистров 17 и 18.

При сравнении кодов регистра 19 с содержимым регистров 18 и 17 вырабатываются импульсы, управляющие работой регистров 13, т.е. производятся переходы с одной подпрограммы контроля на другую с повторением и с возвратами на прежнюю программу.

При формировании сложных тестовыхпоследовательностей бывает необходимым возвращение к определенному ад ресу ячейки проверяемой памяти. Хранение этого адреса производится регистром 15, который может многократно обмениваться информацией с регистром 19.

Передача адреса ячейки памяти на проверяемое изделие производится через коммутаторы 7 и блок 5 с блоков

3 и 6, при этом каждая "l в регистре

17 разрешает прохождение информации с блока 3, а "0" - с блока 6.

Таким образом . производится проверка одной микросхемы памяти в каждом информационном разряде по всем тестам, содержащимся в программе, с последующим переходом на следующую микросхему.

Технико-экономическое преимущество предложенного устройства заключается в том, что оно обеспечивает проверку микросхем, памяти в каждом информационном разряде по всем тестам, содержащимся в программе, без перепрограммирования, за счет чего повышается быстродействие предложенного устройства по сравнению с известными. формула изобретения

1. Устройство для контроля полупроводниковой памяти, содержащее блок управления, входы и одни из выходов которого подключены соответственно:к одним из выходов и входов

945904

7 первого и второго блоков сопряжения, блока формирования данных и первого блока формирования адреса, о тл и ч а ю щ е е с я тем, что с целью повышения быстродействия устройства, оно содержит второй блок формирования адреса и коммутаторы, одни иэ входов которых соединены с одними иэ выходов второго блока формирования адреса, одни иэ входов 10 которого подключены к другим выходам первоГо блока формирования адреса и другим входам коммутаторов, а другие входы и выходы являются управляющими, другие входы и выходы второго >s блока сопряжения соединены соответственно с выходами коммутаторов и другими выходами блока формирования данных.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что второй блок формирования адреса содержит адресные регистры и схему сравнения, входы которой подключены к выходам первого и второго адресных регистров соответственно, одни из входов первого и второго адресных регистров объединены и являются одними из входов блока, выходы второго адресного регистра и схемы сравнения являются выходами блока, другие входы адресных регистров объединены и являются другими входами блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 691929, кл. G 11 С 29/00, 1977.

2. Патент США У 3751649, кл. 235-153, 1973 (прототип).