Цифровой вентильный электропривод

Иллюстрации

Показать всеРеферат

OnИСАНИЕ И ЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (i i) 945945 (61) Дополнительное к авт. свид-ву (22)Заявлено 08.01.81 (21) 3232069/24-07 (53)M. Кл.

Н 02 Р 5/06 с присоединением заявки №вЂ”

3Ьеудэрстеенны6 «эмитет

СССР йв далем нзебретеннй и открытий (23) Приоритет (5Ç) УДК 62-83: . 621 . 313. 2-52(088.8) Опубликовано 23.07.82. Бюллетень № 27

Дата опубликования описания 23.07.82

С. В. Демидов, В. А. Казанский, Э.:,,С. Иучник, В. А. Рыддов и В. А. Яковлев

1 (72) Авторы изобретения (71) Заявитель (54) ЦИФРОВОЙ ВЕНТИЛЬНЬЩ ЭЛЕКТРОПРИВОД с

Изобретение относится к элек роl технике, преимущественно к системам автоматического управления электродвигателями постоянного тока, и может быть использовано в тех отраслях про5 мышленности, где требуются высокие статические и динамические характеристики электроприводов, например в станкостроении в качестве приводов органов металлорежущих станков. 1О

Известен электропривод, содержащий электродвигатель с датчиком частоты вращения, тиристорный преобразователь и цифровой регулятор (1 7.

Наиболее близким по техническои сущности является цифровой электропривод, содержащий последовательно соединенные электродвигатель с датчиком частоты вращения, тиристорный 2о преобразователь, распределитель импульсов, выход датчика частоты вращения соединен с входами цифровогб.регулятора и блока ограничения, фазосдвигающий блок, блок выбора наименьшего сигнала I,2).

Недостатком известного электропривода является относительно невысокое быстродействие.

Цель изобретения — повышение быстродействия электропривода.

Поставленная цель достигается тем, что в электропривод второй фазосдвигающий блок, вход которого подключен к выходу блока ограничения, а выход связан с вторым входом блока выборанаименьшего сигнала, первый вход кОторого связан с выходом первого фазосдвигающего блока, а выход блока выбора наименьшего сигнала соединен с входом распределителя импульсов, вход первого фазосдвигающего блока подключен к выходу цифрового регулятора.

Причем блок выбора наименьшего сигнала выполнен в виде трех схем И, причем первые входы схем И соединены с выходом первого фазосдвигающего блока, вторые входы - с выходом второго. 3 94 9 фазосдвигающего блока, а выходы - с распределителем импульсов.

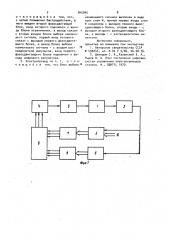

На фиг. 1 и 2 представлены структурные схемы устройства; на Фиг. 3диаграмма работы цифрового вентильного электропривода.

Цифровой вентильный электропривод, содержит последовательно соединенные электродвигатель 1 с датчиком 2 частоты вращения, тиристорный преобразо- !6 ватель 3, распределитель 4 импульсов, выход датчика 2 соединен с входами цифрового регУлятора 5 и блока б ограничения, первый фазосдвигающий блок вход которого соединен с выходом 1 цифрового оегулятора 5, а выход - с первым входом блока 8 выбора наименьшего сигнала, второй вход которого, соединен с выходом второго фазосдви. гаюшего блока 9, вход которого сое- о динен с выходом блока 6, а выход блока 8 соединен с входом распределитеilR, 4

Фазосдвигающие блоки 7 и 9 содержат соответственно блок 10 временной задержки и дешифратор 11, входы которых являются входами Фазосдвигающих блоков 7 и 9,,а выходы блока 10 и дешифратора ll соединены соответственно с первыми и вторыми вхоДами схем И 12, 13 и 14 (Фиг. 2),выходы схем И 12 и 13 и дешифратора 11 соединены с входами схем ИЛИ 1 и 16, выходы которых, а также выход схемы

И 14 являются выходами фазосдвигаю" щих блоков 7 и 9. Блок 8 содержит три схемы И 17, 18 и 19, первые вхо-, ды которых соединены с выходом первого Фазосдвигающего блока 7, а вторые входы - с выходом второго фазосдвигающего блока 9, а выходы схем

И 17, 18 и 19 соединены с входами распределителя 4.

Устройство работает следующим образом { работа .электропривода поясняется диаграммой, представленной на

Фиг. 32.

В начальный момент времени на вход циФрового регулятора 5 подают сигнал управления, соответствующий заданной частоте вращения электродвигателя 1.

На выходе цифрового регулятора фор" мируегся код управления, который по ступает на вход первого фазосдвигающего блока 7. Одновременно блок 6 ограничения реализует заданную функцию or(2oHè÷eHèÿ, и сигHBJl с выхода

45 1 блока 6 поступает на вход фазосдвигающего блока 9.

Фазосдвигающие блоки 7 и 9 выполнены по принципу одноканального управления тиристорным преобразователем

3„ наиболее эффективно реализуемому средствами цифровой техники. Для обеспечения диапазона управления тиристорным преобразователем 3 вплоть до 180 эл. град. входные сигналы фазосдвигающих,блоков 7 и 9 разбиты . по уровню на три поддиапазона, соответствующих количеству интервалов синхронизации за полупериод напряжения питающей сети (фиг. 2, За, б).

Сигнал внутри поддиапазона формируется на управляющем входе блока 10 задержки (фиг. 2). Максимальная амплитуда этого сигнала соответствует максимальному Фазовому сдвигу отпирающего импульса, равному интервалу синхронизации (фиг. Зв - для фазосдвигающего блока 7; фиг. Зм — для Фазосдвигающего блока 9)

Сигнал, соответствующий количеству

1 полных поддиапазонов, содержащихся во: входном коде, формируется на входах дешифраторов 11 (фиг. Зд - для фазосдвигающего блока 7 и фиг. 3c - для фазосдвигающего блока 9).

Блок 10 задержки формирует на своем выходе передний фронт импульса, задний фронт которого совпадает с ближайшим моментом синхронизации фазосдвигающего блока с питающей сетью (как правило, таким моментом синхронизации удобно выбрать точки перехода фазных:.напряжений питающей. сети переменного тока через нуль; фиг. За, б) °

Передний фронт импульса на выходе блока.10 представляет собой точное значение фазового сдвига отпирающегоимпульса внутри поддиапазона (фиг. Згдля фазосдвигающего блока 7; Зн - для фазосдвигающего блока 9) ° Сигнал с выхода блока 10 поступает на первые входы схем И вЂ” 12, !3 и 14 (фиг. 2) °

Дешифратор 11 формирует на своих выходах„сигналы, соответствующие поддиапазонам управления тиристорным преобразователем 3. Эти сигналы представляют собой импульсы, длительность которых равна интервалу синхронизации (фиг. Çe, ж, з - для фазосдвигающего блока 7 и фиг. Зп, р, с - для фазосдвигающего блока 9).Наличие сигнала на первом выходе дешифратора 11 означает, что требуемый угол отпирания тиристоров находится

945 6

Формула изобретения

Цифровой вентильный электропривод, .одержащий последовательно соединенные электродвигатель с датчиком частоты вращения, тиристорный преобразователь, распределитель импульсов, выход датчика частоты вращения соединен с входами цифрового регулятора и блока ограничения, фазосдвигающий блок, блок выбора наименьшего сигнала, . 5 . . 945 в диапазоне от. 0 до 60 .эл.град. счи- . тая влево от конца полупериода напряжения, приложенного к соответствующему тиристору (фиг. Зе, и).

Наличие сигнала на втором выходе дешифратора 11 означает, что требуемый угол отпирания тиристоров находится в диапазоне от 60 до 120 эл.град. (фиг. 3ж, р). Наличие сигнала на третьем выходе дешифратора 11. означает, что требуемый .угол отпирания находит- ся в диапазоне от 120 до 180 эл.град. (фиг. 3з, с) °

С первого выхода.дешифратора 11 сигнал поступает на второй вход схемы 15

И 12, которая на своем выходе формирует сигнал, поступающий на первый вход схемы ИЛИ 15, на два других входа которой поступают сигналы с второго и третьего выходов дешифратора 11. 2о

Схема И 15 формирует на своем выходе сигнал Х (сигнал Х1, фиг. 3п - для фазосдвигающего блока 7 и сигнал Х, фиг, 3м - для фазосдвигающего блока 91

С второго выхода дешифратора 11 25 сигнал поступает на второй вход схемы И 13, которая на своем выходе формирует сигнал, поступающий на первый вход схемы ИЛИ 16, на другой вход. которой поступает сигнал с третьего вы- зо хода дешифратора 12. Схема ИЛИ 16 формирует на своем выходе-сигнал Y (сигнал Yg, фиг. Зк — для фазосдвигающего блока 7 и сигнал У, фиг.3удля фазосдвигающего блока 9).

С третьего выхода дешифратора 11 сигнал поступает на второй вход схемы И 14, которая на своем выходе формирует сигнал Z (сигнал Z, фиг. 3л - > для Фазосдвигающего блока 7, сигнал

Z<, фиг. 3Ф вЂ” для фазосдвигающего . блока 9) . "

Сигналы Х, У< и 2< с выходов фазосдвигающего блока 7 и эквивалентные

45 им сигналы ), Y и 2 с выходов блока 9 поступают на входы блока 8 выбора наименьшего сигнала.

На выходах схем И 17, 18 и 19 происходит выделение наименьшего из

50. соответствующей пары входных сигналов (фиг. 3х, ц, ч) . Далее выделенные сигналы поступают на входы распределителя 4 импульсов (фиг. 2), который

Формирует отпирающие. импульсы и распределяет их по тиристорам преобразо5$ вателя 3 с учетом фазировки сети. Выходное напряжение тиристорного преоб.разователя 3 подается к электродвигателю 1, который разгоняется под действием приложенного напряжения. Информация о текущем значении частоты вращения передается с выхода датчика

2 на вход цифрового регулятора 5, а также на вход блока 6 ограничения

Блок. 5 реализует закон регулирования электропривода, а блок 6 - ограничения, накладываемые на координаты (переменные) электропривода в переходных и установившихся режимах (например, может быть реализована функция упреждающего токоограничения, предельный угол включения тиристоров и т. д.).

В зависимости от количества дополнительно реализуемых ограничений, накладываемых одновременно на управ.". ление, в структуре элекгропривода (фиг. 1 и 2), добавится соответствующее количество фазосдвигающего блоков, работающих параллельно фазосдвигающим блокам 7 и 9. При этом блок 8 выбора наименьшего сигнала остается прежним, у него изменится только число входов логических схем

И 17, l8 и 19 (Фиг. 2). .Как следует из фиг. 2 и 3, формирование временных интервалов, эквивалентных фазовому сдвигу отпирающих импульсов -тиристоров, производится в фазосдвигающих блоках 7 и 9 параллельно.

Следовательно, уменьшается запаздывание в формировании сигналов на входе распределителя 4 импульсов. Это запаздывание не увеличится и в случае реализации дополнительных ограничений на сигнал управления.

С другой стороны, техническая.реализация фазосдвигающих блоков 7 и 9 достаточно проста.

Таким образом, предлагаемый электропривод обладает повышенным быстро. действием и более простой реализацией.

945 отличающийся тем, что, с целью повышения быстродействия, в него введен второй фазосдвигающий блок, вход которого подключен к выходу блока ограничения, а выход связан с вторым входом блока выбора наименьшего сигнала, первый вход которого связан с выходом первого фазосдвигающего блока, а выход блока выбора наименьшего сигнала - с входом распределителя импульсов, вход первого фазосдвигающего блока подключен к выходу цифрового регулятора.

2. Электропривод по и. 1, о т л ич а ю шийся тем, что блок выбора

945 8 наименьшего сигнала выполнен в виде трех схем И, причем первые входы схем

И соединены с выходом первого фазосдвигающего блока, вторые входы - с выходом второго фазосдвигающего блока, а выходы - с распределителем импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

tf 490245, кл. Н 02 P 5/06, 06.08.76.

2. Демидов С. В.,Казанский В. А., Рыдов В. А. Опыт построения цифровых систем управления электроприводов станков. И., ЛДНТП, 1979.