Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ .СВИДЕТЕЛЬСТВУ ()945962

J

/ (6l ) Дополнительное к авт. свид-ву (51) М. Кл.

Н 03 К 5/00 (22) Заявлено 08.12.80 (21) 3 212735/18-21 с присоединением заявки J%

Н 03 В 19/10

3Ьвударстмнньй комнтет

СССР да делам иаабретенкй и открытий (23) Приоритет

Опубликовано 23.07.82. Бюллетень щ 27

Дата опубликования описания 25.07.82 (53) УДК621, . 374.4 (088.8) (72) Авторы изобретения

Л. Г. Бояркнн и P. А. Ивашев (71) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

Изобретение относится к цифровой измерительной технике и может быть использовано как в качестве автономного пртбора, так и в качестве устройства, встраиваемого в информапионно-измерительные системы.

Известен умножитель частоты следования импульсов, содержащий делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, to счетчик импульсов опорной частоты, входной формирователь, запоминающий регистр и блок управления 513

Недостатком этого устройстма является сравнительно невысокая точность 15

4 умножения при неравномерном ттериоде следования импульсов умножаемой частоты.

Наиболее близким по технически ущности является умножитель частоты 20 следования импульсов, содержаший последоватетп но соединенные входной формирователь и блок управления, первый вы ход которого подключен к установечным

2 входам делителя опорной частоты, управляемого делителя частоты и управлякацему входу запоминающего регистра и первому входу триггера, а второй выходк установочному входу счетчика имп аьсов, выход которого через запоминавиций регистр связан с управляющим входом управляемого делителя частоты, источник опорной частоты через делитель частоты связан с входом счет*яка импульсов и непосредственно с входом ключа, управляюший вход которого подключен к выходу триггера j2) .

Недостаток данного устройства - невысокая точность умножения, так как пук неравномерном периоде следовании. импульсов умножаемой частоты число им пульсов им фотвсируемых прн уменьшении периода следования становится мм ьше коэффициента умножения.

1Ьль изобретения - повьппение тощооm умножения.

Поставленная цель достигается тем, что в умножитель частотФ следования

94ÈÎÉ2

3 импульсов, содержащий последовательно соединенные входной формирователь им« пульсов и блок управления, первый выход которого подключен к установочным входам делителя опорной частоты и управляемого депктепя частоты, к управляющему входу запоминающего,регистра и первому входу триггера, а второй выход - к установочному входу счетчика иптульсов, счетный вход которого подключен к выходу делителя опорной частоты, а .выход через запоминающий регистр— к управляющему входу управляемого делителя частоты и источник опорной частоты, выход которого соещшен с входом делителя опорной частоты и первым входом ключа, второй вход которого соединен с выходом триггера, введены пороговый эпемент, элсменты ИЛИ, и элемент запрета, первый вход которого соединен с выходом управляемого делителя частоты, вход которого подключен к синхронизируюшему входу блока управления и к выходу исто дпла опорной частоты, второй вход — с выходом первого элемента ИЛИ, а выход — с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом ключа, а выход — с входом порогового элемента, первый выход которого соединен с вторым входом триггера, выход которого соедшен с первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом порогового элемента.

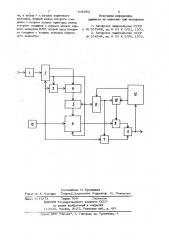

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит входной формирователь 1 импульсов, блок 2 управления, делитель 3 опорной -истоты, управляемый делитель 4 частоты, который может быть вынол:нен в виде счетчика импульсов с элементом сравнения или в виде любого другого известного делителя, упраьпяемого кодом так, что коэф фидиент деления равен числу, передаваемому этим кодом, запоминающий регистр

5, счетчик 6 импульсов, ключ 7, триггер 8, элемент 9 запрета, элементы

ИЛИ 10 и 11, пороговый элемент 12, источник l 3 опорной частоты.

Пороговый элемент 12 является элементом число-импульсного типа и может быть выполнен, например, на базе счетчика и дещпфратора, Срабатывание поро1 2 C0OTBBTCTB .eT MO менту накопления в счетчике числа N =

= К вЂ” 1 юн1 л1 сов, где K — коэффициент умножения.

Устройство работает спедуюшим образом.

Импульсы Ед от источника 13 поступают на вход делителя 3, коэффициент деления которого равен заданному коэффициенту умножения К. Импульсы с выхода делителя 3, частота которых равна

f g tV, поступают на вход счетчика 6.

Одновременно импульсы опорной частоты

К, поступают на вход управляемого де- . лителя 4, коэффициент деления которого равен числу, зафиксированному в регистре 5.

К моменту поступления очередного ыпульса „умножаемой частоты,,, в счетчике 6 фиксируется число m, рав.ное,- Т„ К, где Т; - текущее значекие перйода следовани: импульсов умножаемой частоты. Импульс умножаемой частоты < через формироватепь 1 поступает в блок 2, на синхронизируюший вход которого подаются импульсы опорной частоты о . Блок 2 срабатывает и по переднему фронту иъптульса опорной частоты fo формирует на своем первом выходе импульс, по которому делитель 3 и управляемый делитель 4 устанаыпюайтся в исходное нулевое состояние. На выходе триггера 8 устанавливается единичный сигнал, а число rn зафиксированное к этому моменту в счетчике 6, переписывается в регистр

5 и устанавпивает коэффиииент деления управляемого делителя 4. Затем по заднему фронту импульса на первом выходе бпока 2 на его втором выходе формируется импульс, по которому счетчик 6 устанавливается в исходное нулевое состояние. На выходе управляемого делителя 4 формируется последовательность импульсов с частотой, равной

Уо 4

ФЬ к Щ т;

При единичном сигнале на выходе триггера 8 элемент 9 заблокирован, а ипоч 7 разблокирован, Импульсы опорной частоты Ео проходят через разблокированный ключ 7 и через элемент 11 поступают на выход устройства и на счетный вход порогового элемента 12.

По заднему фронту (К вЂ” 1)-го импульса пороговый элемент 12 срабатывает и на его первом выходе формируется единичный сигнал, который поступает через элемент 10 на управляющий вход элемента 9. По заднему фронту следующего импульса происходит обратное срабатывание порогового элемента 12. При этом на его пеовом выходе устанавлис 4 t- cq

5 вается нулевой сигнал, а на втором вы-! ходе формируется импульс, по которому триггер 8 устанавливается в исходное нулевое состояние. Ключ 7 блокируется, а. элемент 9 запрета разблокируется. В результате на выход устройства и на счетный вход порогового элеМента 12 начинают поступать импульсы с выхода управляемого делителя 4.

Пусть следуюший импульс умножаемой частоты поступает через интервал времени Т„r Т.. Тогда число импуль1+1 сов, формирующихся на выходе управляемого делитепя 4 за интервал времени

Т., превышает порог срабатывания 15

1+» порогового элемента 12. В результате при поступлении на выход устройства

К - 1 импульса с выхода управляемого делителя 4 пороговый элемент 12 срабатывает и блокирует элемент 9. Постут»- 20 ление импульсов с выхода управляемого делителя 4 на выход устройства прекращается. При поступлении импульса умножаемой частоты единичным сигналом триггера 8 разблокируется кл»оч 7 и на вы- 2s ход устройства поступает импульс опорной частоты f, вызывающий обратное срабатывание порогового элемента 12.

Элемент 9 разблокируется и вновь формируемые импульсы управляемого дели- зО . теля 4 начинают поступать на выход устройства, Таким образом, до появления первого импульса вновь формируемой импульсной последовательности на выходе yapaвт»яемого де»»ителя 4 на Выход 35 устройства поступает К вЂ” 1 им»»ульс с выхода управляемого делителя 4 и один импульс опорной частоты Е»», т.е. число импульсов, равное коэффициенту К. .Пусть следующий импульс умножае- 4р мой частоты поступает через интервал времени Т„(T так, что число им1Ф1 пульсов, формирующихся на выходе уп» равляемого делителя 4 и, следовательно, на выходе устройства оказывается мень 45 шим порога срабатывания порогового элемента 12. При поступлении импульса умножаемой частоты элемент 9 блокируется и недостаюшее» до порога сра6атывания число импульсов поступает на счетный вход порогового элемента 12 через разблокированный ключ 7. Следую ший К-ый импульс, поступающий на выход устройства, вызывает обратное срабатывание порогового элемента 12. Элемент 9 разблокируется и на выход устройства начинает поступать вновь форми» руемая последовательность импульсов с выхода управляемого делителя 4. Так как

С2 6

4>) вых . то появле п»е K- о и"" у" са йрактически совпадает с моментом окончания текущего периода Т;+ следования импульсов умножаемой частоты.

При нулевом значении параметра входной частоты ключ 7 оказь»вается заблськирован нулевым сигналом с выхода три» гера 8, а элемент за»трета 9 - единичным сигналом, поступающим с первого выхода порогового элемента 9. В результате подача импульсов на выход устрой1ства прекращается. Следовательно, цри нулевом значении параметра умножаемой частоты значение выходной частоты также равно нулю.

Введение новых элементов - порогового элемента, первого и второго элементов ИЛИ и элемента запрета — выгодно отличает предлагаемое устно»»ство от известного,. поскольку позволяет формировать за текуший период при неравн»>мерном периоде следования импульсов умножаемой частоты число импульсов, равное коэффициенту умножения, т.е. повысить точность умножения.

Формула изобретения

Умножитель частоты следования импульсов, содержащий последовательно соединенные входной формирователь импульсов и блок управления, первый выход которого подключен к установочным входам делителя опорной частоты и упраитяемого делителя частоть», к управляющему входу запоминающего .регистра и первому входу триггера, а второй выход - к установочному входу счетчика импульсов, счетный вход которого подключен к выходу делителя опорной чаототы, а выход через запоминакиций регистр - к управляющему входу управляемого делителя частоты и исто а»ик опорной частоты, выход которого соединен с входом делителя опорной частоты и первь1м входом ключа, второй вход которого соединен с выходом триггера, о тл и ч а ю шийся тем, что, с целью повышения точности, в него введены пороговый элемент, элементы ИЛИ и элемент запрета, первый вход которого соединен с выходом управляемого делителя частоты, вход которого подключен к синхронизирующему входу блока управ= ления и к выходу источника опорной частоты, второй вход — с выходом первого элемента ИЛИ, а выход - с первым входом второго элемента ИЛИ, второй

:вход которого соединен с выходом клю7 9 ча, а выход — с входом порогового элемента, первый выход которого соединен с вторым входом триггера, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом порогового элемента.

2 8

Источники информапии, цринятые во внимание прй экспертизе

1. Авторское свиде гельство СССР

5 № 357668, кл. Н 03 К 5/01, 1971.

2. Авторское свидстепьство СССР № 354546, кл. H 03 К 5/00, 1971.

Составитель О. Кружилина

Редант ор А. Козориз Техред Е.Харитончик Корректор Ю. Макаренко

Заказ 53 18/73 Тираж 959 Подписное

ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

1l3035, Москва, Ж-35, Раушская наб., д. 4/5 пленял ППП Патент", г. Ужгород, ул. Проектная, 4