Преобразователь кода

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социапистичесиии

Респубпнк

О П И С А Н И Е ()945987

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к ввт. свид-ву (22)Заявлено 05.01.81 (21) 3231939/18-21 (5! ) Я. Кд. .3

Н 03 К 13/2$ с присоединением заявки № Ьаударетеенньй камнтет

СССР на делам нзабретеннй н аткрнтнй (23) Приоритет

Опубликовано 23.07.82. Бюллетень № 27 (53) УДК 621, .382 (088.8) Дата опубликования описания 23.07.82

Ленинградский электротехнический институт связи им. проф. M.À. Бонч-Бруевича (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОДА

Изобретение относится к импульсной технике, может быть использовано в устройствах кодирования, передачи данных и технике связи, и, в частности в устройствах компрессий сигнала методами адаптивной дельта - модуляции (АДМ) и дифференциальной импульсно-кодовой модуляции (ДИКМ).

Известны устройства, содержащие сумматор-вычитатель и регистр, в которых

1О на регистре с .помощью сумматора-вычитателя накапливается последователь.» ность положительных и отрицательных кодовых приращений (13.

Однако эти устройства не обеспечивают экспоненциального преобразования накапливаемой суммы, что приводит к ухудшению помехоустойчивости при применении данного устройства (части комплексного устройства) в системе передачи с адап- 0 тивной дельта-модуляцией, являющейся комплексным устройством.

Известен логарифмический преобразователь числа импульсов, содержащий

2 счетчики, выходы которых соединены с входами сравнивающего устройства, а выход последнего подключен к входу

Сброс" счетчика. Входная клемма преобразователя соединена со счетным входом счетчика через ключ, а с входом второго счетчика — через делитель частоты. Второй выход второго счетчика подключен к управляющему входу ключа (2).

Логарифмический преобразователь формирует логарифмическую зависимость времени появления импульсов на выходе устройства. Однако .он не может быть использован в ряде устройств, где .требуется накопление и экспоненциальная обработка последовательности различных по величине s знаку кодовых приращений, например в устройстве адаптивной дельтамодуляции (комплексное устройство.)

Бель изобретения - расширение функциональных возможностей за -счет обеопечения формирования экспоненциального закона спада накапливаемой последователь

3 9459 ности различных положительных и отрицательных кодовых приращений к среднему значению, что необходимо при работе данного устройства в комплексном устройстве стабилизированной адаптивной дельта-модуляции, в результате чего в комплексном устройстве обеспечивается повышение стабильности работы.

Указанная цель достигается тем, что в преооразователь кода, содержащий делитель частоты, первый и второй счетчики.

1 импульсов, сравнивающее устройство и ключ, при этом соответствующие выходы счетчиков импульсов соединены с соответствующими входами сравнивающего уст-1 ройства, выход которого соединен с Входом "Сброс " первого счетчика импульсов, выход делителя частоты соединен с соот« ветствующим входом второго счетчика импульсов, вход ключа соединен с входной2О шиной, введены два управляемых инвертора, триггер и сумматор»вычитатель, причем входы первого и второго управляемых инверторов соединены с выходами соответственно сумматора-вычитателя и второ- го счетчика импульсов, а выходы первого и второго управляемых инверторов соединены с входами соответственно второго счетчика импульсов и сумматора-вычитателя, при этом управляющие входы указан-, ных инверторов подключены к выходу триггера, входы которого подключены соответственно к шине тактовых импульсов, которая соединена с входами ключа и второго счетчика импульсов, и выходу сумма35 тора-вычитателя, выходы ключа соединены соответственно с входом "Сброс первого счетчика импульсов и входами делителя частоты и первого счетчика им-. пульсов.

4о

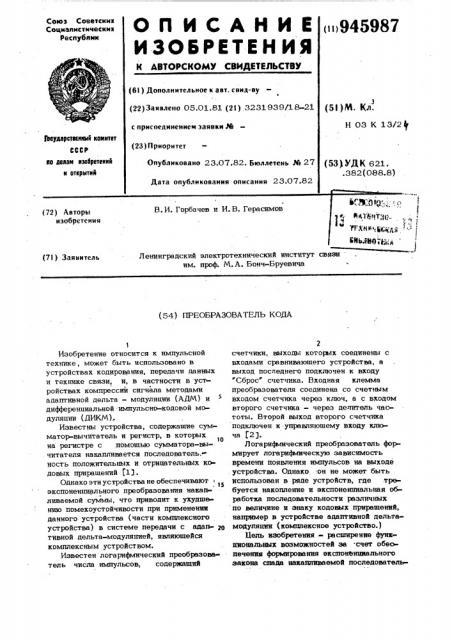

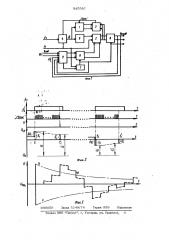

?la фиг. 1 представлена структурная схема преобразователя кода, на фиг. 2 и 3 - временные диаграммы его работы.

Экспоненциальный преобразователь кода содержит суммирующий счетчик 1

45 и вычитающий счетчик 2, поразрядные выходы которых подключены к соответствукщим поразрядным входам сравнивающего устройства 3, а его выход соединен с входом "Сброс" счетчика 1 и запирающим входом ключа 4, на вход которого подан сигнал высокой частоты „, а его выход подключен к входу суммирующего счетчика 1 и через делитель частоты 5к входу вычитающего счетчика 2, поразрядные входы которого соединена с поразрядными выходами управляемого инвертора 6, а управляющий вход инвертора 6 подключен к выходу триггера 7 и управля87 4 юшему входу управляемого инвертора 8, l поразрядные .выходы послед него являются выходами младших разрядов преобразователя и подсоединены также к входам младших разрядов сумматора-вычитателя

9, вход старшего разряда которого подключен к выходу триггера 7, а входом преобразователя являются входы сумматора-вычитателя 9, выходы младших разрядов которого соединены с входами управляемого инвертора 6, а выход старmего разряда подключен к информационно-, му входу триггера 7, на стробируюший ,вход которого, соединенный с открывающим входом ключа 4 и установочным входом вычитающего счетчика 2, подан сигнал тактовой частоты fт.

Устройство работает следующим образом.

На входы 10 сумматора-вычитателя 9 поступают параллельные кодовые приращения с частотой . В каждом такте в зависимости от знака кодового приращения, т. е. "1" или "0 в знаковом разряде, происходит суммирование или вы- . читание его из остатка суммы, подающегося на входы 11 сумматора-вычитателя

9. После суммирования вновь образованная сумма поступает в блок экспоненциальной обработки, состоящий из суммирующего счетчика 1, вычитаюшего счетчика 2, сравнивающего устройства 3, ключа 4, и делителя частоты 5, после чего на вы» ходе устройства образуется новый остаток суммы, обработанной по экспоненциальному закону, причем экспоненциальный спад стремится к некоторому среднему значению 0 .В момент времени 1; кодовое приращение ь0„суммируется с ранее образованным остатком накопленных приращений (фиг. 2). Если новая сумма превы шает пороговый уровень U то высокий потенциал на выходе старшего разряда сумматора-вычитателя 9 фиксируется триггером 7 и выключает управляемый инвертор 6 и выходы младших разрядов, в прямом коде вписываются в вычитающий счетчик 2. Триггер 7 и управляемый инвертор 6 вписывают В вычит&ющий счет» чик 2 абсолютную величину разности

}e„}= }u,.— u«}, rRe ц. - кодовое значение необрабо»1 таиной суммы в момент времени 4-;

U — кодовое значение среднего уровня.

Затем Открывается ключ 4 и импульсы высокой частоты Я суммируются счетчиизобретения

Фо рмула

5 9459 ком 1, а также, пройдя делитель частоты 5, вычитаются из ранее установленной величины(Ф. (в вычитающем счетчике 2.

В момент времени 1 сравнивающее уст1 ройство 3 фиксирует совпадение выходных кодов счетчиков 1 и 2, запирает ключ 4 и устанавливает в исходное состояние суммирующий счетчик 1 . В соответствии с управляющим сигналом триггера 7 инвертор 8 пропускает обработанный код ð младших разрядов суммы на выход устройства в неинвертированном виде, а старший разряд снимается с выхода триггера

7, т. е. на выходе устройства формируется обработанное кодовое значение суммы U

Если в момент времени t отрицатель ное приращение dU-, поступающее на вход

10 сумматора-вычитателя 9, приведет к тому, что новая сумма U>. станет меньше среднего уровня U то низкий потенциал старшего разряда сумматора-вычитателя 9 зафиксируется триггером 7 и вклю- чит управляемые инверторы 6 и 8. Вследствие этого в вычитаюший счетчик 2 впишется обратный код младших разрядов необработанной суммы, что соответствует абсолютной величине разности

)w t=10--о, . зо

Далее через ключ 4 импульсы высокой частоты суммируются счетчиком 1 и через делитель 5 вычитаются из кода, . соответствующего величине (ф.(в счетчике 2. В момент сравнения 4 на вычитаю,з

35 щем счетчике 2, в соответствии с экспоненциальным .законом обработки, будет код jd (, который инвертируется инвертором 8 и поступает на вькод устройства, а также на вход 11 сумматора-вычита40 теля 9 (старший разряд снимается с выхода триггера 8) ° На выходе экспоненциального преобразователя кода в MQMBHT времени образуется код обработанной

1 суммы, соответствующий величине U.

1 (фиг. 2).

Таким образом, на выходе устройства в каждом такте происходит обработка накопленной суммы, которая стремится к среднему значению 9 по экспоненциальному закону.

На фиг. 3 показаны примеры функционирования устройства. Кривая g отоЬражает пример работы при поступлении на вход устройства последовательности различных положительных и отрицатель ных кодовых приращений. Кривые Ъ и с показывают экспоненциальный xapåaòåð изменения амплитуды за несколько тактов

87 6 в случае подачи единовременных положительного или отрицательного приращения соответственно.

Таким образом, предлагаемое устройство обеспечивает формирование экспоненциального спада накапливаемой последовательности различных параллельных кодовых приращений, что делает возможным его использование в устройстве стабилизированной адаптивной дельтамодуляции (комплексном устройстве).

Преобразователь кода, содержащий делитель частоты, первый и второй счет. чики импульсов, сравнивающее устройство и ключ, при этом соответствующие выходы счетчиков импульсов соединены с соответствующими входами сравнивающего устройства, выход которого со динен с входом "Сброс первого счетчика импульсов, выход делителя частоты соединен с соответствующим входом второго счетчика импульсов, вход ключа соединен с входной шиной, о т л и ч а юшийся тем, что, с целью расширения функциональных возможностей, в него введены два управляемых инвертора, триггер и сумматор-вычитатель, причем входы первого и второго управляемых инверторов соединены с выходами соответственно сумматора-вычитателя и второго счетчика импульсов, а выходы первого и второго управляемых инверторов соединены с входами соответственно второго, счетчика импульсов и сумматора-вычитателя, при этом управляющие входы указанных инверторов подключены к выходу триггера, входы которого подключены соответственно к шине тактовых импульсов, которая соединена с входами ключа s второго счетчика импульсов, и выходу сумматора-вычитателя, выходы ключа соединены соответственно с входами Сброс первого счетчика импульсов и входами делителя частоты и первого счетчика импульсов.

Ф

Источники информации, принятые во внимание при экспертизе

1. Букреев И.Н, Мансуров Б.М и др.

Микроэлектронные схемы цифровых устройств, М., Советское радио, 1975, с. 339-341.

2. Авторское свидетельство СССР

hh 470073, an. Н 03 К 13/24, 05.05.75 (прототип).

945987

° ° Ы ° 4 ° ° ее ° ° ° е ° ° °

° ° ° ° ° ° е ° °

° ° ° ° ° ° ° °

;,Орос"

БНИИПИ Заказ 5349/74 Тираж 959 Подписное

Филиап ППП Патент", г. Ужгород, уп. Проектна, 4