Коммутатор

Иллюстрации

Показать всеРеферат

Союз Советсиил

Социалистических

Республии

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ <> 945991 (6I ) Дополнительное к авт. свид-ву

I (22) аявлено 22.01.81 (21) 3240221/1 8-21 (Ы)М. Кл. с присоедмненнем заявки РЙ (23) Приоритет

Н 03 К 17/04

9кударатеелай комитет

СССР ао делам изобретений н открытий (33) УЙК 681.32 (088. 8) Опубликовано 23.07.82. Бюллетень J% 27

Дата опубликования описания 23.07.82

П. В. Друзь, A. И. Савин и Б. В. Солнцев (72) Авторы изобретения

- « !

1 а: (7!) Заявитель. (54) КОММУТАТОР

Изобретение относится к автоматике, и коммутационной технике.

Известны коммутаторы, содержащие элементы И, инвертор, генератор и блок управления (Ц.

К недостаткам известного устройства относится низкое ь|стродействие.

Наиболее близким техническим решением является коммутатор, содержащий первый элемент И, выход которого соединен с первым входом второго элемента

И и через инвертор - с первым входом третьего, элемента И, второй вход которого подключен к выходу генератора и к второму входу второго элемента И, выход которого соединен с входом блока управления f2).

К недостаткам известного устройства относится низкое быстродействие.

Цель изобретения - повышение быстрс фо действия коммутатора.

Указанная цель достигается тем, что в коммутатор,.содержащий первый эле мент И, выход которого соединен с пер2 вым входом второго элемента И и через инвертор — с первым входом третье го элемента И, второй вход которого подключен к выходу генератора и к второму входу второго элемента И, выход которого соединен с входом блока управления, введены дешифратор, сдвиговые регистpbl и шифраторы, входы кажпого иэ которых соединены с соответствующей. группой выходов блока управления, а выходы подключены к информационным входам соо1 ветствующих одноименных разрядов сдвиговых регистров, сдвнговые входы кото рых соединены с выходом третьего элемента И, при этом инверсные выходы последних разрядов сдвиговых регистров подключены к входам первого элемента И, а прямые выходы соединены с входами дешифратора, выходы которого подключены к. выходным шинам.

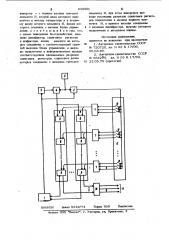

На чертеже представлена функпиональ ная схема предлагаемого коммутатора.

Коммутатор содержит ел@мент И 1, выход которого соединен с первым вхо3 9459 цом элемента И 2 через инвертор 3с первым входом элемента И 4, второй вхоц которого подключен к выходу генератора 5 и к второму входу элемента

И 2, выход которого соединен с входом блока 6 управления; шифраторы 7, входы каждого из которых соединены с соответствующей группой выходов блока 6 управления, а выходы подключены к информационным вхойам соответствуюших ойно-, именных разрядов 8 сдвиговых регистров

9, сйвиговые входы которых соединены с выходом элемента И 4, инверсные выходы последних разрядов 8 сдвиговых регистров 9 подключены к входам элемента И 1, а прямые выходы соединены с входами дешифратора 10, выходы которого подключены к выходным шинам 11, и коммутационные элементы 12.

Коммутатор работает следуюшим образом.

B исходном состоянии сдвиговые регистры обнулены; при этом высокие потенциалы с инверсных выходов последних разрядов 8 открывают элемент И 1, сит нал с выхода которого запирает через инвертор 3 алемент И 4 и пойготавливает к открыванию элемент И 2. С помошью блока 6 управления задается очередность опроса каналов коммутатора.

В блоке 6 управления кажцая группа коммутационных элементов 12 соответствует определенному номеру очередности опроса каналов, а число коммутационных элементов 1 2 в каждой группе соответствует чнспу каналов. Замыканием соответзз ствукщих коммутационных элементов 12 в каждой группе зацается очередность опроса каналов. Сигналы с выхода замкнутых коммутационных элементов 12 воз о бужцают входы соответствующих шифра- . торов 7, которые формируют коцы- номеров выбранных каналов . После включения генератора 5 первый импульс с его выхода через элемент И 2 и замкнутые коммутационные элементы 12 блока 6 управления подается на входы соответствуюших шифраторов 7. На выходах шифраторов 7 формируются коды номеров соответствующих каналов, которые поступают на входы одноименных разрядов 8 сдвиговых регистров 9. Каждая совокупность одноименных разрядов 8 сдвиговых регистров 9 образует регистр, который хранит код номера канала, а размешение этих кодов в разряцах 8 соответствует заданной очередности их опроса. При атом в последних разрядах 8 размещается код номера канала, который опрашивается

91 4 первым, а в первых разрядах 8 - код номера KBBBlIB, который OIIpBIIIIIBBetcsr noc= ледним. Кой канала с единичных выходов последних разрядов 8 декодируется дошифратором 10, на соответствующем выходе которого формируется сигнал, включающий первый данный канал. После записи кода канала в последние раэряцы 8 сигналы с его инверсных выходов не совпадают на входах элемента И 1, который при этом закрывает элемент И 12 и через инвертор 3 открывает элемент И 4.

Следуюший импульс с выхода генератора

5 поступает через алемент И 4 на сцвигаюшие Bxorrbl сдвиговых регистров 9.

В сдвиговых регистрах 9 происходит сйвиг информации, после первого сдвиrB первые разряды 8 обнуляются, а в последних разрядах 8 находится коц номера канала, который опрашивается вторым, Этот код также цекоцируется. йешифратором 10, который задействует следующий канал. При поступлении следуюших импульсов с генератора 5 происходит дальнейший сдвиг информации в сцвиговых регистрах 9 и с помощью цешифратора 10 — опрос каналов в заданной последовательности. После обнуления пооледних разрядов 8 коммутатор возвращается в исходное состояние и описанный выше процесс повторяется, что обеспечивает циклический опрос каналов в зайанной очередности. Для изменения очередности опроса каналов или количества опрашиваемых каналов соответственно изменяется набор на коммутационных элементах 12 в блоке 6 управления. Изменение этого набора может производит ся вручную .оператором или автоматически от внешнего программного устройства.

Таким образом, введение в коммутатор сдвиговых регистров, шифраторов и дешифратора позволяет производить опрос каналов с произвольно задаваемой очередностью, оперативно изменять число опредепяемых каналов и очередность их .опроса в процессе работы коммутатора без изменения схемы соединений коммутатора, что повышает его быстроцействие по сравнению с известным, формула изобретения

Коммутатор, содержащий первый элемент И, выход которого соецинен с первым входом второго элемента И и через

9459

5 инвертор - с первым входом третьего элемента И, второй вход которого подключен к выходу генератора и к второму входу второго элемента И, выход которого соединен с входом блока управ- 5 ленни, о т л и ч а ю ш и и с я тем, что, с целью повышения быстродействия, введены дешифратор, савнговые регистры и шифраторы, входы каждого из которых соединены с соответствуюшей группой выходов блока управления, а выходы подключены к информационным входам соответствуюших одноименных разрядов сдвиговых регистров, савиговые входы которых соединены с выходом третьего 15

91 Ф. элемента И, при этом инверсные выходы последних разрядов сдвиговых регистров подключены к входам первого элемента И, а прямые выходы соеаинены с входами дешифратора, выходы которого подключены к выходным шинам.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

% 720720, кл. Н 03 К 17/00, 05.03. 80.

2. Авторское свидетельство СССР

No 664254, хл, Н 03 К 17/04, 25.05.79 (прототип).

ВНИИПИ Заказ 5349/74 Тираж 959 Подписное

Фипнап ППП Патент, г. Ужгород, уи. Проектная, 4