Статистический анализатор выбросов и провалов напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 23 ° 01 ° 80 (21) 2875243/18-21 (31) М. Кп. З с присоединением заявки №вЂ” (23) Приоритет

G 01 R 19/04

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 30.07.82. Бюллетень ¹ 28

Дата опубликования описания 30.07. 82 (33}УДК 621.317.

° 7 (088. 8) (72) Автор изобретения

ВСЕСОЮЗНАЯ

В. Ф. Ермаков

ИАТЕНТНОтехмнчБскА

Новочеркасский ордена Трудового Красного Эн ни политехнический институт им. Серго Орджоникидэ (71) Заявитель (54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОБ

И ПРОВАЛОВ НАПРЯЖЕНИЯ

Изобретение относится к информационно-измерительной и вычислительной технике и, в частности, может быть использовано в электроэнергетике при аппаратурном контроле качества напряжения в электрических сетях.

Известен многоуровневой анализатор выбросов и провалов напряжения, содержащий пороговые элементы, счет,чики и элементы И и НЕ, причем первый вход каждого i ro (i C n, где n — количество уровней анализа) элемента И, подключенного выходом к входу соответствующего счетчика, соединен с выходом i.-ro порогового элемента, а второй вход подключен через соответствующий элемент HE к выходу (i + 1)-го порогового элемента, выход n-ro порогового элемента соединен с входом и-ого счетчика, соединенного с входной клеммой устройства через дифференциатор порогового элемента, инверсный выход которого через формирователь связан -с третьими входами элементов

И ) 1).

Недостатками устройства являются низкая помехоустойчивость, низкая надежность схемы и двойное время анализа, необходимое для получения гистограмм выбросов и провалов напряжения.

Наиболее близким техническим ре5 шением к предлагаемому является многоуровневый статистический анализатор выбросов и провалов напряжения, содержащий и где п -число уровней анализа) соединенных входами со входной клеммой устройства компараторов, прямые и инверсные выходы которых через и-входовые элементы ИЛИ с динамическими входами соединены соответствен но с вхо-.„ами установки нуля и едини.цы К5-триггера, входы каждого i-го (при 1 «< и) элемента И, подклю.— ченного выходом к входу i-ro m-декадного счетчика импулbcoB соединены соответственно первый — с инверсным выходом i-ro компаратора, второй— с прямым выходом (i-1)-го компаратора, третий — через формирователь одиночного импульса с прямым выходом RS-триггера 52(.

Недостатками известного устройства

25 являются двойное время анализа, необходимое для получения гистограмм выбросов и провалов напряжения, а также его низкая надежность.

ЦеЛь изобретения — повышение быстро30 действия и надежности работы устройства.

947775

Поставленная цель достигается тем, что в статистический анализатор выбросов и провалов напряжения, содержащий и соединенных входами компараторов, прямые и инверсные выходы которых через два п-входовых элемента

ИЛИ с динамическими входами соединены соответственно с входами установки нуля и единицы RS-триггера, выход которого соединен с входом формирователя одиночного импульса, и блок памяти, введены формирователь модуля, нуль-орган и шифратор, причем входная клемма соединена с входами нуль-органа и формирователя модуля, выход которого соединен с входами компарато- 15 ров, прямые входы компараторов, кроме и-го, соединены с входами шифратора, а блок памяти выполнен в виде оперативного запоминающего устройства, m-декадного двоично-десятичного счет- 20 чика и блока задержки, при этом выходы шифратора соединены с младшими разрядами адресных входов оперативного запоминающего устройства, старший разряд которых соединен с внходом нульоргана, выходы оперативного запоминающего устройства соединены с входами предварительной записи m-декадного двоично-десятичного счетчика, выходы последнего соединены с входами записи оперативного запоминающего устройства, выход формирователя одиночного импульса соединен с входом блока задержки, первый выход которого соединен с управляющим входом m-декадного двоично-десятичного счетчика, второй выход — с его счетным входом, а третий выход — с управляющим входом оперативного запоминающего устройства.-

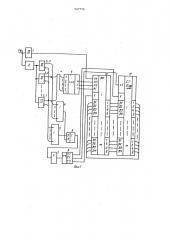

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — графи- 40 ки напряжения на элементах схемы.

Анализатор содержит нуль-орган 1, формирователь 2 модуля, компараторы

3.1-3.3, элементы ИЛИ 4 и 5 с динами ческими входами,RS-триггер б форми 45 рователь 7 одиночного импульса (одновибратор), блок 8 задержки с тремя выходами, шифратор 9 из одноразрядного нормального кода в двоичный, оперативное запоминающее устройство 5р

l0 eMKocTbp3 2 ° n . m 6HT, m-декадный двоично-десятичный счетчик 11 с возможностью предварительной записи информации.

Анализатор выполнен. п êàíàëüíûì, причем опорные уровни компараторов

3.1-3.3 каналов выбраны по равномерному закону с шагом 60. Блок памяти устройства, выполненный на оперативном запоминающем устройстве 10, счет- ®О чика 11 и блока задержки 8, содержит 2и каналов емкостью 10 каждый.

Накопление информации в процессе анализа случайного процесса выбросов и провалов напряжения осуществляется 65 с помощью m-декадного двоично-десятичного счетчика 11, а ее хранение в ячейках оперативного запоминающего устройства 10. Для записи и хранения в оперативном запоминающем устройстве

10m-разрядное десятичное число представляется в виде слова емкостью

m " 4 в коде 1-2-4-8, причем номер декады записанного в оперативном запоминающем устройстве слова соответствует номеру десятичного разряда числа, а значение декады — десятичной цифре этого разряда.

Для изображенного на фиг. 1 в качестве примера анализатора n = 8.

Схема анализатора позволяет производить одновременный параллельный анализ выбросов и провалов напряжения.

Рассмотрим работу устройства при анализе выбросов напряжения. В этом сдучае подаваемое на вход устройства отклонение напряжения сети от его номинального уровня повторяется форми -t рователем 2 модуля без изменений и подается на входы компараторов 3.1-3.3. (фиг . 2, a)

U1=0åÔ=V=0-0Н

В процессе. своего йзменения напряжениа U „пересекает нулевое значение (в момент времени t ), что приводит к срабатыванию нуль-органа 1, выходное единичное напряжение которого прикладывается к адресному входу оперативного запоминающего устройства 10.

В момент времени t напряжение U пересекает уровень 00 „, что сопровождается срабатыванием компаратора первого канала 3.1 и появлением на выходе элемента ИЛИ 4 единичного им пульса (фиг. 2, Д ). Этот импульс переводит RS-триггер б в нулевое состо.яние.

Даль нейший рост напряжений 09„ (и, соответственно, 0 ) сопровождается поочередными срабатываниями компаратора .второго и третьего каналов.

Поступающие при этом на вход R RSтриггера б единичные импульсыГне меняют состояние RS-триггера, а лишь повышают надежность работы устройства в целом. При срабатывании каждого компаратора, кроме того, формируется новый адрес на входах А1-АЗ оперативного запоминающего устройства 10, однако это также не приводит к какимлибо изменениям в схеме анализатора.

После прохождения выбросом напряжения своего амплитудного значения напряжение 0 начинает снижаться, .что в момент времени t приводит к возврату компаратора третьего канала 3.3 и появлению единичного напряжения на его инверсном выходе. При этом с выхода элемента ИЛИ 5 на вход

S RS-триггера б поступает чмпульс

947775

6 напряжения (фиг. 2, в), который переводит RS-триггер в единичное состояние. A зто, в свою очередь, приводит к запуску формирователя 7 одиночного импульса, выходное напряжение которого прикладывается к входу блока 8 задержки.

После возврата компаратора 3.3, кроме того, формируется соответствующий,третьему каналу блока памяти выбросов напряжения адрес на входах l0

А1-А4 оперативного запоминающего устройства 10 — 1010.

Появляющийся на выходе блока задержки 8 с задержкой Г импульс на,пряжения (фиг. 2, г) подает команду 15 на.предварительную запись в m-декадный двоично-десятичный счетчик 11 числа, накопленного в результате предыдущего анализа в канале устройства с адресом 1010 и поданного с выходов оперативного запоминающего устройства 10 на информационные входы счетчика 11, После окончания предварительной записи с задержкой Т на выходе блока

8 задержки, связанном со счетным входом декадного двоично-десятичного счетчика 11, появляется импульс, увеличивающий содержимое счетчика на еди-. ницу.

30 с задержкой Гз с выхода блока 8 задержки подается команда на запись в оперативное запоминающее устройство

10 по тому же адресу 1010, увеличенному на единицу числа.

Таким образом осуществляется накоп 5 ление информации в блоке памяти устройства.

При появлении провала напряжения нуль-орган 1 возвращается в исходное состояние и его выходное напряжение 40 принимает нулевое значение, а формирователь 2 модуля инвертирует входное напряжение устройства

u2 - =-v = -v = - (u-u„)

ЬХ

В остальном работа анализатора 45 при провалах напряжения аналогична описанной выше. Только накопление информации осуществляется в оперативном запоминающем устройстве 10 по адресам 0000 — 0111.. 50

После накопления достаточного объема информации по содержимому оперативного запоминающего устройства 10 строятся гистограммы выбросов и провалов напряжения. Максимальное число разрядов гистограмм равно и, т.е. п9ловине записанных в оперативном запоминающем устройстве 10 числа слов, а величина выборки выбросов и провалов напряжения ограничена числом десятичных разрядов m счетчика 11 °

Преимуществами предлагаемого устройства по сравнению с известными является меньшее в 2 раза время анализа, необходимое для получения гистограмм выбросов и провалов напряжения, большая экономичность и надежность схемы, меньшая стоимость и потребляемая его мощность.

Формула изобретения

Статистический анализатор выбросов и провалов напряжения, содержащий п соединенных. входами компараторов, прямые и инверсные выходы которых через два и-входовых элемента

ИЛИ с динамическими входами соединены соответственно с входами установки нуля и единицы RS-триггера, выход которого соединен с входом формирователя одиночного импульса, и блок памяти, отличающийся тем, что, с целью повышения быстродействия и надежности работы, в него введены формирователь модуля, нуль-орган и шифратор, причем входная клемма соединена с входами нуль-органа и формирователя модуля, выход которого соединен с входами компараторов, прямые выходы компараторов, кроме п-го, соединены с входами шифратора, а блок памяти выполнен в виде оперативного запоминающего устройства, m-декадного двоично-десятичного счетчика и блока задержки, при этом выходы шифратора соединены с младшими разрядами адресных входов оперативного запоминающего устройства, старший разряд которых соединен с .выходом нуль-органа, выходы оперативного запоминающего устройства соединены с входами предварительной записи m-декадного двоичнодесятичного счетчика, выходы последнего соединены с входами записи оперативного запоминающего устройства, выход формирователя одиночного импульса соединен с входом бюйжа задержки, первый выход которого соединен с управ. ляющим входом m-декадного вдоично-деоятичного счетчика, второй выходс егo счетным входом, а третий выхг с управляющим входом оперативного запоминающего устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ю 591781, кл. G 01 R 19/04, 1976.

2. Авторское свидетельство СССР

Ф 789880i кл. G 01 R 19/04, 1979.

Составитель В. Костин

Редактор Н. Гришанова Техред A. БабииеЦ Корректор У. Пономаренко

Заказ 5624/68 Тираж 717 Поднисное

ЗНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ППП "Патент", г. Ужгород, Ул. Проектная, 4