Устройство для контроля функционирования интегральных схем памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рескублик о«947789 (6t) Дополнительное к авт. свид-ву(22) Заявлено 21.0378 (21) 2592831/18-25 с присоединением заявки ¹f51) M Кл з

G R 31/26

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (53) УДК 621. 382..2(088.8) Опубликовано 3007.82. Бюллетень ¹ 28

Дата опубликования описания 30.07,82

1

A.È. Панов, В.Ф. Ворожеев и Б.П.Лучин Л П К:: МЕь ° - . Ф ч. са (.: . " ° с

5t.. ., .,: .:,ф, 1.:;. (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФУНКЦИОНИРОВАНИЯ

ИНТЕГРАЛЬНЫХ СХЕМ ПА?4ЯТИ

Изобретение относится к электронной промышленности и может быть . использовано для функционального контроля интегральных схем с высоким уровнем интеграции, в частности больших интегральных схем оперативных запоминающих устройств (БИС ОЗУ), а также для их испытаний при массовом производстве, когда необходимо производить контроль функционирования большого числа однотипных схем, проходящих испытания под электрической нагрузкой.

Известны устройства для контроля функционирования интегральных схем, осуществляющие проверку по принципу "годен-брак". В них формируется определенная кодовая информация - программа -проверки, которая передается на испытуемую схему, а поступающая с функционирующей схемы информация сравнивается с ожидаемой, содержащейся в программе проверки. Совпадение поступающей информации с ожидаемой характеризует работоспособность испытуемой схемы на заданной рабочей частоте, т.е. способ-. кость выполнять на этой частоте заданные логические операции(13 Г23 к (32 °

Укаэанные устройства универсальны, могут осуществлять проверку функционирования различных логических

БИС, но имеют низкую производительность, так как с их помощью одновременно можно осуществлять проверку только>одной БИС ОЗУ.

Наиболее близким техническим решением к предлагаемому является устройство, которое содержит подключающее устройство для включения испытуемой схемы, блок задания входных воздействий, компаратор данных, соединенный по входам с блоком задания ожидаемой информации, подключающим устройством и блоком управления, который подключен к блоку задания ожидаемой информации и к ЭВИ(4).

Недостатком известного устройства также является низкая производительность контроля функционирования схем, особенно медленно работающих .БИС ОЗУ с высокой информационной емкостью. Например, для ОЗУ емкостью 4096 бит продолжительность проверки одной схемы на частоте

1 МГц в заВисиМости от алгоритма проверки, определякщего достоверность контроля, составляет от 34 с

947789 до 17 ч. При массовом контроле такие затраты времени недопустимы.

Цель изобретения - обеспечение . возможностИ одновременного контроля и схем памяти и повышение тем самым производительности устройства. 5

Поставленная цель Достигается тем, что в устройство дополнительно введены и-1 подключающих устройств, и буферных каскадов, и-1 компараторов данных и и регистров памяти результатов 10 контроля, причем подключающие устройства через буферные каскады соединены с выходом блока задания- входных воздействий, а также с входами компараторов данных, которые вторыми парал 5

1 ельно соединенными входами подклюены к выходу блока задания ожидаемой информации, третьими, также параллельно соединенными входами - к выходу блока управления, а выходами соединены через регистры памяти результатов контроля с соответствующими входами блока управления.

Такое устройство позволяет осуществлять проверку функционирования одновременно и БИС ОЗУ вместо одной, увеличивая производительность оборудования в и раз.

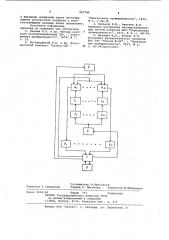

На чертеже представлена блок-схема предлагаемого устройства для контроля функционирования интегральных схем памяти.

Устройство содержит подключающие. устройства 1, ...1 для подключения и контролируемых схем, буферные каскады 2„ ...,2п, предназначенные для 35 усиления согласования и развязки входных сигналов с блока 3 задания входных воздействий, компараторы 4« ...,4п данных (по количеству контролируемых схем), блок 5 задания ожи-40 даемой информации, регистры бл,...,б

1памяти результатов контроля, служащие для хранения информации о результатах проверки каждой схемы, блок 7 управления и ЭВМ 8. На чертеже для простоты понимания предлагаемого решения не показаны режимные источники питания, коммутаторы выводов испытуемых БИС, устройства согласования уровней (БИС вЂ” транслято50 ры сигналов), блок формирования рабочей частоты и строб-импульсов, блок фОрмирования адресных сигналов.

Устройство работает следующим образом.

Контролируе,е БИС ОЗУ помещаются 55 в подключающие устройства 1„, ...,1, Из ЭВМ 8 через блок 7 управления в и блок 3 задания входных воздействий и блок 5 ожидаемой информации заносятся данные, необходимые для выпол- Ю нения программы контроля в зависимости от типа контролируемой БИС и выбранного алгоритма. После ввода программы контроля из ЭВМ 8 коды информационных частей команд преоб- 65 разуются в необходимые аналоговые сигналы. По команде ЭВМ "Начало контроля" формируется адрес начальных ячеек контроля БИС, в память которых с блока 3 задания входных воздействий параллельно через буферные каскады 2, ...,2 заносится требуемая контрольная последовательность сигналов. Занесенная в ячейки памяти БИС контрольная последовательность сигналов подается на один из входов компараторов 4.,„...,4,„ данныхна вторые входй которых параллельно подается контрольная последовательность сигналов ожидаемой информации с блока 5 задания ожидаемой информации.компараторы 4„,...,4z данных сравнивая входную и ожидаемую информацию, формируют сигналы результаты сравнения, которые записываются в регистры 6,...,6 памяти результата контроля. Пройдя, таким образом, последовательно все ячейки памяти контролируемых БИС, регистры памяти результата контроля получают и хранят полную информацию о результатах проверки. По окончании контроля полученная информация через блок

7 управления последовательно с каждого регистра считывается в ЭВМ 8.

В данном устройстве по сравнению с известным благодаря введению новых элементов, которые привели к небольшому его усложнению, существенно пОвышена производйтельность основного дорогостоящего оборудования и эффективность его использования.

Формула изобретения

Устройство для контроля функционирования интегральных схем памяти, содержащее подключающее устройство для включения испытуемой схемы, блок задания входных воздействий, компаратор данных,.соединенный по входам с блоком задания ожидаемой информации, подключающим устройством и блоком управления, который подключен к блоку задания ожидаемой информации и к ЭВМ, о т л и ч а ю щ е е с я тем, что, с целью обеспечения возможности одновременного контроля и схем памяти и повышения производительности, в него дополнительно введены и-1 подключающих устройств, и буферных каскадов, и-1 компараторов данных и и регистров памяти результатов контроля, причем подключающие устройства через буферные каскады соединены с выходом блока эадания входных воздействий, а также с входами компараторов данных, которые вторыми параллельно соединенными входами подключены к выходу блока задания ожидаемой информации, третьими, также параллельно соединенными входами — к выходу блока управления, 947789

Составитель Ю.Брызгалов

Техред С. Мигунова Корректор Ю.Макаренко

Редактор Н.Гришанова

Заказ 5645/69 Тираж 717 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 а выходами соединены через регистры памяти результатов контроля с соответствуюшими входами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Валиев В.Х. и др. Методы контроля полупроводниковых ОЗУ. - Электронная,промышленность", 1974, Р 7, с. 12.

2. Богородицкий Л.A. и др. Многопостовой комплекс "Элекон-СД" 10

"Электронная промышленность", 1975, 9 i, с.24-35.

3. Вальков В.М., Ажаткин Д.И.

Принципы построения автоматизированных систем контроля БИС-"Электронная промышленность", 1973, 9 2, с. 68-74.

4. Данилин Н,Н., Попель Л.М.

Установка функционального контроля

БИС ОЗУ "Элекон Ф-ЗУ", — "Электронная промышленность", 1977, 9 2, с. 20-24(прототип).