Преобразователь кода из системы остаточных классов в двоичный код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик р >947850

1 Ъ:@ Лт а.=-

Д

-"я (61) Дополнительное к авт, свид-ву— (22) Заявлено 081280 (21) 3213074/18-24 (511 М. Кп.

G 06 F 5/02 с присоединением заявки №вЂ” (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325. .53(088.8) Опубликовано 300782. Бюллетень ¹ 28

Дата опубликования описания 300782 (.ру nyq (72) Автор изобретения

А.А.Коляда .4". 1.(п 10

: т :

Р .+ :"., gc

Научно-исследовательский институт прикладных физических проблем им.А.М.Севченко при Белорусском орде а ТДЩЙЙ6з- - :

Красного Знамени государственном университет им. В.И.Ленина (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОДА ИЗ СИСТЕМЫ

ОСТАТОЧНЫХ КЛАССОВ В ДВОИЧНЫЙ

КОД

Изобретение относится к вычислительной технике и может быть исполь-. зовано в цифровых вычислительных устройствах, работающих в непоэиционных системах счисления для перевода чисел, представленных в ранговом расширении систем остаточных классов в двоичный код.

Известен преобразователь кода числа из системы счисления остаточных классов в позиционный код, содержащий блок модульных накапливающих сумматоров, блок для контроля обнуления, управляющий блок, позиционный сумматор, входные и выходные шины, соединенные соответствующими связями (1J .

Недостатком устройства является невысокое быстродействие.

Наиболее близким к данному изобретению техническим решением является преобразователь кода из системы остаточных классов в полиадический код, содержащий входной и выходной регистры, пирамиду сумматоров, устройство для хранения констант по каждому модулю, формирователи переносов, элементы И, элемент ИЛИ, а также анализатор модульной суммы, сумматоры в пирамиде объединены в группы по каждому модулю и параллельно-последовательно соединены между собой, причем входы пирамиды сумма-. торов соединены с соответствующими выходами устройства для хранения констант по каждому модулю, входы которого соединены с выходами ,входного регистра, а каждый из формироватепей переносов соединен по входам с сумматорами данной группы, а по выходу — с последним сумматором последующей группы, причем выход пред последнего сумматора группы сумматоров по последнему модулю соединен с входом анализатора величины модульной суммы, выходы которого соединены через элементы И с входом элемента

ИЛИ $2J .

Недостаток устройства — большой объем оборудования.

Цель изобретения †уменьшение объема оборудования.

Поставленная цель достигается тем, что преобразователь кода из системы остаточных классов в двоичный код, содержащий входной регистр, входы которого являются информационными входами преобразователя, группу из и блоков хранения констант, группу из п+1 сумматоров по модулю

947850 р (n — количество оснований систеьм, р; - основание системы), сумматор по модулю р„+ и сумматор по модулю р»»+, содержит регистр интервального индекса, вход которого является индексным входом преобразователя, сдвиговый регистр, выходы которого являются выходами двоичного кода преобразователя, первый, второй и третий блоки хранения констант интервального индекса, первые входы первых и сумматоров группы объедине10 ны с первьа и входами соответствующих и блоков хранения констант группы и подключены к соответствующим выходам входного. регистра, пеРвый вход (n+1)-15

ro сумматора группы объединен с первым входом первого блока хранения констант интервального индекса и подключен к выходу регистра интервальноro индекса, вторые входы n+1-го сум 20 маторов группы объединены и подключены к выходу сумматора по модулю р„. и к входу сдвигового регистра, первые входу первого блока хранения констант35 интервального индекса, первый выход которого подключен к первому входу второго блока хранения констант интервального индекса, а второй — к (n+2)-му входу сумматора по модулю первый выход которого подключен

»»»»к к второму входу второго блока хранения констант интервального индекса, а второй - к первому входу третьего блока хранения констант интервально40

45 го индекса, второй вход которого подключен к первому входу первого блока хранения констант интервального индекса, а выход подключен к (и+1)-му входу сумматора по модулю р„, .

Упрощение преобразователя достигается за счет использования кодов

50 рангового расширения системы остаточных классов.

В основу работы преобразователя положено следующее.

Пусть требуется преобразовать в двоичную систему счисления целое число А, представленное в виде

А = О,„й у,... ° Й»»р IA, где 0 .; =)Ар; !р, .

i-ая цифра нормированного кода в остатках числа !А!р,, а IA — интервальный индекс числа А,определяемый так, чтобы

»»

А Е ос р. + 1 Р. (1) »»»» Л бО входы первых и сумматоров группы подключены к соответствующим входам входного регистра, а вторые - к вторым входам блоков хранения констант, первые выходы которых подключены к соответствующим Tl входам сумматора по модулю рд+„, а вторые — к соответствующим и входам сумматора по моду- ЗО лю р„,<,(п+1)-ый вход сумматора по модулю р„,» подключен к первому выходу (и+1)-ro сумматора группы, второй выход которого подключен к второму

Р»-

Р„, если i

»»w Q

°,яй сумматор формирует

n+1 то (п+1) величину и

Здесь Р =.П„р„,р„., р ...,р„-основ- .ные модулй ран го во го р асшире ни я системы остаточных классов; через ! Ajp; обозначается наименьший неотрицательный вычет по модулю р;, сравнимый с Х.

Индекс IA числа А должен удовлетворять условию

-q Я )А)р+ ГА (q, (2) где »IA) — нормированный ранг числа к !

А!, à q = 2 (K — фиксированное натуральное число) .

В соответствии с определением нормированного ранга числа можно записать

А. = !А!р + (1!А! Р + 1л)Р.

Учитывая (2), заключаем, что диапазон рангового расширения системы остаточных классов, а следовательно, и множество чисел, которые могут быть приведены из рассматриваемых систем в двоичный код с помощью предлагаемого устройства, представляет собой интервал P-qP, q Р)

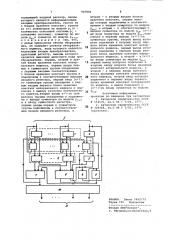

На чертеже представлена блок-схема устройства.

Схема включает входной регистр 1, группу 2 из п блоков хранения констант, группу 3 из п+1 сумматоров по модулю р„, регистр 4 интервального индекса, первый блок 5 хранения констант интервального индекса, сумматоры б и 7 по модулю р„„и р, второй и третий блоки 8 и 9 хранения констант интервального индекса, сдвиговый регистр 10.

Входной регистр предназначен для хранения остатков числа по каждому из оснований системы и состоит из и подрегистров.

Группа 2 блоков хранения констант представляет собой совокупность из и постоянных запоминающих блоков, адресом которых являются остатки по соответствующим основаниям системы, а выходом преобразованные остатки в соответствии с формулами j р;о ;)Р„,,и(-к;/ „!Р„„, Группа сумматоров 3 выполняет функции вычитателей по основаниям системы р„ и р„„ с весом „. Если

i = 1,2,...,n, то 1-ый сумматор формирует величину!(Р;-»»,Р )/Рв, р; если i = п+1, то (и+1) -ый сумматор формирует величину !(Р x;)/! / p»» à! p„»

Первый блок 5 храненйя констант интервального индекса представляет собой таблицу дополнительного кода интервального индекса, на выходе которой формируется величина (-1! Р>« с весом (3; . Если i = 1,2,...,n то i-ый сумматор формирует величину

947850

-и- -и- -(р„„ . Второй и третий блоки

1 п»2 хранения констант интервального индекса также представляют собой таблицы, которые по входной информации, определяемой величиной I„ формируют на выходах величины -1Р)Р„,»и(1Р Рп+г.

Устройство работает следующим образом.

Процесс перевода числа A E(-QP,g P) в двоичный код состоит иэ двух этапов, на первом иэ которых число А, поступающее в регистр 1, расширяется на дополнительные модули рангового расширения системы остаточных клас ((p»,»и p„2 где рп г q а р > 1с), причем модули р, р ..., р

n+» » попарно взаимно просты.

С точки зрения экономии оборудования расчетные формулы для.вычислеНИЯ ОСтатКОВ ЖП»» =- Aj P„ZOCn»гте P„ записываются в виде

Ы.„,„* -Р : )- —" lP» )-1„ Р„,„ Р„,„1Р„„, Р) и п»2 » l » +4Рп(2 д Р Рп+2 Рп»2, (4)

Реализация устройством формул (3) и (4) осуществляется следующим образом.

Цифра a(„(i = 1,2,...,n) числа А через выход i-го подрегистра входного регистра 1 подается на вход 1-Fo блока группы 2, на выходах которого формируются вычеты Lp;

Сумматоры б и 7 производят суммирование согласно формул (3) и (4).

Для окончательного формирования вычетаосп,„ результат суммирования в блоке 6 с второго выхода поступает на вход блока 8 для умножения на — Р по модулю рп,„ . Искомое значение oc„,» с выхода блока 8 передается на вход регистра 4 интервального индекса.

Вычет oc„»2, пРедставляющий собой

К младших двоичных разрядов позиционного кода числа А, с выхода блока

7 поступает в К старших разрядов сдвигового регистра 10, разрядность которого составляет mK бит, где

m =) ((через L

К обозначается наименьшее целое число, не меньшее Х).

Второй этап процедуры перевода числа А в двоичный код состоит иэ

m-1 одинаковых шагов, íà j-oM из которых (j = 1,2,..., m-1) преобразователь выполняет следующее действие.

Содержимое сдвигового регистра 10 сдвигается на бит вправо, а содержимое входного регистра 1, представляющее собой вектор вычетов (о »(г ") ...,с (п () о(.(„, »)) полученный на прео(.,,"»те п»»), через выходы своих подрегистров подается на первые входы сумматоров группы 3, на вторые входы которых с выхода блока 7 поступает х ) 2 (х ;, г = к п.г ). В Результате i-ый сумматор группы 3 (i= 1,2,...,n) определяет величину

-()Ь. С„(" - Р."o(,(> "

Р à (n+1)-ый сум15 ()-1) ((») матор — величину " " " ) р

° п»2 которая через первый вйход передается на (n+1) ый вход блока 5.

Дополнительный код по модулю р„, найденной величины с первого выхода блока 5 поступает на первый вход блока 8, где окончательно формируется величинам.„», по формуле (()-») ()-»)

25 ()) и пр» — с4 п»2 которая с выхода блока 8 передается в регистр 4 интервального индекса.

З0 Вычет (й.",) через первый выход i-го сумматора группы 3 (i = 1,2,...,n) пересылается в i-ый подрегистр регистра 1, а через второй выход подается на вход i-ro блока группы 2.

35 В результате блоки 2,7 и 6 определяют величины

B (K Р(а )Р и ()) (j1

"+" „ р Рп+»1 Рп»»

Вычет r формируется на втором

45 выходе блока 6, откуда поступает на вход блока 9 для определения величины 1п,/Р) Р п,, котоРаЯ с выхода блока 9 передается на (и+1)-ый вход сумматора 7. В результате на выходе

gp сумматора 7 формируется вычет oC, =

= p;+l(; Р р,! Ä, двоичное представление которого совпадает с очередными м гадшими двоичными разрядами допол)(итель" ного кода числа А по модулю 2q

Таким образом, введение в состав устройства регистра интервального индекса, сдвигового регистра и трех блоков хранения констант интервального индекса позволяет при сохранении достаточно высокого быстродейстбО вия сократить объем оборудования преобразователя. .Формула изобретения

Преобразователь кода из система

65 остаточных классов в двоичный код, s

947850 содержащий входной регистр, входы которого являются информационными входами преобразователя, группу из и блоков хранения констант, группу из п+1 сумматоров по модулю p„(n количество оснований системы,p основание системы), сумматор по модулю р„,,и сумматор по модулю р„ о т л и ч а ю шийся тем, что, с целью уменьшения объема оборудования, он содержит регистр интервального индекса, вход которого является индексным входом преобразователя, сдвиговый регистр, выходы которого являются выходами двоичного кода преобразователя, первый, второй и третий блоки хранения констант интервального индекса, первые входы первых и сумматоров группы объединены с первыми входами соответствующих и блоков хранения констант группы и подключены к соответствующим выходам входного регистра, первый вход (n+1)— го сумматора группы объединен с первым входом первого блока хранения констант интервального индекса и подключен к выходу регистра интервального индекса, вторые входы n+1-го сумматоров группы объединены и подключены к выходу сумматора по модулю р„, и к входу сдвигового регистра, первые входы первых и сумматоров группы подключены к соответствующим входам входного регистра, а вторые — к вторым входам блоков хранения констант, первые выходы которых подключены к соответствующим и входам сумматора по модулю р„,», а вторые — к соответствующим П входам сумматора по модулю р < (n+1)ый вход сумматора по модулю р„,„ подключен к первому выходу (n+I)-ro сумматора группы, второй выход которого подключен к второму входу первого блока хранения констант интервального индекса, первый выход которого подключен к первому входу второго блока хранения констант интер-. вального индекса, а второй — к (n+Z)му входу сумматора по модулю р„,„, 5 .первый выход которого подключен к второму входу второго блока хранения констант интервального индекса, а второй — к первому входу третьего блока хранения констант интерваль 2О ного индекса, второй вход которого подключен к первому входу первого блока хранения констант интервального индекса, а выход подключен к (n+1)-му входу сумматора по модулю

25 . Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 554536, кл.G 06 Г 5/02, 1977.

2. Авторское свидетельство СССР

Р 328448, кл.G 06 F 5/02, 1970 (прототип).

ВНИИПИ Заказ 5652/72

Тираж 731 Подписное

Филиал ППП"Патент", r, Ужгород,ул.Проектная,4