Устройство для вычисления функции @

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< >947855 ь .

//= — —. а.=-" ьь, г.. ,«

«г .«. .«:: (61) Дополнительное к авт. свид-ву (22) Заявлено 03. 09. 79 (21) 2815365/18-24 с присоединением заявки М—

f$g) Кп з

G 06 F 7/552 (23) Приоритет—

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 300782. Бюллетень М 28

Дата опубликования описания 30.07.82

{ЗЗ) УДК 681. 325 (088.8) (72) Авторы изобретения

А.К.Беляев, Г.И.Корниенко и В.В.Ткаченк

1, Ордена Ленина институт кибернетики AH Ук

ВСЕ,: N .»

1

1:,Л!Г» " ;3

;« ь ) аинской ССР, 1 йь Ф (71) Заявитель и (54) УСТРОИСТВО ДЛЯ ВЫНИСЛВНИЯ ФУНКЦИИ,Z.« л «

Изобретение относится к цифровой вычислительной технике и может быть использовано для вычисления функции к а также для получения квадратичных характеристик числовых последовательностей, необходимых при статистической обработке данных.

Известно цифровое устройство для решения уравнений вида z = x + у, 2 содержащее регистр, блок управления, элементы И (1J .

Недостатком его является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления функции и 2 вида у (и ) = (д ) ° содержащее . ре— гистр числа, блок управления, блоки коммутации, сумматор, регистры результата промежуточного результата, суммы (2J .

Недостатком .известного устройства является невысокое быстродействие.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в устройство для вычисления х функции вида Z, содержащее регистр исходного числа, выходом подключенный к входу регистра коммутации, выход которого соединен с входом регистра преобразования, блок управления,введены триггер управления инвертированием, элементы И, ИЛИ, сумматор по модулю два, элемент запрета, причем i-й разряд регистра (i = 1-:x) преобразования содержит триггер, сумматор по модулю два, элементы И, ИЛИ, при этом выход триггера соединен с первым входом первого элемента И, второй вход которого подключен к выходу сумматора по модулю два и первому входу второго элемента И, а выход — к входу элемента ИЛИ, второй вход которого подключен к выходу элемента ИЛИ (i-1)-го разряда регистра преОбразования и первому входу сумматора по модулю два, второй вход которого и второй вход третьего элемента И соединены с выходом элемента И i-го разряда регистра коммутации, второй вход второго элемента И

i-ro разряда регистра преобразования соединен с выходом первого управляющего элемента И устройства и со счетным входом триггера i-го разряда регистра исходного числа, выход второго элемента И i-го разряда ре947855 гистра преобразования соединен со счетным входом триггера i-го разряда регистра преобразования в i-м разряде регистра коммутации, выход элемента запрета соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ (i-1)ro разряда регистра коммутации, первый вход элемента И i-ro разряда регистра коммутации соединен с выходом триггера i го разряда регистра ком- 1О мутации, подключенного к первому входу блока управления, и с входом элемента запрета (i-1)-го разряда регистра коммутации, второй вход элемента И i-го разряда регистра коммутации соединен с выходом триггера

i-ro разряда регистра исходного числа, выход элемента ИЛИ и-ro разряда регистра коммутации соединен с вторым входом блока управления и с первым входом второго управляющего элемента И, второй вход которого соединен с первым выходом блока управления, а выход — с входом триггера управления инвертированием, выход которого подключен к первому входу первого управляющего элемента И, второй вход которого подключен к второму выходу блока управления устройства.

Кроме того, блок управления содержит элементы И, ИЛИ, триггер, генератор импульсов, причем выход генератора импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом 35 элемента ИЛИ, входы которого соединены с первым входом блока управления, выход первого элемента И подключен к первым входам второго и третьего элементов И и к счетному 4р входу триггера, вход которого подключен к второму входу блока управления, прямой и инверсный выходы триггера соединены с вторыми входами соответственно второго и третьего 45 элементов И, выходы которых являются соответственно вторым и первым выходами блока.

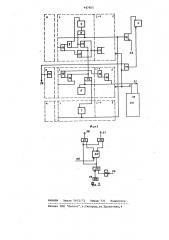

На фиг.1 представлена схема вычисления функции; на фиг.2 — вариант выполнения блока управления.

Схема (фиг.1) содержит регистр 1 преобразователя, регистр 2 коммутации, регистр 3 исходного числа, триггер 4 управления инвертированием, триггеры 5-7, элементы И 8-10, элементы ИЛИ 11, сумматор 12 по модулю два, элемент И 13, элементы 14 запрета, элементы ИЛИ 15, управляющие элементы И 16 и 17; блок 18 управления (фиг.2) содержит генератор 19 импуль- О сов, триггер 20, элементы И 21-23, элемент ИЛИ 24, входы 25 и 26, выходы 27 и 28.

Устройство работает следующим образом. 65

В исходном состоянии содержимое триггера управления "0", в регистре

1 — нули, в регистре 2 — единицы, а в регистре 3 — исходное число. По тому на выходе элемента И 15 и -го разряда регистра 2 состояние и -го разряда регистра 3 и все разряды исходного числа подключены к регистру 1. В первом цикле работы устройства из устройства управления на выход 27 выдается сигнал сдвига. По этому сигналу происходит правый сдвиг содержимого регистра 2, при этом состояние регистра преобразуется к виду 0111...1, и левый сдвиг содержимого регистра 1. В регистре 1 остаются нули, а в триггер управления инвертированием переписывается содержимое и-ro разряда регистра 3 исходного кода. В результате правого сдвига содержимого регистра 2 происходит отключение переменной и-ro разряда от соответствующего входа регистра 1.

На выходе элемента ИЛИ 15 п-го разряда регистра 2 появляется переменная п-1 разряда регистра 3. В регистре 1 происходит срабатывание комбинационной логики и на соответствующих входах элементов H 8 формируются условия инвертирования разрядов этого регистра. Затем устройство управления на выход 28 инвертирования выдает сигнал инвертирования и в зависимости от состояния триггера 4 управления и условий инвертирования в раз— рядах происходит инвертирование содержимых разрядов регистра 1 и разрядов регистра 3. В следующем цикле работы устройства путем подачи сигнала на выход 27 сдвига осуществляется сдвиг содержимого регистра 1 влево, а регистра 2 вправо на один разряд.

При этом в регистр 1 сдвигается прежнее содержимое триггера 4 управления, в который записывается новое содержимое, состояние п-1 переменной регистра 3. В регистре 2 образуется код 00111...1. Таким образом, происходит отключение и и и-1 переменных от соответствующих входов регистра 1, а на выходе элемента ИЛИ 15 и-го разряда регистра 2 формируется значение п-2 переменной регистра 3, которое в следующем цикле переписывается в триггер 4 управления. После подачи сигнала сдвига устройство управления выдает сигнал инвертирования на вход

28 и происходит инверсия в соответствующих разрядах. Таким образом, в результате И циклов работы устройства в регистре 1 формируется резульх тат вычисления, (с f

Предлагаемое устройство является более быстродействующим имеет меньшее количество аппаратуры по сравнению с извесТными схемами.

947855

Формула изобретения

1. Устройство для вычисления функции с ., содержащее регистр исходного числа, выходом подключенный к входу регистра коммутации, выход которого соединен с входом регистра преобразования, блок управления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и 10 сокращения аппаратуры, в него введены триггер управления инвертированием, элементы И, ИЛИ, сумматор по модулю два, элемент заПрета, причем

i-й разряд регистра (i = 1 †: x) npe15 образования содержит триггер, сумматор по модулю два, элементы И, ИЛИ, при этом выход триггера соединен с первым входом первого элемента И, второй вход которого подключен к вы- 20 ходу сумматора по модулю два и перному входу второго элемента И, а выход — к входу элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход кото- 25 рого подключен к выходу элемента ИЛИ (i-1)-ro разряда регистра преобразования и первому входу сумматора по модулю два, второй вход которого и второй вход третьего элемента И сое- 3О динены с выходом элемента И i-ro разряда регистра коммутации и с прямым входом элемента запрета i.-го разряда регистра коммутации, второй вход второго элемента И i-го разряда регистра преобразования соединен с выходом первого управляющего элемента И устройства и со счетным входом триггера i-ro разряда регистра исходного числа, выход второго элемента И i-го„ разряда регистра преобразования соединен со счетным входом триггера

i-ro разряда регистра преобразования в i-м разряде регистра коммутации, выход элемента запрета соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ (i-1)-го разряда регистра коммутации, первый вход элемента И

i-го разряда регистра коммутации соединен с выходом триггера i-го разряда регистра коммутации, подключенного к первому входу блока управления, и с входом элемента запрета (i-1)-го разряда регистра коммутации, второй вход элемента И i-ro разряда регистра коммутации соединен с выходом триггера i-го разряда регистра исходного числа, выход элемента ИЛИ

n-ro разряда регистра коммутации соединен с вторым входом блока управления и с первым входом второго управляющего элемента И, второй вход которого соединен с первым выходом блока управления, а выход — с входом триггера управления инвертированием, выход которого подключен к первому входу первого управляющего элемента И, второй вход которого подключен к второму выходу блока управления устройства.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок управления содержит элементы И, ИЛИ, триггер, генератор импульсов, причем выход генератора импульсов соединен с пеовым входом первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, входы которого соединены с первым входом блока управления, выход первого элемента И подключен к первым входам второго и третьего элементов И и к счетному входу триггера, вход которого подключен к второму входу блока управления, прямой и инверсный выходы триггера соединены с вторыми входами соответственно второго и третьего элементов И, выходы которых являются соответственно вторым и первым выходами блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 453697, кл.G F 7/38, 1972.

2. Авторское свидетельство СССР

Р 765803, кл.G 06 F 7/38, 1978 (прототип).