Стохастическое делительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Сецналнстнческнк

Ресл ублнк ф.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 29.10.80 (21) 3000353/18-24 ($1) М. КП. с присоединением заявки ¹

G 06 F 7/70

Государственный комитет

СССР по делам, изобретений и открытий (23) Приоритет с

Опубликовано 300782. Бюллетень ¹ 28 )53) УДК 681 ° 3 (088.8) Дата опубликования описания 30.07.82

В.В.Яковлев, И.Рааш, P.Ô.Ôåäîðîí, Г.В.ДобРис и A.Â.ßêoâëåí ф / !

5 ъ

" c

Ленинградский ордена Ленина институт инженефов.-. железнодорожного транспорта им. акад. В.Н.Образцова (72) Авторы изобретения (71) Заявитель (54 ) СТОХАСТИЧЕСКОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и предназначается для выполнения операции деления чиA сел — н стохастических вычислиВ тельных машинах (ЛФВ) .

Известны ст охастические делительные устройства, содержащие преобразователи код-вероятность, счетчики, логические элементы И, ИЛИ, НЕ, сумматоры, элементы задержки (13, (2) и 33.

Недостатком данных устройств является низкая точность нычислений, что вызвано применением метода одноразрядного вероятностного кодирования чисел A и В.

Наиболее .близким к предлагаемому является стохастическое делительное устройство, содержащее блок задержка, сумматор, преобразователь код-вероятность, блок умножения, блок инвертирования, входы которого соединены с разрядными шинами кода делителя, а выходы — c первой группой входов блока умножения, первая группа выходов которого подключена к второй группе входов сумматора, первая группа входов которого соединена с разрядными шинами кода делимого, а выходы — c выходами устройства (4).

Недостатком известного устройства

5 является также низкая точность выполнения операции деления.

Цель изобретения — повышение точности деления °

Поставленная цель достигается тем, что в стохастическом делительном устройстве, содержащем блок инвертирования, входы которого являются разрядными нходами делителя устройства, . блэк умножения, первая, группа входов которого соединена с выходами блока инвертирования, сумматор, первая группа входов которого является разрядными входами делимого устройства, вторая группа входов соединена с выходами младших раэрядон блока умножения, а выходы являются выходами устройства, преобразователь код-нероятность и блок задержки, входы блока задержки соединены с выходами сумматора, а выходы — с второй

25 группой входов блока умножения, выходы старших разрядов которого соединены с входами преобразователя код-вероятность, выход преобразователя код-вероятность соединен с вхо30 дом младшего разряда сумматора.

947858

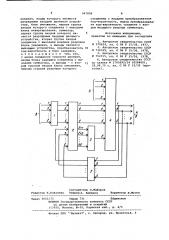

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит блок 1 инвертирования, блок 2. умножения, преобразователь 3 код-вероятность, сумматор 4, блок 5 задержки.

Разрядные входы шины (Е разрядов) кода делителя В подключены к 0 входам блока 1 инвертирования, Г выходов которого соединены с первой группой входов блока 2 умножения. )О

Первая группа выходов блока 2 умножения (шины с номерами 1, 2 ° ....С) соединена с второй группой входов сумматора 4, первая группа входов которого соединена с Е разрядными 15 входами делимого А, а выходы — с выходом устройства б и с б входами блока 5 задержки. Выходы блока 5 задержки подключены к второй группе (8 входов блока 2 умножения, вторая группа выходов которого (шины с номерами +1, 6+2,...,2f) соединена с 6 входами преобразователя 3 кодвероятность, выход которого соединен с входом младшего разряда сумматора 4.

Работа устройства управляется последовательностью синхроимпульсов,. подаваемых на соответствующие входы сумматора 4 и преобразователя код- ЗО

I вероятность 3 (входы не показаны) .

Пусть к некоторому 1-му синхроимпуль су на выход сумматора 4 передано

8-разрядное число z; . Это число с задержкой на один такт блок 2 умножения, на 2 выходах которого в 1+1-м такте образуется произведение э„(1-В). Обозначим часть этого произведения, получаемую на второй группе входов блока 2 умножения через „ . Это число („.e.q) в 1+1-м такте преобразуется преобразователем 3 код-вероятность в бинарный символ Х„+< Этот символ далее в том же такте поступает на вход младшего (0-го) разряда сумматора 4. Таким образом, случайная величина z4 4 - содержимое на выходах сумматора 4 в 1+1-м такте равна

z + =А+(1-В)z. — g„+„ +2 Х4 . (1)

-е

Математическое ожидание бинарного символа на выходе преобразователя код-вероятность равно

М (Х, + ) =2 М (g „+< ) . (2)

° ° оэтому при переходе к математичес им ожиданиям иэ (1) и (2) получаем N (z„ +4 ) =А+ (1-В) М (э,) ) .

Решение этого конечнораэностного р) уравнения получаем в виде

М(х ° ) = -(1-(1-В) ) . (3) ч В

При 1-+ со

М(Е1)= В. (4) (s=0, 1,2,... С), э" = e (e > -eee(eõф))(i- +зеив +>) Dz

Коэффициент К = - т выражает от0 носительное уменьшение статистической погрешности выполнения операции

А деления — в предлагаемом устройстВ ве по сравнению с известным. Анализ выражений . (5) и (6) показывает, что

0т=Вр только в случаях, когда А=О или А=В или В=1 или В=1-2.Во всех остальных случаях Dz(D,т,е. К 1.

Например, если A= — В=—

5 25

16 32

6=7 D = 4704. 2 4

4 -М а 0 = 25 - 2, т.е. К11000.

Таким образом, применение предлагаемого устройства позволяет повысить точность деления (в рассмотренном примере в 1000 раз).

Формула изобретения

Стохастическое делительное устройство, содержащее блок инвертит.е. в предлагаемом устройстве дейст вительно реализуется операция делеА ния чисел — .

Мерой точности работы устройства является дисперсия случайной величины z. Для известного устройства имеем (1)

DZ= у(В-А)(1 — В) (5)

При оценивании дисперсии случайной величины z на выходе предлагаемого устройства необходимо рассмотреть

2 случая.

Частное — точно представляется в

В (-разрядном коде. Это может произойти тогда, если

Ь = 2", а 2 (K=0,1,2,...p) или

b = 2 a, а=2е где a=2 А, b=2f В.

В этом случае дисперсия случайной

t величины z p H H (Dz=0).

Частное — не может быть точно

В представлено С-различным двоичным кодом. Это происходит во всех случаях, когда исходные операнды таковы, что

bP2 и Ьф2 а.

А

Разложим — на целую и дробную

В части

А e CA

2 ent(2 — ) + 2 Ь, -8 где 0 « l

ent — операции выделения целой части.

В этом случае

947858

Составитель О.Майоров

Редактор Н.Ковалева Техред А. Бабинец Корректор И.Муска

Заказ 5653/73 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент!, г. Ужгород, ул. Проектная, 4 рования, входы которого являются разрядными входами делителя устройства, блок умножения, первая группа входов которого соединена с выходами блока инвертирования, сумматор, первая группа входов которого яв- 5 ляется разрядными входами делимого устройства, вторая группа входов соединена с выходами младших разрядов блока умножения, а выходы являются выходами устройства, преобразователь tO код-вероятность и блок задержки, о т л и ч а ю щ е е с я- тем, что, с целью повышения точности деления, входы блока задержки соединены с выходами сумматора, а выходы — с второй группой входов блока умножения, выходы старших разрядов которого соединены с входами преобразователя код-вероятность, выход преобразователя код-вероятность соединен с входом младаего разряда сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 579624, кл. G 06 F 15/36, 1977.

2. Авторское свидетельство СССР

9 726529, кл. G F 15/36, 1978.

3. Авторское свидетельство СССР

Р 752355, кл. G Об F 15/36, 1978.

4 ° Авторское свидетельство СССР по заявке М 2745092/24 (028460), 28.09.79 r, кл. G 06 F 15/36 (прототип).