Устройство для регистрации сигналов ошибок

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соеетскнз

Социалнстическнк

Республик (ii) 947862

4 . (6() Дополнительное к авт. свид-ву.—

Р М,К з (22) Заявлено 10. 06.80 (21) 2940589/18-24

G 06,F ll/04 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет 53} УДК681. 326. .7 (088.8) Опубликовано 3007.82. Бюллетень № 28

Дата опубликования описания 30.07.82 (72) Авторы (54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ

ОШИБОК

Изобретение относится к вычислительной технике и автоматике и может найти применение в системах контроля и управления технологическими процессами.

Известно устройство для фиксации сбоев, содержащее выходной регистр, счетчик, дешифратор, элементы И, ИЛИ, НЕ, генератор импульсов, реле времени формирователь, регистр памяти (1).

Недостатками данного устройства являются ограниченные функциональные воэможности, обусловленные невозможностью определения первого по времени поступившего сигнала неисправности и следовательно ее первопричины.

Наиболее близким к предлагаемому является устройство фиксации сигналов ошибок, содержащее первый и второй регистры, реле времени, элементы И, формирователь признака ошибки (2).

Недостатками известного устрой- 25 ства являются ограниченные функциональные возможности, обусловленные тем, что устройство не позволяет выделить первый по времени сигнал ошибки, а также низкая достоверность 30 регистрации вследствие того, что одиночные сигналы (помехи) воспринимаются устройством как основные и регистрируются.

Цель изобретения — повышение достоверности регистрации и расширение функциональных воэможностей устройства. .Поставленная цель достигается .тем, что в устройство для регистрации сигналов ошибок, содержащее первое реле времени, первый и второй регистры соединенные первыми входами с первым и вторым входами устройства соответственно, выходы второго регистра соединены с первыми выходами устройства и входами формирователя признака ошибки, соедйненного выходом со вторым выходом устройства, элементы И по числу третьих входов устройства, соединенные первыми входами с четвертым входом устройства, вторыми входами — с соответствутощыми инверсными выходами первого регистра, введены по числу третьих входов устройства -элементы блокировки и по числу третьих входов устройства, без одного, вторые реле времени причем выходы первого и вторых

9 47862 реле времени соединены с соответствующими вторыми входами второго регистра, первые входы — с выходами соответствующих элементов И, каждый прямой выход первого регистра соединен с вторым входом соответствующего элемента И и с первыми входами неодноименных элементов блокировки, вторые входы которых соединены с соответствующими третьими входами устройства.

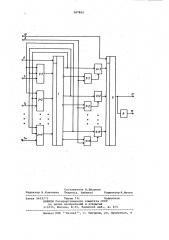

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит первый регистр 1, элементы 2 блокировки, элементы И 3, реле 4 времени, второй регистр 5, формирователь б признака ошибки, третьи входы 7, четвертый вход 8, первый вход 9, вто рой вход 10, первый 11 и второй 12 выходы. Элементы задержки могут быть выполнены на цифровой пересчетной схеме, например счетчике импульсов.

Устройство работает следующим образом.

В исходном состоянии, когда на входах устройства 7 отсутствуют сигналы ошибок, на вход 10 поступает сигнал сброса 5 регистра. В результате на выходах 11 и 12 устанавливается код отсутствия ошибок и сигнал отсутствия общей ошибки соответственно. На входы 8 и 9 поступают первый и второй сигналы синхронизации. Эти сигналы имеют одинаковую частоту, но первый сигнал синхронизации опережает второй сигнал синхронизации.

Второй сигнал синхронизации по входу 9 сбрасывает регистр 1. В результате на всех прямых выходах регистра 1 устанавливается уроC вень логического 0 . Тем самым на блокировочные входы всех элементов 2 блокировки не подаются запрещающие сигналы, и регистр 1 находится в режиме ожидания, т.е. возможности приема любого из сигналов ошибок, поступающих на входы 7.

Одновременно все инверсные выходы регистра 1 установлены в состояние логической 1 . Поэтому первый сигнал синхронизации, поступивший на вход 8, через все элементы H 3 установит все реле времени 4 i в сброшенное состояние.

-Устройство имеет три основных режима работы.

Йа одном из входов, например 7-2, присутствует устойчивый, периодически повторяющийся во времени, сигнал ошибки. При этом на других входах 7 сигналы ошибки отсутствуют.

На одном из входов, например 7-2, присутствует сигнал помехи (случайный одиночный импульс). HB других входах 7 сигналы отсутствуют. !

На двух входах, например 7-1 и

7-2, присутствуют устойчивые сигна- лы ошибок, а на остальных входах сигналы ошибок отсутствуют.

В первом режиме после поступления первого сигнала ошибки. на вход

7-2 он пройдет через элемент блокировки 2-2 и запишется во второй разряд регистра 1. После этого прямой и инверсный выходы второго раз10 ряда регистра 1 изменяют свое . состояние на противоположное. Уровень логической 1, установившийся на прямом выходе второго разряда регистра 1, запустит реле времени

4-2 и поступит на блокировочные входы .всех, кроме второго, элементов 2 блокировки. При этом прием остальных, кроме второго, сигналов ошибок заблокирован.

Для работы устройства необходимо, чтобы частота поступления сигналов синхронизации по входам 8 и 9 была меньше частоты любого из устойчивых

Во втором режиме после поступления на вход 7-2 .сигнала помехи устрой тво работает так же, как и в первом режиме, а именно: запускается реле 4-2 времени, в регистре 1 изменяется состояние прямого и инверсного выходов второго разряда. Однако первая пара сигналов синхронизации изменяет состоя60

65 сигналов ошибок, а период сигналов с ин крон из ации меньше выдержки любого из реле 4 времени.

Первый сигнал синхронизации, поступивший на вход 8, через элементы И 3 опрашивает состояние всех инверсных выходов регистра 1 и подтвердит сброшенное состояние всех, кроме второго, реле 4 времени. Реле времени 4-. 2 останется запущенным.

Второй сигнал синхронизации, поступивший на вход 9, производит сброс регистра 1, переводя тем самым его в режим ожидания.

Так как на вход 7-2 поступает повторяющийся сигнал ошибки, то через некоторое время на вход 7-2 поступает еще один сигнал. При этом устройство работает аналогично вышеописанному.

Рассмотренный процесс происходит при поступлении на вход 7-2 каждого нового сигнала ошибки до тех пор, пока не закончится выдержка реле

4-2 времени. После окончания выдержки реле времени, например заполнения пересчетной схемы до заданного двоичного кода, происходит запись информации во второй разряд регистра 5.

В результате эого на выходе 11 формируется код ошибки, а на выходе 12 появится сигнал наличия общей ошибки, что необходимо для начала прове-. дения диагностических процедур.

947862 ние устройства. Сигнал по входу 9 сбрасывает регистр 1, однако из-за отсутствия повторения сигнала на входе 7-2 новая запись в регистр 1 не произойдет. Поэтому при поступлении второй по времени пары сигналов синхронизации на входы 8 и 9 через элементы И 3 происходит сброс, всех включая, второе реле 4 времени. В результате устройство устанавливается в исходное состоя- 10 ние, следовательно осуществляется эффективная фильтрация случайных помех, действующих по входам 7. Пусть в третьем режиме и первым по времени является сигнал ошибки, поступа- !5 ющий на вход 7-2. Тогда обработка этого сигнала, происходит так же, как и в первом режиме, заканчивается формированием соответствующих сигналов на выходах 11 и 12. При 20 этом обработка сигнала ошибки, поступающего на вход 7 заблокирована, по той причине, что к моменту поступления сигнала на вход 7-1 его прохождение через элемент блокировки приема сигналов 2-1 заблокировано логической 1, поступающей от прямого выхода второго разряда регистра 1. В этом разряде записана информация о наличии на входе 7-2 сигнала. ошибки. Таким образом осу30 ществляется выделение первопричины в случае появления на входах 7 нескольких сигналов ошибок. итак, введение в устройство эле35 ментов 2 блокировки реле 3 времени позволяет отмечать помехи от сигнала и выделять первый по времени сигнал ошибки, что расширяет функциональные возможности устройства и увеличивает достоверность регистрации.

Формула изобретения

Устройство для регистрации сигналов ошибок, содержащее первое реле времени, первый и второй регистры, соединенные первыми входами с первым и вторым входами устройства соответственно, выходы второго регистра соединены с первыми выходами устройства и входами формирователя призна ка ошибки, выход которого является вторым выходом устройства, элементы И по числу третьих входов устройства, соединенные первыми входами с четвертым входом устройства, вторыми входами — с соответствующими инверсными выходами первого регистра, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности регистрации и расширения функциональных возможностей устройства, в него введены по числу третьих входов устройства элементы блокировки и по числу третьих входов устройства, без одного, вторые реле времени, причем выходы первого и вторых реле времени соединены с соответствующими вторыми входами второго регистра, первые входы — с выходами соответствующих элементов И, каждый прямой выход первого регистра соединен с вторым входом соответствующего элемента И и с первыми входами неодноименных элементов блокировки, вторые входы которых соединены с соответствующими третьими входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 601695, кл. G F 11/00, 1978.

2. Авторское свидетельство СССР

9 556441, кл. С 06 Г 11/00, 1977 (прототип).

947862

Составитель В.Дворкин

Редактор Н.Ковалева ТехредА. Бабинец Корректор И.Муска

Заказ 5653/73 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4