Двухполярный аналого-цифровой преобразователь с автоматическим масштабированием входного сигнала

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублин (1)947960 (Q)ty 1ф

= *";У

, (61) Дополнительное к авт. свид-ву(22) Заявлено 23.01.81(21) 3241629/21-18 (51) М. Кд.з с присоединением заявки ¹H 03 К 13/17

Государственный комитет

СССР но делам изобретений

- и открытий (23) Приоритет—

fS3) УДК 681 ° 325 ° (088.8) Опубликовано 300782. Бюллетень ¹ 28

Дата опубликования описания 30.07.82

/ " „.Г т Волков ñ е Я (72) Авторы изобретения

В.Д. Сысоев, В.И. Григорович, Ю.И. Шубин и А (71) Заявитель (54) ДВУХПОЛЯРНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

С АВТОМАТИЧЕСКИМ МАСШТАБИРОВАНИЕМ ВХОДНОГО

СИГНАЛА

1 2

Устройство относится к цифровой электроизмерительной технике и может быть применено в цифровых измерительных приборах, устройствах автоматики и вычислительной техники.

Известен аналого-цифровой преобразователь (АЦП ) с поразрядным кодированием, содержащий блок сравнения, блок управления, цифро-аналоговый преобразователь (1J, Недостатком известного АЦП является низкая точность представления сигнала в, цифровом коде при преобразовании входных сигналов с большим динамическим диапазоном, превосходящим динамический диапазон цифроаналргового преобразователя.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь, содержащий аналоговый запоминающий блок,,подключенный выходом к первому входу блока сравнения, второй вход которого соединен с выходом цифро-аналогового преобразователя, блок управления, блок коррекции, ключи, два элемента ИЛИ, блок установки кода, нуля, подключенный выходом к входам блока управ-1 ления, блок регулирующих резисторов, 1 два элемента НЕ, пять элементов И, генератор тактовых импульсов, анало- говый мультиплексор, реверсивный счетчик, триггер коррекции, соединенный выходом с входами первых элементов НЕ, И, а также реверсивного счетчика Г23.

Недостатком известного АЦП является невозможность работы в большом динамическом диапазоне входящих сигналов, ограничиваемых динамическим диапазоном цифро-аналогового преобразователя..

Цель изобретения — расширение ди-, намического диапазона входных сигналов при сохранении точности преобразования.

Поставленная цель достигается . тем, что в аналого-цифровой преобразователь, соДержащий аналоговый запоминаощий блок, первый вход которого соединен с первым выходом блока управления, первая группа управляющих выходов которого соединена с цифровыми входами цифро-аналогового преобразователя, первый выход которого соединен с первым входом блока сравнения, выход которого соединен с первым входом блока управления, ключ и элемент ИЛИ, дополнительно

947960 введены дискретный делитель, первый и второй пороговые элементы и счетчик масштаба, при этом второй вход аналогового запоминающего блока соединен с входной шиной, а выход подключен к входу дискретного делителя, группа управляющих входов которого соединена с второй группой управляющих выходов блока управления, второй выход которого соединен с первым входом ключа, выход которого соединен с вторым входом блока сравнения, а второй вход — с выходом дискретного делителя и первыми входами первого и второго пороговых элементов, вторые .входы которых соединены соответственно с вторым и тре тьим выходами цифро-аналогового преобразователя, причем выходы первого и второго пороговых элементов соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого подключен к второму входу бло ка управления, третий выход которого соединен с входом счетчика масштаба, группа выходов которого объедине на с группой информационных выходов блока управления и подключена к выходной шине °

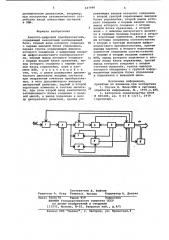

На чертеже приведена структурная электрическая схема устройства.

Устройство содержит аналоговый запоминающий блок 1, дискретный дели тель 2, ключ 3, блок 4 сравнения, цифро-аналоговый преобразователь 5, блок 6 управления, первый пороговый элемент 7, элемент ИЛИ 8, счетчик

9 масштаба, второй пороговый элемент 10.

Аналого-цифровой преобразователь работает следующим образом.

Цикл аналого-цифрового преобразователя начинается с приходом тактового импульса от блока 6 управления на аналоговый запоминающий блок 1, при этом последний устанавливается в режим запоминания мгновенного значения выходного сигнала. Процесс запоминания длится на протяжении первого такта, остальное время блок

1 находится в режиме хранения.

Выборка аналогового сигнала подается через дискретный делитель 2 на первые входы первого и второго пороговых элементов 7 и 10, на вторыв входы которых подаются соответст енно положительное и отрицательно опорные напряжения с цифро-анал ового преобразователя 5. Коэффициент-передачи дискретного делителя в начале каждого цикла преобразования устанавливается с блока 6 управления равным единице.

Если входной сигнал пороговых

7 и 10 по абсолютной величине меньше одного из опорных напряжений,,подаваемых с цифро.-аналогового преобразователя 5, коэффициент передачи дискретного делителя 2 сохраняется равным единице. При превыше нии по абсолютной величине входным сигналом пороговых значений опорных напряжений элементов 7 и 10, один из них дает команду через элемент

ИЛИ 8 на блок 6 управления на уменьшение коэффициента передачи дискретного делителя 2 в два раза. Коэффициент передачи дискретного делите10 ля 2 уменьшается ступенчато в 2и раз, где п — масштабирующий коэффициент, по сигналу с блока 6 управления до тех пор, пока входной сигнал пороговых элементов 7 и 10 по абсолютной величине не станет меньше одного из опорных напряжений.

При каждом уменьшении коэффициента передачи дискретного делителя

2 от блока 6 управления поступает сигнал на счетчик 9 масштаба, на выходе которого получают масштаб преобразуемого сигнала.

После окончания масштабирования входного сигнала по сигналу с блока 6 управления, ключ 3 замыкается и сигнал с дискретного делителя 2 подается на вход блока 4 сравнения.

С этого момента сигнал преобразуется по алгоритму поразрядного уравновешивания в цифровой код. На выходе устройства группа информационных выходов блока 6 управления объединяется с группой выходов счетчика

9 масштаба. Таким образом, на выходе преобразователя имеется пред3 ставление входного сигнала в цифро вом позиционном коде с учетом масштаба.

Ф

По сравнению с известным устройством предлагаемый аналого-цифро40 вой преобразователь позволяет увеличить динамический диапазон входных сигналов при сохранении точности представления сигнала в цифровом коде за счет того, что входной

45 сигнал перед преобразованием сравнивается с динамическим диапазоном цифро-аналогового преобразователя и при превышении его автоматически уменьшается с учетоь4 масштаба в Сы50

Применение AIJJI обладающего рас-, ширенным динамическим диапазоном входных сигналов, целесообразно при формировании массивов данных для расчета на ЭВМ характеристик нестационарных случайных процессов, отличающихся большой .неопределенностью динамического диапазона, так как он позволит повысить точность представления сигналов, избежать ошибок при вычислениях и, таким образом, привести к экономии средств.

Использование изобретения целесообразно при построении аналогоцифровых преобразователей, позволяющих работать с сигналами с большим

947960

Формула изобретения

Составитель В. Войтов

Редактор А. Огар Техред П. Пекарь Корректор Лзятко

Заказ 566 7 Тираж Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, динамическим диапазоном, например, при построении автоматического устройства ввода аналоговых сигналов в 3ВМ.

Аналого-цифровой преобразователь, содержащий аналоговый запоминающий блок, первый вход которого соединен 10 с первым выходом блока управления, первая группа управляющих выходов которого соединена с цифровыми входами цифро-аналогового преобразователя, первый выход которого соединен с первым входом блока сравнения, выход которого соединен с первым входом блока управления, ключ и эле.мент ИЛИ, отличающийся тем, что, с целью расширения динами- 0 ческого диапазона входных сигналов нри сохранении точности преобразования, в него дополнительно введены дискретный делитель, первый и,второй пороговые элементы и счетчик масштаба, при этом второй вход аналогового запоминающего блока соединен с входной шиной, а выход подключен к входу дискретного делителя, группа управляющих входов которого соединена с второй группой управляющих выходов блока управления, второй выход которого соединен с первым входом ключа, выход ко срого соединен с вторым входом блока сравнения, а второй вход — с выходом дискретного делителя и первыми входами первого и второго пороговых элементов, вторые входы которых соединены соответственно с вторым и третьим выходами цифроаналогового преобразователя, причем выходы первого и второго пороговых элементов соединены соответственно с первым и вторым входами элемента

ИЛИ; выход которого подключен к второму входу блока управления, третий выход которого соединен с входом счетчика масштаба, группа выходов которого объединена с группой информационных выходов блока управления и подключена к выходной шине.

Источники информации, принятые во внимание при экспертизе

1. Соучек Б. Мини-ЭВМ в системах обработки информации, N., 1976,с.385.

2. Авторское свидетельство СССР

Р 805490, кл. Н 03 К 13/17, 1979 (прототип).