Многоканальное устройство для анализа динамических параметров импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 29.11.79 (21) 2845122/18-24 (51)M Нп з с присоединением заявки №

G 01 R 31/28

0 06 F 15/20

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 0708.82. Бюллетень ¹ 29 (53) УДК 681. 3 (088.8) Дата опубликования описания 070882 (72) Автор изобретения

Ж.H. Ветшев

" < "-. ir .. „. -, k

>""оЛл „. К; -:;Научно-исследовательский институт ядерн дюдики npi4 Томском политехническом институте им. С.N. Кирова (71) Заявитель (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ АНАЛИЗА

ДИНАМИЧЕСКИХ ПАРАМЕТРОВ ИМПУЛЬСОВ

Изобретение относится к специализированньхч средствам вычислительной техники и предназначено для регистрации, наолюдения и измерения параметров однократных и редко повторяющихся сигналов.

Известно устройство, содержащее группу компараторов, память и блок индикации (17.

Наиболее близким к изобретению по технической сущности является многоканальное устройство, содержащее генератор тактовых импульсов, блок управления и индикации, счетчик, элемент И, а в каждом канале компаратор, коммутатор кода и регистр (21.

Однако известные устройства имеют недОстаточное быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в многоканальное устройство для анализа динамических параметров, импульсов, содержащее генератор тактовых импульсов, выход которого-соединен с первым входом элемента И, .второй вход которого соединен с первым выходом блока управления и индийации, счетчик, а в каждом канале .компаратор, первый вход которого соединен с входом устройства, выход компаратора соединен с управляющим вхо" дом коммутатора кода своего канала, выход-коммутатора кода первого канала соединен с входом регистра, введены генератор опорных сигналов, генератор эталонных частот, дешифратор нуля, а в каждый канал — регистр сдвига и дешифратор, причем выходы генератора опорных сигналов соединены с ,вторыми входами компараторов соответ:ствующего канала, выходы генератора эталонных:частот соединены с группами входов коммутатора кода .каждого канала, выход коммутатора кода каждого канала через дешифратор соединен с

20 группой входов регистра сдвига своего канала, выходы которых соединены с соответствующими группами входов бло- ка управления и индикации., группа выходов которого .соединена с первыми входами регистров сдвига каждого ка25 нала, вторые входы которых соединены с выходом элемента И и входом счетчика, выходы которого через дешифратор нуля:соединены с третьим входом элемента И, выходы регистра соединены с группой входов счетчика.

949556 ,законом кодовой измерительной шкалы разместит в регистре 12 последовательности единиц, разделенные последовательностями нулей, причем нули— результат пассивной фазы работы дешифратора.11. Пассивная фаза соответствует тем интервалам реального времени, на которых входной сигнал принимает значение логического нуля.

B эти интервалы времени коммутатор

10 10 закрыт. Все разряды регистра 12 предварительно устанавливаются в нулевое состояние управляющим сигналом, поступающим с выхода блока 1.

Вследствие асинхронного режима

15 работы логического анализатора входной логический сигнал длительности меньшей длительности интервала измерения может совпасть с концом одного и началом другого последующего цикла. При работе дешифратора 11 это приведет к сдвиговому искажению формы входного логического сигнала.

При этом регистр б воспринимает сигналы, соответствующие символам первой кодовой комбинации активной фазы работы дешифратора- 11. Двоичный код принятой комбинации заносится в счетчик 5. Содержимое счетчика 5 контролируется дешифратором 7, который вырабатывает сигнал "нуль", если содержимое счетчика 15 равно нулю и сигнал "единица", если содержимое счетчика 5 отлично от нуля. Сигнал

"единица" разрешает прохождение так, товых импульсов с генератора 2 в счетчик 5 и регистры 12 всех каналов. В момент равенства нулю содержимого счетчика 5 вырабатывается сигнал, который запрещает прохождение тактовых импульсов через элемент

4О H S. При этом в регистрах 12 произойдет циклический сдвиг информации (на число тактов, равное содержимому счетчика 5) в сторону нулевого разря-. да. Единица первой кодовой комбинации

45 (в первом канале), которая была занесена в разряд регистра 12 с номером, соответствующим числовому эквиваленту, переместится после сдвига в нулевой разряд регистра 12. Сигналы "едиgp ница", зафиксированные в регистрах

12. всех каналов, после сдвига займут положение, соответствующее шкале времени, начало которой совмещено с началом измерения.

Из регистров 12 сигналы накоплен-, ной логической информации передаются в блок 1 для визуального анализа.

Логический анализатор устанавливается в исходное (нулевое) состояние.

При применении изобретения быстродействие логических анализаторов может быть увеличено в 10.-100 раз. Формула изобретения

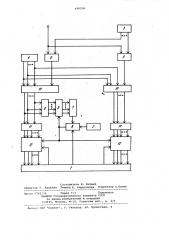

На чертеже приведена блок-схема устройства, Устройство содержит блок 1 управления и индикации, генератор 2 тактовых импульсов, генератор 3 опорных сигналов, генератор 4 эталонных частот, счетчик 5, регистр б, дешифратор 7 нуля, элемент И 8,,а в каждом канале — компаратор 9, коммутатор

10 кода, дешифратор 11 и регистр 12 сдвига.

Устройство работает следующим образом.

Ручной установкой соответствующих переключателей генераторов 3 и 4

;задаются на время работы уровни логического анализа по .каждому из каналов и масштаб линейной ступенчатой шкалы времени. В соответствии с номером канала генератор 3 фиксирует постоянные уровни логического анализа в абсолютных единицах измерения уровня входного сигнала, которые поступают на входы компараторов 9.Генератор

4 формирует различные, согласованные во времени, простые сигналы, которые поступают на входы коммутаторов 10 всех каналов. В последовательные интервалы времени системы простых сигналов образуют составной сигнал, который обеспечивает формирование кодовой измерительной шкалы и в режиме непрерывной генерации циклическое воспроизведение шкалы э реальном масштабе времени.

В режиме анализа сигнал от объекта исследования поступает на компараторы 9 всех каналов. В каждом из каналов компаратор 9 вырабатывает в соответствии с логикой сравнения сигналы высокого уровня (логическая единица) и сигналы низкого уровня (логический нуль) . Так как все каналы функционируют одинаковым образом, рассмотрим работу первого канала.

Сигнал с компаратора 9:.поступает на коммутатор 10 и пропускает составной сигнал на регистр б дешифратора

11. Низкий логический уровень прерывает доступ составного сигнала через коммутатор 10 на дешифратор 11. В этом состоянии регистр б запоминает код той кодовой комбинации, которая совпала с моментом начала измерения. Дешийратор 11 преобразует параллельный двоичный код в унитарный позиционный код. Этот сигнал с дешифратора 11 поступает на вход того разряда регистра 12, номер которого совпадает с номером числового эквивалента кода кодовой измерительной шкалы. Положение единицы, которая запоминается и хранится в регистре

12, согласует;.я, таким образом, с положением интервала времени на кол ной измерите п-ной шкале, которая кни»алентнз -з.талонной шкале времени, Д шифт «т< р !) н соответствии с

Многоканальное устройство для анализа динамических параметров импуль949556 сов, содержащее генератор тактовых импульсов, выход которого соединен с первым входом элемента И, второй вход которого соединен с первым вы; ходом блока управления и индикации, счетчик, а в каждом канале — компаратор, первый вход которого соединен с входом устройства, выход компаратора соединен с управляющим входом коммутатора кода своего канала, выход коммутатора кода первого кана- 10 ла соединен с входом регистра, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены генератор опорных сигналов, генератор эталонных частот, дешифратор нуля, а в каждый канал регистр сдвига и дешифратор, причем выходы генератора опорных сигналов соединены с вторыми входами компараторов .соответствующего канала, выходы о генератора эталонных частей соединены с группами входов коммутатора кода каждого канала, выход коммутатора кода каждого канала через дешифратор соединен с группой входов регистра сдвига своего канала, выходы которых соединены с соответствующими группами входов блока управления и индикации, группа выходов которого соединена с первыми входами регистров сдвига каждого канала, вторые входы которых соединены с выходом элемента И и входом счетчика, выходы которого через дешифратор нуля соединены с третьим входом элемента И, выходы регистра соединены с группой входов счетчика.

Источники информации, принятые во внимание при экспертизе

1. Экспресс-информация. Серия

"Контрольно-измерительная техника", Р 40, М.i BHHHTH,1978, с. 1-13.

2. Журнал "Приборы и техника эксперимента" 9 1, 1980, с. 98-101, (прототип).

349556

Составитель Ж. Ветшев

Редактор 1 . Кацалап Техред E. Харитончик Корректор O.Билак

Закаэ 5742/ 34 Тираж 717 Подписное

ВНИИПИ Государственного комитета СССР

l1o делам иэобретений и открытий

1130 35, Москва, Ж-35, Раушская наб., д. 4!5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4