Устройство для контроля электрических параметров электронных схем

Иллюстрации

Показать всеРеферат

(«)949557

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву . (22) Заявлено 301280 (21)3228350/24-21

31 М Nn з с присоединением заявки ¹

001а 31Д8

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (33) УДК 621. 317. .333(088.8) Опубликовано 07.08.82. Бюллетень ¹ 29

Дата опубликования описания 070882 (72) Авторы

Самарцев (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКИХ

ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ

Изобретение относится к электроиэмерительной технике и может быть использовано при создании устройств для контроля параметров электронных схем, включая полупроводниковые и гибридные интегральные схемы.

Известно устройство для автоматического контроля параметров электронных схем, содержащее управляющую вычислительную машину, устройство согласования, измерительные блоки, коммутационную матрицу и рабочие посты для подключения объектов контроля (1);

Недостатком этого устройства являются ограниченные функциональные возможности вследствие ограниченного объема памяти запоминающих устройств.

Наиболее близким к изобретению по технической сущности является устройство, содержащее m контрольных установок и и ввыыччииссллииттееллььнныых х ммаашшиинн,. соединенных посредством 8 адресных и k информационных шин через коммутатор, ° включающий m ..п(к + Р) ключей, управляющие входы которых соединены с соответствующими выходами первой группы блока сканирования, выходы второй группы которого соединены с ,соответствующими входами второй группы и-разрядного сдвигающего регистра, ды первой группы которого соединены с соответствующими выходами вычислительных машин, m-разрядный сдвигающий регистр, входы первой группы которого соединены с выходами соответствующих контрольных установок, а входы второй группы — c соответству-. ющими выходами третьей группы блока сканирования, выходы четвертой группы которого соединены с соответствующими входами блока прерывания программ, выходы которого соединены с входами соответствующих вычислительных машин, регистры признаков, входы

15 и выход ;оторых соединены с соответствующими информационными шинами, и дешифраторы; входы которых соединены с соответствующими адресными шинами, а выходы ". с входами соответствующих регистров признаков 2).

Недостатками известного устройства являются низкая точность контроля и ограниченные функциональные возможности»

Цель изобретения — повышение точности и расширение функциональных возможностей контроля.

Для достижения этой цели устрой ство для контроля электрических паЗО раметров электронных схем, содержа«

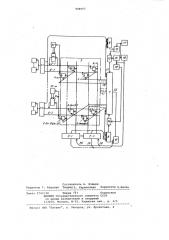

949557 щее m контрольных установок и и вы- (12-m), логические умножители 13 и числительных машин, соединенных пос- 14, сдвиговый регистр 15, преобразоредством (адресных и k информацион- ватель 16 кодов, генератор 17 такных шин через коммутатор, включаю- товых импульсов, счетчик 18 и управщий m n(k + 8) ключей, .управляющие ляющий вычислительный блок 19. входы кото1 ых соединены с соответст- Устройство работает следующим обвующими выходами первой группы блока разом. сканирования, выходы второй группы Пусть в исходном состоянии в запокоторого соединены с соответствующи-, минающие устройства вычислительных ми входами второй группы и-разрядного машин (2-1) — (2-n) записана прорраМсдвигающего регистра, входы первой «О ма работы, содержащая програмгруппы которого соединены с соответ- мы контроля изделий, причем чисствующими выходами вычислительной ло программных единиц, запимашины, m ðàýðÿäíûé: сдвигающий ре- санных в запоминающие устройстгистр, входы первой группы которого ва. может быть неодинаково у различ" соединены с выходами соответствующих 15 ных .вычислительных машин и ни одна контрольных установок, а axozga вто- из вычислительных машин не подключерой группы — с соответствующими вы- на к соответствующим контрольным ходами третьей группы блока сканиро- Установкам (1-1) — (1-m). Регистры вания, выход четвертой группы которо- 8,9,(11-1) †(11-m) и 15 установлены го соединены с соответствующими вхо- 20.-в исходное состояние. единичное сос-. дами блока прерывания программ, вы- тояние триггеров регистра 9 свидеходы которого соединены с входами со- тельствует о наличии свободных контответствующих вычислительных машин> рольных установок (1-1) †(1-m), а ререгистры признаков, входы и выходы гистра 8 — свободных для обслуживакоторых соединены с соответствующими ния вычислительных машин (2-1)-(2-n) .i информационными шинами, и дешифрато- В управляющем вычислительном блоке ры, входы которых соединены с соот- 19 записана информация о том, какие ветствующими адресными шинами, а вы- вычислителФиые машины (2-1) †(2-и) моходы — с входами соответствующих ре- гут.обслуживать каждую иэ контрольгистров признаков снабжено двумя ло- 0 ных Установок (1-1) †(1-m). Состояние

30 гическими умножителями, сдвиговым ре- сдвигового регистра 15 копирует в гистром, генератором тактовых импуль- >процессе работы состояние m-раэрядносов, счетчиком, управляющим вычисли- го регистра 9, тельным блоком и преобразователем Начинает работу генератор 17 таккодов, при этом входы первого логи- товых импульсов. Тактовые импульсы ческого умножителя соединены с выхо- З поступают на сдвиговый регистр 15, и дами соответственно преобразователя на его выходе появляется информация кодов и сдвигового регистра, входы (в виде логического нуля или логическоторого соединены с выходами соот- кой единицы) о занятости контрольных ветственно генератора тактовых им- установок. Одновременно тактовые импульсов и m-разрядного сдвигающего 140 пульсы проходят на счетчик 18, на регистра, входы второго логического выходах которого формируется код ноумножителя соединены с выходами соот- мера контрольной установки (1-1)ветственно и-разрядного сдвигающего (1-m), поступающий на преобразователь регистра и управляющего вычислитель- 16 кода и в управляющий вычислительного блока, выходы логических умножи- 45 ный блок 19 ° телей соединены с соответствующими Преобразователь 16 кода преобраэувходами блока сканирования, вход -ет код номера контрольной устасчетчика соединен с выходом генера- новки (1-1)-(1-m) h параллельный т тактовых импульсов а его выхо- :позиционный код. В зависимости ора

t нт ольной стады — соответственно с входами управ- 0 от кода номера контрольно у ляющего вычислительного блока, дре- новки управляющий вычислительный образователя кодов. и вычислительных блок 19 формирует и-разрядный управляющий код. В логическом умноНа чертеже представлена структур- жителе 14 происходит поразрядное ная электрическая схема устройства. умножение кодов сдвигающего региУстройство содержит m контрольных стра 8 и управляющего вычислительустановок (1-1)-(1-m), n вычисленных ного блока 19. машин (2-1)-(2-n), коммутатор 3, Непрерывно работающий блок. 7 включающий m n(k + 1>) ключей (4-1)-, сканирования дешифрует коды, пос (4-m .n -(k + В), Ю адресных шин (5- 1)- тупающие с логических умножителей (5- И),М информационных шин (6- )- 60 13 и 14, и подключает при помощи (6-й),. блок 7 сканирования, и-разряд- ключей (4-Ц вЂ (4-в ° n ° (k + У)) вычисный сдвигающий регистр 8, m-разрядный лительные машины (2-1)-(2-n) к дансдвигающий регистр 9, блок 10 пре- ной контрольной установке (1-1)рывания программ, регистры (11-1)- (1-m) и одновременно устанавливает (11-m) признаков, дешифраторы (12-1)- 65 в нулевое состояние регистры 8 и 9.

949557

Сигналы блока 7 сканирования поступают через блок 10 на вход прерывания соответствующей вычислительной машины (2-1) †(2-n). По сигналу прерывания и в соответствии с номером контрольной установки (1-1) †(1-m) вычис- 5 лительная машина осуществляет ввод программы контроля. Аналогично происходит процесс подключения для других вычислительных машин и контрольных установок. 10

После ввода командной и информационной частей программы начинается выполнение программы контроля установками (1-1) †(1-m). По окончании ввода программы контроля вычислитель-15 ные машины (2-1) †(2-и) выдают сигналы, которые устанавливают регистр 8 в единичное состояние. Кроме того, последняя перед прерыванием команда программы контроля расшифровывается дешифратором (12-1)-(12-m) и подготавливает к приему регистр (11-1) †(1-m) призйаков.

В регистрах (11-1) †(11-m) записывается последнее перед прерыванием информационное слово — относительный (относительно начала программы контроля) адрес ячейки памяти, с которого должно быть продолжено после прерывания дальнейшее выполнение программы.

По окончании выполнения программы контроля установки (1-1)-(1-m) выдают сигнал окончания работы. Этот сигнал поступает на регистр 9, устанавливая его в единичное состояние.

Подключение освободившейся контрольной установки происходит описанным способом. После подключения и этой установки к вычислительной машине (2-1)-(2-и) последняя первой коман- 40 дой через дешифратор (12-1)-(12-m) опросит регистр (11-1)-(11-m) признаКов, хранящий относительный адрес, расшифрует его и в зависимости от номера контрольной установки (1-1)— (1-m), определит начальный адрес последующей части программы контроля, после чего перейдет к ее выполнению.

Аналогично работают и остальные контрольные установки. 50 формула изобретения устройство для контроля электрических параметров электронных схем, содержащее m контрольных установок и

П вычислительных машин, соединенных посредством 0 адресных и М информационных шин через коммутатор, включающий rn-n(9+0) ключей, управляющие входы которых соединены с соответствующими выходами первой группы блока сканирования, выходы второй группы которого соединены с соответствующими входами второй группы и -разрядного сдвигающего регистра, входы первой группы которого соединены с соответствующими выходами вычислительных машин, rn -разрядный сдвигающий регистр, входы первой группы которого соединены с выходами соответствующих контрольных установок, а входы второй группы — с соответствующими выходами третьей группы блока сканирования, выходы четвертой группы которого соединены с соответствующими входами блока прерывания программ, выходы которого соединены с входами соответствующих вычислительных машин, регистры признаков, входы и выходы ко" торых соединены с соответствующими информационными шинами, и дешифраторы, входы которых соедийены с соответствующими адресными шинами, а выходы - с входами соответствующих ре» гистров признаков, о т л и ч а ю— щ е е с я тем, что, с целью повышения точности и расширения функцио» нальных возможностей контроля, оно снабжено двумя логическими умножителями, сдвиговым регистром, генератором тактовых импульсов, счетчиком, управляющим вычислительным блоком и преобразователем кодов, при этом входы первого логического умножителя соединены с выходами соответственно преобразователя кодов и сдвигового регистра, входы которого соединены с выходами соответственно генератора тактовых импульсов ив -разрядного сдвигающего регистра, входы второго логического умножителя соединены с выходами соответственно и -разрядного сдвигающего регистра и управляющего вычислительного блока, выходы логических умножителей соединены с соответствующими входами блока сканирования, вход счетчика соединен с выходом генератора тактовых импульсов, а его выходы — соответственно с входами управляющего вычис- . .лительного блока, преобразователя кодов и вычислительных машин.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 G R. 31/28, 1969.

2. Авторское свидетельство СССР

9 471560, кл. G 01 R 31/28,. 1976.

949557

Составитель A. Изюмов

Редактор Г. Кацалап Техред E. Харитончик КорРектор О.Билак

Заказ 5742/34 Тираж 717 Подписное

ЭНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4