Компаратор

Иллюстрации

Показать всеРеферат

(72) Автор иэобретения

В. А. шульгин

1 ф .. I

1

Воронежский ордена Ленина государственный ерснтер;;, ... им. Ленинского комсомола

3 (7L) Заявитель (54) КОМПАРАТОР

Изобретение относится к автоматике и импульсной технике и может быть использовано в системах автоконтроля, быстродействующих кодирующих преобразователях, в цифровых мостах.

Известен синхронный компаратор с запоми- 5 нанием, в котором лервыи каскад выполнен на дифференциальном усилителе, резистивная нагрузка которого включена через развязывающие транзисторы, согласующие транзисторы, второй дифференциальный усилитель и ключ Щ10

Недостатком данного компаратора является малое быстродействие.

Наиболее близким к предлагаемому является компаратор, содержащий первый и второй дифференциальные усилители, выполненные на транзисторах различных типов проводимости, базы транзисторов первого дифференциального усилителя соединены с соответствующи- ми входами компаратора, а коллекторы — с базами соответствующих транзисторов второго дифференциального усилителя s с одними из выводов нагрузок транзисторов первого дифференциального усилителя, другие выводи которых соединены, эмиттеры транзисторов второго дифференциального усилителя соединены с Первым источником тока, а коллекторы — через нагрузки транзисторов второго дифференциального усилителя — с шиной нулевого потенциала, ключ, управляющий вход которого подключен к управляющему входу компаратора, первый и второй источники напряжения и второй источник тока (2).

Недостатком известного компаратора является малое быстродействие.

Цель изобретения — повышение быстродействия компаратора.

Указанная цель достигается тем, что в известный компаратор введены в качестве нагрузок транзисторы первого и второго дифференциальных усилителей соответственно, первый, второй, третий и четвертый диоды, а также туннельный диод и транзистор, тип проводимости которого совпадает с типом проводимости у транзисторов второго дифференциального усилигеля, причем эмиттер транзистора соединен с эмиттерами транзисторов второго дифференциального усилителя, коллек9496

3 тор — с шиной нулевого потенциала, а база — с первым источником напряжения, базы транзисторов первого дифференциального усилителя соединеныс коллекторами соответствуюших транзисторов второго дифференциального усилителя, эмиттеры через ключ — со вторым источником тока, а коллекторы — с соответствующими выходами компаратора, а одни из выводов первого и второго диодов подключены через туннельный диод ко второму ис- 10 точнику напряжения.

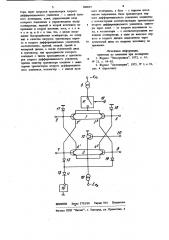

На чертеже приведена электрическая схема компаратора.

Устройство содержит первый дифференциальный усилитель 1, выполненный на транзисторах 2 и 2, второй дифференциальный усилитель 3 — на транзисторах 4, и 4, входы компаратора 5 и 6,выходы компаратора

7 и 8, первый источник 9 тока (одной полярности), второй источник. 10 тока (другой полярности), ключ (тока) 11, транзистор 12, первый 13 и второй 14 диоды нагрузки транзисторов первого дифференциального усилителя, туннельный диод 15, первый источник 16 напряжения, третий 17 и четвертый 18 д диоды (нагрузки транзисторов второго дифференциального усилителя), управляющий вход

19 компаратора и второй источник 20 напряжения.

Компаратор работает следуюшим образом.

На входы компаратора 5 и 6 подключаются источники сравниваемых токов. В ждушем режиме компаратора ключ 11 разомкнут, и поэтому ток через первый и второй диоды 13 и 14 и туннельный диод 15 практически от35 сутствует. Такой режим соответствует малому падению напряжения на туннельном диоде

15. Потенциал базы транзистора 12 выбирается таким, чтобы в этом случае транзистор

12 открыт и весь ток первого источника 9 до тока протекает через него. Ясно, что при этом эмиттерные переходы транзисторов 4 и 4 второго дифференциального усилителя

3 находятся под запирающим смещением.

С приходом строб-импульса на управляющий вход компаратора 19 ключ 11 замыкается.

Ток транзисторов 2 и 2 первого дифференциального усилителя 1, нарастая в соответствии с динамическими характеристиками ключа

11 и фронта строб-импульса, проходит через первый и второй диоды 13 и 14 и туннель- >в ный диод 15. Причем распределение тока между транзисторами 2 и 2 соответствует падениям напряжений на третьем и четвертом диодах 17 и 18, и, следовательно, величинам входных анализируемых сигналов. Аналогичным образом, перераспределяются падения напряжений на первом и втором диодах.13 и 14, после усиления входного сигнала первым диф27 4 ференциальным усилителем 1. В некоторый момент нарастания тока через туннельный диод 15 он переключится в состояние с большим падением напряжения, что приведет к очень быстрому изменению потенциалов выходов компаратора 7 и 8 по отношению к потенциалу базы транзистора 12. Этот потенциал выбран таким образом, чтобы наряду с ранее приведенным, условием в данном случае он обеспечивал закрытие транзистора 12 и, следовательно, прохождение всего тока первого источника тока 9 через транзисторы 4 и 4 . Между этими транзисторами ток перераспределится в соответствии с существуюши1 ми в данный момент соотношением токов первого и второго диодов 13 и 14. Начинает действовать положительная обратная связь, которая переводит схему компаратора в одно из устойчивых состояний, сохраняющихся до тех пор, пока замкнут ключ 11. Информацией о состоянии схемы компаратора служат падения напряжений на первом и втором диодах 13 и 14. Для нормального функционирования компаратора сумма входных анализируемых токов íà его входах 5 и 6 должна быть меньше тока первого источника тока 9 с тем, чтобы схема компаратора сохранила свое состояние независимо от значения входного сигнала.

Уменьшение задержки распространения сигнала в компараторе и апертурного времени достигается за счет того, что "включение" положительной обратной связи происходит при больших токах через первый и второй диоды

13 и 14, имеющих в этом случае малые динамические сопротивления. Поэтому цепь обратной связи работает при больших сигналах

"перевозбуждения", что способствует улучшению динамических характеристик компаратора.

Такое выполнение изобретения позволяет повысить его быстродействие по сравнению с известными компараторами.

Формула изобретения

Компаратор, содержащий первый и второй дифференциальные усилители, выполненные на транзисторах различных типов проводимости, базы транзисторов первого дифференциального усилителя соединены с соответствующими входами компаратора, а коллекторы — с базами соответствуюших транзисторов второго дифференциального усилителя и с одними из выводов нагрузок транзисторов первого дифференциального усилителя, другие выводы которых соединены, эмиттеры транзисторов второго дифференциального усилителя соединены с первым источником тока, а коллек949627

ВНИИПИ Заказ 5753(38 Тираж 914 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 торы через нагрузки транзисторов второго дифференциального усилителя — с шиной нулевого потенциала, ключ, управляющий вход которого подключен к управляющему входу компаратора, первый и второй источники напряжения и второй источник тока, о т л ич а ю щ и и сятем,,что, с целью повышения быстродействия компаратора, он содер жит s качестве нагрузок транзисторы первого и второго дифференциальных усилителей, соответственно, превый, второй, третий и четвертый диоды, а также туннельньй диод и транзистор, тип проводимости которого совпадает с типом проводимости у транзисторов второго дифференциального усилителя, причем эмиттер транзистора соединен с эмиттерами транзисторов второго дифференциального усилителя, коллектор — с шиной нулевого потенциала, а база — с первым источником напряжения, базы транзисторов первого дифференциального усилителя соединены с коллекторами соответствующих транзисторов второго дифференциального усилителя, эмиттеры через ключ — со вторым источником тока, а коллекторы — с соответствующими выходами компаратора, а одни иэ выводов первого и второго диодов подключены через туннельный диод ко второму источнику на пряжения.

I. Источники информации, принятые во внимание при экспертизе, 1. Журнал "Электроника", 1972, т. 45, Н 21, с. 54 — 62.

2. Журнал "Автометрия", 1975, N 1, с. 91, рис. 4 (прототип).