Устройство программного управления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕИ ДЬСТВУ

Союз Советских

Социалистических

Республик

< н949656 (61) Дополнительное к авт. свид-ву (22) Заявлено 05. 07. 77 (21) 2505576/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 07.08.82.Бюллетень № 29

Дата опубликования описания 07. 08. 82

151) М. Кп.з

G 06 F 9/06

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.14 (088.8) (12) Авторы изобретения,Р; ф

В.Ф.Мелехин и Г.Каульфус! с

° 1

Ленинградский ордена Ленина политехн ческйй" (11) Заявитель институт им. М. И. Калинина (54) УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано при проектировании вычислительных машин и систем, в частности управляющих вычислительных машин,„

Известно устройство управления ЦВМ с произвольным следованием команд, адрес которых содержится непосредственно в коде предыдущих команд $13.

Известно также устройство управления ЦВМ, содержащее счетчик команд, первый вход которого соединен с выходом регистра команд, второй с вхо.дом устройства, а выход — с входом регистра адреса, подключенного к адресным входам блока памяти, выход которого соединен с входом регистра числа, первый выход которого подключен к информационному входу блока памяти, второй выход — к второму выходу устройства, а третий выход - к входу регистра групп.нз и последовательно соединенных групп триггеров, выход которого подключен K входу дешифратора номера разрядов, выход которого подключен к входу регистра команд (23.

Недостаток известного устройства состоит в том, что не предусмотрена реализация команд безусловных переходов, т.е. невозможно следование команд с произвольным адресом в ,виде исключения, Это обстоятельство существенно усложняет предварительное кодирование адресов команд "соседними" кодами.

Устройство управления, выполняющее команды в естественном порядке, достаточно сложно и недостаточно эффективно при большом количестве разветвлений из-за большого числа условных и безусловных переходов.

Основным недостатком известного устройства является то, что выполнение

15 команд условных и безусловных переходов требует применения специальных команд, в которых указан адрес перехода.

Осуществление устройства управления с произвольньм следованием команд требует в каждой команде добавочного поля для указания адреса следующей команды. Это приводит к существенному увеличению аппаратурных затрат оперативной памяти и является недостатком устройства.

Цель изобретения — сокращение объема оборудования.

Для достижения поставленной цели в устройство, содержащее блок памяти, 949656 дешифратор, регистр адреса, регистр числа, регистр команд, триггер услоний, причем выход блока памяти соединен с первым входом регистра числа и входом регистра команд, первый вход блока памяти является первым 5 входом устройства, выход регистра числа является первым выходом устройства и подключен к второму входу блока памяти, третий вход которого подключен к выходу регистра адреса и со-)p соединен с вторым нходом регистра числа, первый нхад регистра адреса подключен к первому выходу дешифратора, вход которого соединен с первым выходом регистра команд, второй выход которого является вторым выходом устройства, вход триггера условий является вторым входом устройства, введены коммутатор и коммутатор кода адреса, выход которого соединен с вторым входом регистра адреса, третий вход которого подключен к выходу коммуматора, первый вход которого подключен к выходу триггера условий, а второй вход коммутатора соединен с. вторым выходом дешифратора, первый вход коммутатора кода адреса является третьим входом устройства, второй вход коммутатора кода адреса подключен к третьему выходу регистра команд, а третий вход коммутатора кода адреса соединен с выходом блока памяти.

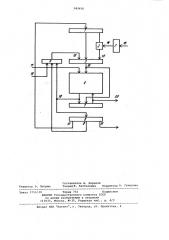

На чертеже представлена блок-схема устройства.

Устройство программного управления 35 состоит из дешифратора 1, триггера 2 условий, коммутатора 3, коммутатора

4 кода адреса, регистра 5 адреса,блока б памяти, регистра 7 числа и регистра 8 команд. На чертеже обозначе- 49 ны второй выход 9 регистра команд, вход

10 записи регистра адреса, первый выход 11 регистра команд, третий выход

12 регистра команд, счетные входы 13 триггеров регистра адреса, выход 14 45 триггера условий, информационный вход

15 триггера условий, выход 16 регистра адреса, третий выход 17 устройства, числовая магистраль 18, второй вход 19 устройства, первый вход 20 устройстна. Регистр 5 адреса построен на триггерах со счетными входами (входы 13 и 14 регистра 5) и входами 10 записи.

Устройство работает следующим об-,55 фаном. Код каждой команды содержит кроме кода операции и адресов операндов еще одно адресное поле для указания адреса следующей команды. В этом ад- 60 ресном поле хранится код модификации адреса. Этот код представляет собой код номера разряда,.который следует изменить н коде адреса предыдущей команды, чтобы получить адрес сле-65 дующей. Разрядность кода модицикации адреса и равна

n >, 0од Ход N„, где N — количество команд програм-. мы е

Предпосылкой использования этого способа является применение "соседнего" кодирования для кодов адреса таким образом, что код адреса каждой последующей команды отличается от кода предыдущей значением только одного разряда.

Процесс кодирования адресов команд можно выполнять при помощи специальной программы на ЦВМ.

На каждом командном цикле выполняется алгоритм, показанный ниже, 1

1) выборка адреса А; первой (или первой после прерывания коман ды K„ ïðîãðàììû

PAK A „., PA PAK;

2) выборка команды К

РК вЂ” Н tPAl i

3) исполнение команды К, 4) формирование адреса очередной : команды;

5) засылка адреса новой команды в PAK

РЧ ". — PA, РАК РЧ;

6) есть сигнал окончания или прерывания.

В алгоритме используются следующие сокращения: PAK — регистр адреса команды, PA - регистр адреса, РЧ— регистр числа, H(PA) — содержимое ячейки накопителя по адресу PA.

В блоке "Формирование адреса очередной команды" адгоритма реализуются различные регистровые пересылки и модификации (М) в зависимости от вида команды: а) команда условного перехода

PA PAK, PA=(PA, ° КМА, ТУ); б) команда линейного участка программы

PA <†PAK, PA=M(PA, KMA) в) команда безусловного перехода

PA+ — PK, где КИА — код модификации адреса и

ТУ вЂ” триггер условий.

Согласно алгоритму формируется после исполнения команды адрес очередной команды таким образом, что в начале из блока б памяти считывается содержимое регистра адреса команд (РАК) и передается через коммутатор

4 кода адреса в регистр 5 адреса.

Затем выходные сигналы на первом выходе 12 (выход адресного поля кода Модификации адреса) регистра

8 команд поступают на вход дешифратора 1, который расшифровывает номер разряда, подлежащего изменению. Расшифрованный выходной сигнал дешифратора 1 поступает на соответствующий

949656 счетный вход 13 регистра 5 адреса, образуя тем самым адрес очередной команды.

Команды условного перехода реализуются таким образом, что при выполненном условии адрес очередной команды 5 формируется, как показано выше, а при невыполненном условии выходной сигнал триггера 2 условий, находящийся в единичном состоянии, подается через коммуматор 3 на счетный вход 14 одно-10 го разряда, например старшего, регистра 5 адреса, изменяя дополнительно этот. разряд.

В данном устройстве предусмотрена возможность передачи полного адреса команды с регистра 8 команд через коммутатор 4 кода адреса в регистр 5 адреса, т.е. возможно осуществлять отдельные команды безусловного перехода. Эта возможность использования отдельных команд безусловнЫх переходов облегчает достаточно сложный процесс кодирования адресов команд соседними кодами °

Технико-экономический эффект устройства заключается в повышении эко25 номичности, а в сравнении с устройствами, использующими естественную адресацию команд, также и в повышении прбизводительности ЦВМ. формула изобретения (Устройство программного управлейия, содержащее блок памяти, дешифратор, регистр адреса, регистр числа,35 регистр команд, триггер условий, причем выход блока памяти соединен с первым входом регистра числа и входом регистра команд, первый вход блока памяти является первым входом устройст-. ва, выход регистра числа является первым выходом устройства и подключен к второму входу блока памяти, третий вход которого подключен к выходу регистра адреса и соединен с вторым входом регистра числа, первый вход регистра адреса подключен к первому выходу дешифратора, вход которого соединен с первым выходом регистра команд, второй выход которого является вторым выходом устройства, вход триггера условий является вторым входом устройства, о т л и ч а:ю щ е е с я тем, что, с целью сокращения объема оборудования, в него введены коммутатор и коммутатор кода адреса, выход которого соединен с вторым входом регистра адреса,.третий вход которого подключен к выходу коммутатора, первый вход которого подключен к выходу триггера условий, а второй вход коммутатора соединен с вторым выходом дешифратора, первый вход коммутатора кода адреса является третьим входом устройства; второй вход коммутатора кода адреса подключен к третьему выходу регистра команд, а третий вход коммутатора кода адреса соединен с выходом блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Бут Э. и Бут К. Автоматические цифровые машины." M., Гос.изд-во фиэ;.мат.литературы, 1959, с. 50, 205.

2. Авторское свидетельство СССР

Р 416695, кл. G 06 F 9/06, 1974 (прототип).

949656

Составитель A. Баранов

ТехредЖ. Кастелевич Корректор А Гриценко

Редактор В. Петраш

Филиал ПЛП "Патент", г . Ужгород, ул. Проектная, 4

Заказ 5755/39 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5