Устройство аналого-цифрового преобразования

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИЯЕТЕЛЬСТВУ

<„>949806 (я) дополнительное к авт. свид-ву— (22) Заявлено 21.04.80 (21) 2912399/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

Н 03 К 13/17

Гвеудвретвевлмв квмлтет

СССР (53) УДК 681.325 (088.8) Опубликовано 07.08.82. Бюллетень №29

Дата опубликования описания 17.08.82 лв делам лзвбретений и вткрмтий (54) УСТРОИСТВО АНАЛОГО-ЦИФРОВОГО

ПРЕОБРАЗОВАНИЯ

Изобретение относится к электроизмерительной и вычислительной технике и предназначено для преобразования стационарных эргодических случайных сигналов в цифровой код.

Известно устройство аналого-цифрового преобразования, состоящее из аналого-цифрового преобразователя, первого и второго регистров, сумматора-вычитателя, блока сравнения и блока задатчика ошибки, причем на первый вход аналого-цифрового преобразователя подан входной сигнал, на второй вход подан сигнал «Пуск», выход его соединен с входом первого регистра, выход которого соединен с первым входом сумматора-вычитателя, второй вход последнего соединен с выходом второго регистра (1).

Недостатком известного устройства является отсутствие возможности аналого-цифрового преобразования с заданной среднеквадратической погрешностью восстановления.

Цель изобретения — оптимизация выбора интервала временной дискретизации, обеспечивающего заданную среднеквадратическую погрешность восстановления преобразуемого сигнала.

Поставленная цель достигается тем, что в известное устройство аналого-цифрового преобразования, содержащее блок задания ошибок, блок сравнения, преобразователь аналог — код, первый вход которого соединен

5 с входной шиной, второй — с шиной «Пуск», а выход — с входом первого регистра и первым входом второго регистра, выход которого соединен с выходной шиной и первым входом блока суммирования и вычитания, введены счетчик, регулируемый делитель частоты, два блока усреднения, умножитель, два квадратора, вход первого из которых соединен с выходом первого регистра и вторым входом блока суммирования и вычитания, а выход — с входом первого блока усреднения, выход которого соединен с первым входом умножителя, второй вход которого соединен с блоком задания ошибки, а выход — с первым входом блока сравнения, при этом вход второго квадратора соединен с выходом блока суммирования и вычитания, а выход — с входом второго блока усреднения, выход которого соединен со вторым входом блока сравнения, выход которого соединен с первым входом регулируемого делителя частоты, второй вход — через счет949806 вычитания и, кроме того, выход регистра 4 соединен с выходом устройства, а выход регистра 3 соединен с входом квадратора 6, 2, выход которого соединен с входом усредни25

55 чик с шиной «Пуск», а выход — со вторым входом второго регистра.

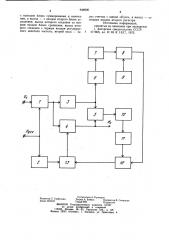

На чертеже представлена блок-схема предлагаемого устройства аналого-цифрового преобразования.

Устройство содержит преобразователь 1 аналог — код, счетчик 2, регистры 3 и 4, блок 5 суммирования-вычитания, квадратор 6, блок 7 усреднения, умножитель 8, блок 9 задатчика ошибки, блок 10 сравнения, блок 11 усреднения, квадратор 12, регулируемый делитель 13 частоты.

На вход преобразователя 1 аналог-код подан входной сигнал, на второй вход подан сигнал «Пуск», который, кроме того, подан на вход счетчика 2, выход преобразователя 1 аналог — код соединен с входом регистров 3 и 4, выходы которых соединены с первым и вторым входами блока 5 суммирования и теля 7, выход последнего соединен с первым входом умножителя 8, второй вход которого соединен с выходом блока 9 задатчика ошибки, а выход соединен с первым входом блока 10 сравнения, второй вход которого соединен с выходом блока 11 усреднения, вход последнего соединен с выходом квадратора 12, вход которого соединен с выходом блока 5 суммирования и вычитания, выход блока 10 сравнения соединен с первым входом регулируемого делителя 13 частоты, первый вход которого соединен с выходом счетчика 2, а выход соединен с вторым входом регистра 4.

Устройство работает следующим образом. В блоке 9 задания ошибки записан код заданной среднеквадратической ошибки восстановления кодируемого сигнала. При подаче на вход преобразователя 1 аналог— код запускающих импульсов, частота следования которых первоначально равна частоте

45 поступает код среднеквадратического значения напряжения. В умножителе 8 это значение умножается на код заданной относительной и среднеквадратическую ошибку восстановления 6зад, а получение значение

-z кода абсоЛютной заданной среднеквадратической ошибки восстановления У подается на вход блока 10 сравнения, на другой вход которого с выхода блока 11 усреднения подается код абсолютного значения текущей среднеквадратической ошибки У„

Если Ь, <<Ь2 д, то регулируемый делитель 13 частоты уменьшает на единицу частоту записи результатов преобразования в регистр 4 и в него записывается каждое второе значение кодируемого сигнала, после чего процесс повторяется. Уменьшение частоты записи результатов преобразования в регистр 4 продолжается до тех пор, пока

@„ах не станет на каком-то и-ом периоде больше Ь д. При этом по сигналу от блока

10 сравнения регулируемый делитель 13 частоты увеличивает на единицу частоту записи кода в регистр 4, при которой 37 Ä(3 5a и процесс изменения частоты записи кода в регистр 4 прекращается. Значение выходного кода считывается с регистра 4.

Таким образом, в результате ряда измерений входного сигнала в зависимости от заданной среднеквадратической погрешности восстановления автоматически устанав ливается интервал дискретизации, при котором среднеквадратическая ошибка восстановления кодируемого сигнала не превышает заданную.

Формула изобретения

Устройство аналого-цифрового преобразования, содержащее блок задания ошибок, блок сравнения, преобразователь аналог— код, первый вход которого соединен с входной шиной, второй — с шиной «Пуск», а выход — с входом первого регистра и первым входом второго регистра, выход которого соединен с выходной шиной и первым входом блока суммирования и вычитания, отличающееся тем, что, с целью оптимизации выбора интервала временной дискретизации, обеспечивающего заданную среднеквадратическую погрешность восстановления преобразуемого сигнала, в него введены счетчик, регулируемый делитель частоты, два блока усреднения, умножитель, два квадратора, вход первого из которых соединен с выходом первого регистра и вторым входом блока суммирования и вычитания, а выход — с входом первого блока усреднения, выход которого соединен с первым входом умножителя, второй вход которого соединен с блоком задания ошибок, а выход — с первым входом блока сравнения, при этом вход второго квадратора соединен

949806

Составитель А. Кузнецов

Редактор Л. Горбунова Техред А. Бойкас Корректор В. Синицкая

Заказ 5495/47 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! l 3035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 с выходом блока суммирования и вычитания, а выход — с входом второго блока усреднения, выход которого соединен со вторым входом блока сравнения, выход которого соединен с первым входом регулируемого делителя частоты, второй вход — через счетчик с шиной «Пуск», а выход — со вторым входом второго регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

471666, кл. Н 03 К !3/17, 1972.