Нелинейное корректирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<111951231 (61) ???????????????????????????? ?? ??????. ????????-????(22) ???????????????? 19.04.80 (21) 2932292>

Опубликовано 150882,. Бюллетень №30

Р1 М К з

G 05 В 5/01

Государственный комитет

СССР ио делам изобретений и открытий

Ю3 УДКбг-50 (088.8)

Дата опубликова ия описания 150882 аявитель (54) НЕЛИНЕЙНОЕ КОРРЕКТИРУЮЦЕЕ УСТРОЙСТВО

Изобретение относится к автоматическому управлению и может найти применение в следящих системах, условия работы которых требуют повышенной помехозащищенности.

Известно нелинейное корректирующее устройство для повышения точности коррекции, без уменьшения запаса устойчивости, содержащее блок сигнатуры, вход которого подключен через блок выделения модуля сигнала . ошибки .к первому входу множительного блока и через первый усилитель к первому входу первого сумматора, второй сумматор, первый вход которого подключен к выходу множительного блока, а выход - ко второму входу первого сумматора, второй и третий усилители, причем выход блока сигнатуры через второй усилитель соединен со вторым выходом множительного блока, а через третий усилитель — co вторым входом второго сумматора (1 1.

Недостатком такого устройства является то, что в условиях действия 25 внешних помех значительно снижается точность нелинейного корректирующего устройства.

Известно нелинейное корректирующее устройство для динамических сис- 30 тем с ограничением при двухотороннем ограничении сигнала помехи с увеличением среднего значения управляющего сигнала, содержащее первый коммутатор, выход которого связан со входом элемента с ограничением, источ-. ник постоянного напряжения, подключенный ко входу первого коммутатора, элемент сравнения, входы. которого подключены ко входу гервого коммутатора и выходу элемента с ограничением, а выход через второй коммутатор ко входам первого и второго интеграторов, в цепь обратной связи которых включены выпрямительные элементы, выходы первого и второго коммутатора связаны с управляющими входами первого коммутатора, фиксатор периода изменения управляющего сигнала, третий коммутатор и третий интегратор, при этом выход третьего интегратора подключен к управляющему входу второго коммутатора, а вход — ко входам первого коммутатора и фиксатора пе риода изменения управляющего сигнала, выход которого через третий коммутатор связан со входами интегратора (2j.

Недостатком данного устройства является то, что в условиях интен951231 сивных помех в устройстве происходит недопустимо большой сдвиг фазы полезного сигнала.

Наиболее близким по технической сущности к изобретению является псевдолинейное корректирующее устройст- 5 во для повышения порядка астатизма, содержащее интегратор, блок выделения модуля, вход которого соединен со входами фильтра и первого реле, блок умножения, второй вход которого >Q через второе реле соединен с выходом фильтра, выход третьего реле через второй блок умножения соединен со вторым входом первого сумматора, второй сумматор, входы которого соедине- 5 ны соответственно с выходами первого и второго реле, а выход — co входами третьего реле и интегратора, выход которого соединен со вторым входом второго блока умножения. g3).

Однако при работе в шумах корректирующее устройство не может обеспечить необходимой точности.

Целью изобретения является повышение динамической точности при работе в шумах.

Поставленная цель достигается введением второго блока выделения модуля, трех аналоговых запоминающих элементов, двух формирователей управляющих импульсов, второго интегратора, источника опорного напряжения, линии задержки, сравнивающего устройства, квадратора и управля- 35 емого делителя напряжения, причем выход первого реле соединен с первым входом блока умножения, выход которого соединен со входом первого формирователя управляющих импульсов, пер- 4Q вый выход которого соединен с первым входом первого аналогового запоминающего элемента и с первым входом первого интегратора, а второй выход соединен с первым входом второго ана- 45 логового запоминающего элемента; вход второго блока выделения модуля соединен с выходом фильтра и с первым входом управляемого делителя напряжения, а выход соединен со вторым входом первого аналогового запоминающего элемента, выход которого соединен со вторым входом первого интегратора, выход которого соединен с первым входом сравнивающего устройства, второй вход которого через

55 второй аналоговый запоминающий элемент соединен с выходом первого блока выделения модуля, выход сравнивающего устройства через второй формирователь управляющих импульсов 60 соединен с первым входом третьего аналогового запоминающего элемента, а через линию задержки - с первым входом второго интегратора, второй вход которого соединен с источником 65 опорного напряжения,. а выход через третий аналоговый запоминающий элемент и квадратор соединен со вторым входом управляемого делителя напряжения.

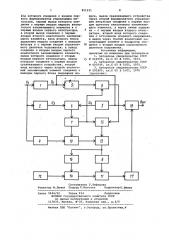

На чертеже представлена функциональная схема нелинейного корректирующего устройства, Схема включает в себя фильтр 1, первое реле 2, вход которого соединен со входом фильтра 1, второе реле 3, вход которого соединен с выходом фильтра 1, первый блок выделения модуля 4, вход которого соединен со входом реле 2, второй блок выделения модуля 5, вход которого соединен со входом реле 3, блок умножения б, первый вход которого соединен с выходом реле 2, а второй вход — с выходом реле 3, первый формирователь управляющих импульсов 7, вход кото.рого соединен с выходом блока умножения б, второй формирователь управляющих импульсов 8, первый аналоговый запоминающий элемент 9, вход которого соединен с выходом блока выделения модуля 5, а управляющий вход с первым выходом формировате,ля управляющих импульсов 7, второй аналоговый запоминающий элемент

10, вход которого соединен с выходом блока выделения модуля 4, а управляющий вход — co вторым выходом формирователя управляющих импульсов 7, третий аналоговый запоминающий элемент 11, управляющий вход которого соединен с выходом формирователя 8, источник опорного напряжения 12, первый интегратор 13, вход которого соединен с выходом аналогового запоминающего элемента

9, а управляющий вход — с первым выходом формирователя управляющих импульсов 7, второй интегратор 14, вход которого соединен с выходом источника опорного напряжения 12, а выход — со входом аналогового запоминающего элемента 11, сравнивающее устройство 15, первый вход которого соединен с выходом интегратора 13, а второй вход — с выходом аналогового запоминающего элемента

10, линию задержки 16, вход которой соединен с выходом сравнивающего устройства 15 и со входом формирователя управляВщих импульсов 8, а выход — с управляющим входом интегратора 14, квадратор 17, вход которого соединен с выходом аналогового за поминающего элемента 11, управляемый делитель .напряжения 18, вход которого соединен со входом блока выделения модуля 5, а управляющий вход с выходом квадратора 17.

Нелинейное корректирующее устройство работает следующим образом.

На фильтре 1 происходит сдвиг по фазе в сторбну отставания и измене951231

60

65 ние по амплитуде входного сигнала 0

На реле 2 и 3 происходит выделение знака сигналов U< и U соответственно. Блок умножения 6 вырабатывает прямоугольный разнополярный сигнал, изменение знака которого соответствует моментам начала и конца совпадения знаков прямоугольных сигналов

U и И4 . На формирователе управляющих импульсов 7 происходит выделение положительного и отрицательного перепадов выходного сигнала блока умножения 6, а также их задержка по времени. Сигнал, соответствующий отрицательному перепаду, подается на аналоговый запоминающий элемент 10 в качестве управляющего сигнала, что позволяет запоминать модуль сигнала

U с выхода блока выделения модуля

4 именно в момент окончания совпадения знаков сигналов U3 и U4 плюс некоторое время задержки ty, опреде-. ляемое формирователем управляющих импульсов 7. Сигнал, соответствующий положительному перепаду, подается на аналоговый запоминающий элемент 9 в качестве управляющего сигнала, что позволяет запоминать модуль сигнала U2 с выхода блока вы-деления модуля 5 в момент начала совпадения знаков сигналов U> и U4 плюс то же время задержки t> . Так как отношение запомненных таким образом на аналоговых запоминающих элементах 9 и 10 сигналов U4 и U пропорционально текущей частоте входного сигнала U то для формирования сигнала, соответствующего такому отношению на интеграторе 13, происходит интегрирование запомненного на аналоговом запоминающем элементе

9 сигнала U причем интегратор обнуляется тем же управляющим импульсом с первого выхода формирователя управляющих импульсов 7, который идет на управление аналоговым запоминающим элементом 9. На входы сравнивающего устройства 15 подается запомненное значение сигнала 11 и линейно-изменяющийся сигнал с выхода интегратора 13. В результате на выходе сравнивающего устройства 15 формируется импульс, передний фронт ,которого соответствует моменту начала совпадения знаков сигналов U3 и

U4 плюс время задержки t >, а задний фронт — моменту сравнения сигналов с выхода аналогового запоминающего элемента 10 и интегратора 13, т.е. длительность импульса с выхода сравнивающего устройства 15 пропорциональна текущей частоте входного сигнала U . Теперь необходимо дли4. тельность импульса преобразовать в постоянное напряжение, для чего интегратор 14 интегрирует эталонное напряжение с источника опорного напряжения 12, начиная с момента времени, соответствующего переднему фронту импульса с выхода линии задержки 16, которая задерживает импульс с выхода сравнивающего устройства 15 на время +, и кончая моментом времени, соответствующим заднему фронту импульса с выхода линии задержки 16. Амплитуда треугольного импульса на выходе интегратора 14 пропорциональна текущей частоте входного сигнала Uz и она запоминается по своему максимуму на аналоговом запоминающем элементе 11 по уп-равляющему импульсу с выхода формирователя управляющих импульсов 8.

Запомненное на аналоговом запоминающем элементе 11 значение сигнала, пропорциональное текущей частоте входного сигнала U„ возводится в квадрат на квадраторе 17 и подается в качестве управляющего сигнала на управляемый делитель напряжения 18, который изменяет амплитуду сигнала

U в соответствии с текущей частотой входного сигнала U Тем самым удается получить отдельно амплитудную характеристику нелинейного корректирующего устройства, зависящую, в основном, от числа квадраторов, введенных в устройство, и фазовую его характеристику, зависящую от фазовой характеристики фильтра 1 и задержек

tg и 14 . Поэтому введение такого нелинейного корректирующего устройства в замкнутую автоматическую систему может повысить динамическую точность системы (a 2 раза) .

Применение данного устройства обеспечивает возможность более эффективного подавления шумов без ухудшения качества переходного про. цесса. Это объясняется тем, что обеспечиваются условия построения амплитудной характеристики высокого порядка при наличии фазового сдвига меньше 180О.

Формула изобретения

Нелинейное корректирующее устройство, содержащее интегратор, блок выделения модуля, вход которого соединен с входами фильтра и первого реле, блок умножения, второй вход которого через второе реле соединен с выходом фильтра, о т л и ч а ю— щ е е с я тем, что, с целью повышения динамической точности, введены второй блок выделения модуля, три аналоговых запоминающих элемента, два формирователя управляющйх импульсов, второй интегратор, источник опорного напряжения, линия задержки, сравнивающее устройство, квадратор

:и управляемый делитель напряжения, причем выход первого реле соединен с первым входом блока умножения, вы951231

Составитель Г.Нефедова

Редактор М.Дылын Техред Т;Маточка КорректорО.Билак

Заказ 5944/52 Тираж 914 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5 филиал ППП "Патент", г.ужгород, ул.Проектная,4 ход которого соединен с входом пер- вого формирователя управляющих импульсов, первый выход которого соединен с первым входом первого аналогового запоминающего элемента и с первым входом первого интегратора, а второй выход соединен с первым входом второго аналогового запоминающего элемента, вход второго блока выделения модуля соединен с выходом фильтра и с первым входом управляе мого делителя напряжения, а выход соединен с вторым входом первого аналогового запоминающего элемента, выход которого соединен с вторым входом первого интегратора, выход которого соединен с первым входом .сравнивающего устройства, второй вход которого через второй аналоговый запоминающий элемент соединен с выходом первого блока выделения модуля, выход сравнивающего устройства через второй формирователь управляющих импульсов соединен с первым входом третьего аналогового запоминающего элемента, а через линию задержки - с первым входом второго интегратора, второй вход которого соединен с источником опорного напряжения, а выход через третий аналоговый запоминающий элемент и квадратор сое10 динен с вторым входом управляемого делителя напряжения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

15 Р 610059 кл.G 05 В 5/01, 1973.

2. Авторское свидетельство СССР

9 603949, кл.G 05 В 5/01, 1975.

3, Авторское свидетельство СССР

Р 591809, кл.С 05 В 5/01, 1976

,прототип).