Устройство для отладки программ

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик р>951314 (61) Дополнительное к авт. свид-ву (22) Заявлено 2309.80 (21) 2984254/18-24

Р )М К з с присоединением заявки М (23) Приоритет

G 06 F 11/28

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 681 ° 3 (088,8) Опубликовано 15.08,82. Бюллетень Й9 30

Дата опубликован я описания 150882

Б.А. шаповалов, м.Ф. новиков, ю.Ф. шелюхин,)А.В;-Пилюли, (72) Авторы изобретения

О.А. Козлов и Б.Н. Сычков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ

Изобретение относится к вычисли тельной технике и может найти применение при автоматизированной отладке программ специализированных цифровых систем управления в реальном масштабе времени.

Известно устройство для отладки программ, содержащее оперативную память, регистр числа, регистр адреса, регистр обмена, накопитель на магнитной ленте, перфоратор и блок клавиатуры (1), Недостатком этого устройства является невысокая скорость отладки программ.

Наиболее близким к изобретению по технической сущности является устройство для отладки программ, содержащее оперативную память

ОП (НЗБ), соединенную информационными входом и выходом с первым выходом и входом блока приема и выдачи чисел и команд, второй выход которого является информационным выходом устройства, блок формирования адреса, соединенный выходом с адресным входом ОП, а первым входом — с адресным входом устройства, блок управления, первый и третий входы которого являются входами команд, а выход подключен к входу обращения

ОП (2) .

Недостаток этого устройства заключается в том, что оно не позволяет проводить отладку основной программы в процессе ее выполнения, так как требует остановки основной программы на время ее коррекции.A это не дает возможности: проводить отладку программ при включении реальной аппаратуры в контур моделирования из-за того, что остановка отлаживаемой программы приводит к появлению дополнительных запаздываний и искажению процесса моделирования.

Цель изобретения — сокращение времени отладки программ при работе в реальном масштабе времени.

Укаэанная цель достигается тем, что в устройство, содержащее блок памяти, первый регистр числа, первый регистр адреса, блок управления, содержащий генератор импульсов,элемент ИЛИ, два элемента И, причем первые вход и выход первого регистра числа подключены к первым выходу и входу блока памяти, второй вход которого подключен к выходу первого регистра адреса, первый вход которого является первым ад951314 ресным входом устройства, второй выход первого регистра числа является первым информационным выходом устройства, третий вход блока памяти.подключен к первому выходу генератора импульсов, вход которого подклЮчен к выходу элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам первого и второго элементов И, первый вход первого элемента И является первым входом команд обращения устрбйства, первый вход второго элемента И является вторым входом команд обращения устройства введены второй регистр числа, второй регистр адреса, 10

15 блок приоритетного подключения каналов, содержащий два элемента И-НЕ, два D-триггера, два элемента И,два.формирователя импульсов, причем пер; вые вход и выход второго регистра числа подключены соответственно к второму выходу и четвертому входу блока памяти, пятый вход которого

20 подключен к выходу второго регистра и четвертого элементов И подключены соответственно к Q u Q-выходам второго триггера, D-вход которого объединен с вторым входом второго элемента И-HE и является вторым входом запросов устройства.

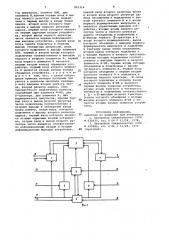

На фиг.1 приведена функциональная схема устройства; на фиг.2 блок управления, схема; на фиг.3

65 адреса, первый вход которого является вторым адресным входом устройства, вторые вход и выход второго регистра числа являются соответственно информационным входом и вторым информационным выходом устройства, тре тий вход второго регистра числа и второй вход второго регистра адреса объединены и подключены к выходу третьего элемента И и к входу первого формирователя импульсов и является управляющим выходом устройства, вторые входы первого регистра числа и первого регистра адреса объединены и подключены к Q-выходу первого D-триггера и к входу второго формирователя, выход которого 40 объединен с выходом первого формирователя импульсов и подключен к третьему входу блока управления, второй выход которого подключен к

С-входам первого и второго тригге- 45 ров, S-входы которых подключены соответственно к выходам первого и второго элементов И-НЕ, первые входы которых объединены и подключены к выходу четвертого элемента И,первый вход которого объединен с первым входом третьего элемента И и подключен к :Q-выходу первого триггера, D-вход которого подключен к второму входу первого элемента И-НЕ и является первым входом запросов устройства, вторые входы третьего блок приоритетного подключения ка— налов, схема .

Схема устройства (фиг.1) нключае: регистр 1 числа, регистр 2 адреса, блок 3 памяти, блок 4 управления, блок 5 приоритетного подключения каналов, регистр 6 адреса, регистр

7 числа, информационные выходы 8, 9 и вход 10, адресные входы 11 и 12, входы 13 и 14 команд обращения, входы 15 и 16 запросов на доступ в блок памяти, управляющий выход 17, элементы 18 и 19 И, элемент ИЛИ 20, генератор 21 импульсов, элементы 22 и 23 И-HE, D-триггеры 24 и 25, элементы 26 и 27 И, формирователи 28 . и 29 импульсов. Устройство работает совместно с ЦВМ и специализированным вычислительным устройством (СВУ).

Специализированное вычислительное устройство является, в частности, цифровой управляющей частью системы управления (БЦВМ вЂ” бортовая цифровая вычислительная машина). Оно реализует программу обработки исходной информации и вырабатывает управляющие сигналы на объект управления, а также выполняет другие функции.

Перед началом отладки основная и служебная программы через регистры

1 и 2 вводятся в OII. Отладка основ— ной программы проводится с помощью служебной программы, которая предназначена для коррекции участков программы или отдельных команд и операндов основной программы. В устрои— стве имеются два канала доступа в

ОП: канал СВУ основной программы и канал ЦВМ служебной программы. Подключение каналов к ОП осуществляется блоком 5 по приоритетному принципу следующим образом. При операциях выборки из памяти от каналов поступают запросы «а доступ в ОП. Канал

СВУ имеет приоритет на доступ к памяти по отношению к каналу ЦВМ, т.е. при одновременном появлении запросов от СВУ и ЦВМ блок 5 подключает к памяти канал основной программы.

Канал служебной программы находится в ожидании подключения к ОП до тех пор, пока канал о".íîâíîé программы не снимет свой запрос. Это происходит при завершении СВУ операций цикла выборки из памяти и начала операций исполнительного цикла.

По сигналу конца цикла выборки из памяти блок 5 подключает к ОП канал служебной программы и ЦВМ начинает выполнение операций выборки из ОП. По следующему запросу от

СВУ блок 5, дождавшись сигнала окончания цикла памяти, отключает ка— нал служебной программы и вновь подключает к ОП канал основной программы. Во время выполнения основной программы при операциях выборки числа или команды из ОП на

951314 управляющий вход 16 от СВУ поступает запрос на доступ в ОП. По адресному входу 12 на регистр б подается адрес считываемой ячейки ОП, а по входу

14 на блок — команда обращения. По сигналу конца цикла памяти, поступающему с второго выхода блока 4 на третий вход блока 5, в последнем вырабатываются сигналы разрешения, поступающие с его первого выхода на регистры б и 7, и управления, поступающие с третьего выхода блока 5 на третий вход блока 4. Сигналы разрешения подключают регистры

6 и 7 к первым адресному входу и информационным входу и выходу ОП.

Сигналы управления открывают первыи вход блока 4, и команда обращения с входа 14 поступает на блок 4. По этой команде БУ вырабатывает сигналы управления ОП для считывания информации, поступающие с первого 20 выхода блока 4 на управляющий вход блока 3 памяти. Информация, считываемая из ОП, через регистр 7 выводится на информационный выход 9 устройства. 25

При выполнении служебной программы при операциях считывания или записи в ОП от ЦВМ на вход 15 устройства поступает запрос на доступ в память. Он находится в ожидании до окончания цикла выборки из ОП, выполняемого СВУ. Пбсле завершения

СВУ цикла выборки оно снимает сигнал запроса, поступающий на первый вход блока 5. А по сигналу конца цикла памяти, посылаемому с второго выхода блока 4 на третий вход блока 5,последний формирует сигналы разрешения, поступающие с его второго выхода на регистры 1 и 2 и управляющий выход

17 устройства. Одновременно с третье- 40

ro выхода блока 5 поступает сигнал, открывающий второй вход блока 4. При появлении сигнала на выходе 17 ЦВМ посылает команду обращения на вход

13 Устройства и адрес ячейки ОП на 45 вход 11. По команде обращения в блоке 4 вырабатываются сигналы управления ОП для считывания при записи информации, посылаемые с первого выхода БУ на управляющий вход ОП.

Адрес с выхода регистра 2 подается на второй адресный вход блока 3.Считываемая информация с второго информационного выхода ОП через первый вход и второй выход регистра 1 выводится на выход 8 устройства. При записи информация с входа 10 устройства через второй вход и первый выход регистра 1 поступает на второй информационный вход блока 3. При приеме запросов на доступ в память 60 от ЦВМ и СВУ или только запроса от

СВУ сигнал управления (ЗА), приходящий с блока 5 на третий вход блока

4, пропускает через элемент И 19 сигнал обращения от СВУ, поступающий 65 на вход блока 4 (фиг.2) . Этот сигнал через элемент 20 ИЛИ запускает генератор 21 импульсов (ГИ). Сгенерированные импульсы с первого выхода блока 4 поступают в оперативную память (ОП) и управляют процессами считывания и записи. С второго выхода блока 4 поступает сигнал конца цикла памяти. При приеме запроса от

ЦВМ на доступ в память (и отсутствии запроса от СВУ) сигнал управления (ЗВ), поступающий на третий вход блока 4, разрешает прохождение сигнала с второго входа блока 4 через элемент И 18. На второй вход блока 4 приходит сигнал обращения от

ЦВМ, по которому аналогично указанной последовательности формируются сигналы управления ОП и сигнал Конец цикла памяти . Блок 5 предназначен для приоритетного подключения кана лов ЦВМ и СВУ через регистры адреса и числа к оперативной памятй . Канал

СВУ имеет приоритет по отношению к каналу ЦВМ.

При одновременном поступлении запросов на доступ в ОП от ЦВМ (вход

15) и СВУ (вход 16) по сигналу конца предыдущего цикла памяти, приходящего с блока 4, в блоке 5 вырабатывается сигнал разрешения загрузки регистров РА1 и Р41, обслуживающих СВУ. Одновременно с сигналом разрешения с третьего выхода БППК на блок 4 поступает сигнал управления (ЗА). Запрос от ЦВМ находится в ожидании до тех пор, пока не будет снят сигнал запроса от СВУ. Таким образом, запрос от ЦВМ обслуживается при условии снятия запроса от СВУ и поступлении сигнала Конец цикла памяти с блока 4. При этом с второго выхода блока 5 подается сигнал, разрешающий загрузку регистров РА2 и Р42 и также поступающий на выход

17 устройства. С третьего выхода блока 5 выходит сигнал ЗВ. При получении ответа на запрос на доступ в ОП с выхода 17 устройства ICBM посылает команду обращения на вход

13 и адрес ячейки памяти на вход 11.

Параллельное выполнение основной и служебной программ позволяет производить отладку основной программы во время ее работы. Следовательно, устройство дает возможность вести отладку программ при моделировании с реальной аппаратурой автоматических и полуавтоматических систем управления в реальном масштабе времени.

Формула из обрет ения

Устройство для отладки программ, содержащее блок памяти, первый регистр числа, первый регистр адреса, блок управления, содержащий генера951314 тор импульсов, элемент ИЛИ, два элемента И,причем первые вход и вы- ход первого регистра числа подключены к первым выходу и входу блока памяти, второй вход которого подключен к выходу первого регистра з адреса, первый вход которого является первым адресным входам устройства, второй выход первого регистра числа является первым информационным выходом устройства, третий вход 10 блока памяти подключен к первому выходу генератора импульсов, вход которого подключен к выходу элемента

ИЛИ, первый и второй входы которого, подключены соответственно к выходам первого и второго элементов И, первый .вход первого элемента И является, первым входом команд обращения устройства, первый вход второго элемента И является вторым входом команд обращения устройства, о т л и ч а ющ е е с я тем, что, с целью сокращения времени отладки программ при работе в реальном масштабе времени, в него введены второй регистр числа, второй регистр адреса, блок приоритетного подключения каналов, содержащий два элемента И-НЕ, два

D-триггера, два элемента И, два формирователя импульсов, причем первые вход и выход второго регистра числа подключены соответственно к второму выходу и четвертому входу блока памяти, пятый вход которого подключен к выходу второго регистра адреса, первый вход которого является вторым адресным входом устройства, вторые вход и выход второго регистра числа являются соответственно информационным входом и вторым информационным выходом устройства, 40 третий вход второго регистра числа и второй вход второго регистра адреса объединены и подключены к выходу третьего элемента И и к входу первого формирователя импульсов и является управляющим выходом устройства, втсрые входы первого регистра числа и первого регистра адреса объединены и подключены к

Ц-выходу первого Э-триггера и к входу второго формироватеЛя, выход которого объединен с выходом первого формирователя импульсов и подключен к третьему входу блока управления, второй выход которого подключен к

С-входам первого и второго триггеров, Я -входы которых подключены соответственно к выходам первого и второго элементов И-НЕ, первые входы которых объединены и подключены к выходу четвертого элемента И, первый вход которого объединен с первым входом третьего элемента И и подключен к

Я-выходу первого триггера, Э. -вход которого подключен к второму входу первого элемента И-HE и является первым входом запросов устройства, вторые входы третьего и четвертого элементов И подключены соответственно к Q — и G -выходам второго триrrepa, р-вход к от орого объеди нен с в т срым входом второго элемента И-НЕ н является вторым входом запросов устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 630630, клг G 06 F 11/28, 1978.

2. Авторское свидетельство СССР

9 690482, кл. G E 11/28, 1979 (прототип .

951314

И них At сне и амююя

Kit ию юлю Й яаиимь ав цен

Составитель A. Зинькова

Редактор К. Волоцук .Техред 3. Палий Корректор О. Билак

Заказ 5951/56 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

jPFllgllC НО fa77

tuttut . Квне цикга ианиец. м )Ь м

/ имюв кн юа и кюти

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4