Устройство для сопряжения процессора с многоблочной памятью

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.1080 (21 ) 3009270/18-24 (54) М. Кд.з с присоединением заявки N

G F 13/06

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (S3) УДК б 81. 325 (088. 8) Опубликовано 1508.82. Бюллетень ¹ 30

Дата опубликования описания 1508,82 (72) Авторы изобретения

A.Ï. Губанов, С.С. Крыкин, Е.M. Луне и Б.С. Турышев ской (71) Заявитель

Специальное конструкторско-техническ техники (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА

С МНОГОЬЛОЧНОЙ ПАМЯТЬЮ

Изобретение относится к вычислительной технике и может быть использовано для увеличения объема оперативной памяти при построении цифровых систем обработки данных на базе мини (микро-) -ЭВМ.

Известно устройство управления памятью со страничной организацией, содержащее регистры адреса страниц, регистры признака страниц, сумматоры и коммутатор (1) .

Недостатками устройства являются большой объем оборудования и невысокое быстродействие за счет потерь времени в каждом цикле обращения к памяти на преобразование виртуального адреса в физический.

Наиболее близким к предлагаемому по технической сущности является устройство для связи запоминающего и арифметического устройств при формате адреса запоминающего устройства, превышающего формат адреса арифметического устройства, содержащее коммутатор, последовательно соединенные дешифратор, шифратор, регистры, выходЫ которых подключены к группе адресных входов запоминающего устройства и к управляющим входам коммутатора (2) .

Однако известное устройство не обеспечивает возможность работы од,новременно с разными областями памяти, находящимися в разных ее страницах. без переключения регистра номера массива, что снижает быстродействие и ограничивает функциональные возможности устройства.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для сопряжения процессора с многоблочной памятью, содержащее регистр номера массива и блок памяти, входы/выходы которого являются информационными входами/выходами устройства, введены блок дешифраторов, группа канальных приемо-передатчиков, дешифратор адреса, триггер, дешифратор управляющих сигналов,первый и второй входы которых подключены к группе управляющих входов/выходов устройства, а третий вход

25 к выходу триггера, синхровход которого подключен к группе управляющих входов/выходов устройства, а информационный вход — к выходу дешифратора адреса, группа входов

30 которого соединена с группой вы951315 ходов группы канальных приемо-передатчиков и группой входов регист- ра номера массива, группа выходон которого соединена с группой входов блока дешифраторов и первой группой нходов группы канальных приемо-передатчиков, вторая группа входов которых соединена с группой управляющих входов/выходов устройства, группа выходов блока дешифраторов соединена с группой упранляющих нходов блока памяти, второй выход дешифратора управляющих сигналов соединен с входом группы канальных приемо-передатчиков.

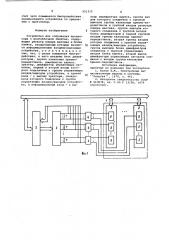

На фиг.1 показана блок-схема устройства! на фиг.2 — блок-схема блока управления, Устройство содержит входы/выходы

1 блоков памяти, блок 2 управления, регистр 3 номера массива, блок дешифраторов 4, блоки 5 памяти, банки

6 памяти, группы выходов 7 регистра номера массива 3, канальные приемопередатчики 8, дешифратор 9 адреса, триггер 10, дешифратор 11 управляющих сигналов.

Устройство работает следующим образом.

Каждый из и блоков 5 памяти, содержащий m банков 6 памяти, имеет максимальную емкость, соответствующую формату адресного слова процессора. Каждый из банков 6 памяти имеет управляющий вход, с помощью которого данному банку либо разрешается, либо запрещается работа с магистралью Общая шина . В связи с тем, что каждый банк 6 памяти управляется автономно, возникает возможность подключать определенный набор m банков 6 из и блоков 5 памяти к магистрали Общая шина за один цикл обращения процессора с помощью блока управления 2 и регистра 3 номера массива. B зависимости от передаваемого в регистр 3 номера массива кода к магистрали подключается та или иная комбинация m банков. 6 из и блоков 5 памяти. При этом возможны только такие комбинации банкон 6 памяти, в которых из и одноименных банков, относящихся к разным блокам памяти, подключен только один. После прохождения по магистрали сигнала установки в нуль регистр 3 номера массива устанавливается в нулевое состояние. При этом по первым выходным шинам каждого из дешифраторов 4 поступают упранляющие сигналы, которые разрешают работу с магистралью только банкам первого блока памяти. Смена подключенной к магистрали комбинации банков 6 памяти производится путем изменения кода на выходах регистра 3 номера массива. Запись кода в регистр 3 номера массива производится

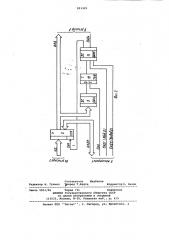

65 раль, При поступлении на вход ДШУС сигнала СИД2 дешифратор формирует синхрониэирующий импульс записи

СИЗп, по которому в регистре 3 номера массива произнодится запись очередного поступающего кода.

Таким образом, с помощью заявляемого устройства к магистрали Общая шина процессора можно подключать различные комбинации из m банков памяти . Это снижает частоту обращения к регистру, управляющему памятью (регистр 3 номера массива предлагаемого устройства) и обеспечивает более гибкое использование памяти объема, превышающего 2" слов, за йрограммно, с помощью отдельной ко-, манды пересылки. При этом, с помощью дешифраторов 4 к магистрали подключается необходимая комбинация банков

6 из имеющихся и блоков 5 памяти.

Контроль подключенной комбинации банков памяти осуществляется при чтении кода с выходов регистра 3 номера массива через блок 2 управления в процессор. Максимальная емкость

10 каждого блока памяти может быть не более 2 слов, где N — формат adpecного слова процессора. Блок управления 2 предназначен для сопряжения регистра 3 номера массива с магист15 ралью Общая шина . Выполнение блока 2 управления определяется типом и структурой магистрали. Поэтому его конкретная реализация для разных

ЭВМ может быть различной.

70 В состав блока 2 управления входят канальные приемо-передатчики (КПП), дешифратор адреса (ДША), триггер Устройство выбрано (ТУВ) и дешифратор управляющих сигналов (ДШУС).

Коды адресов и данные для дешифрации адреса в ДША и записи в регистр 3 поступают по шинам адреса данных магистрали (ШАДМ) на входы КП!!. С выходов КПП коды адресов и данные по шинам адреса данных (ШАД) поступают на входы ДША.и регистра 3 номера массива. Передача из регистра 3 номера массива установленного в нем кода в

ШАЛМ производится через КПП по шинам данных (ШД). По синхронизирующему импульсу адреса (СИА) при совпадении кода адреса, поступающего на вход

ДША, с кодом адреса устройства для управления памятью триггер Устройство выбрано устанавливается в

40 1 состояние и разрешает работу

ДШУС, На вход дешифратора 11 управ— ляющих сигналов поступают синхронизирующие импульсы данных магистрали

СИД1 (ввод данных) и СИД2 (вывод

45 данных). При поступлении на вход

ДШУС сигнала СИД1 дешифратор Форми— рует сигнал СИМ, по которому производится передача кода управления регистра 3 номера массива в магист951315 счет чего повыаается быстродействие; предлагаемого устройства по сравне- нию с прототипом.

Формула изобретения

Устройство для сопряжения процессора с многоблочной памятью, содержащее регистр номера массива и блоки памяти, входы/выходы которых являются информационными входами/выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены блок дешифраторов, группа канальных приемопередатчиков, дешифратор адреса, триггер, дешифратор управляющих сигналов, первый и второй входы которого подключены к группе управляющих входов/выходов устройства, а третий вход — к выходу триггера, синхровход которого подключен к группе управляющих входов/выходов устройства, а информационный вход — к выходу дешифратора адреса, группа вхо дов которого соединена с группой выходов группы канальных приемо-передатчиков и группой входов регистра номера массива, группа выходов ко5 торого соединена с группой входов блока дешифраторов и первой группой входов группы канальных приемопередатчиков, вторая группа входов которых. соединена с группой управ10 ляющих входов/выходов устройства, группа выходов блока дешифраторов соединена с группой управляющих входов блока памяти, второй выход дешифратора управляющих сигналов соединен с входом группы канальных приемо-передатчиков.

Источники информации, принятые во внимание при экспертизе

1. Каган Б.М., Электронные вычислительные машины и системы. Энергия, 1979, с. 461.

2. Авторское свидетельство СССР

9 643878, кл. G 06 F 13/06, 1979 (прототип) .

951315 р (ЫУп2 / g

Го ш пи1 у тю1шмин у

Заказ 5951/56 Тираж 731 Подписное

ВНИИПИ Государственного кбмитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Составитель Щербаков

Редактор А. Гулько ехред Т.Фанта Корректор О. Билак