Умножитель частоты

Иллюстрации

Показать всеРеферат

CoIo3 Советских

Социалистических респубпнк

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВХ ()951638 (61) Дополнительное к авт. спид-ву N 860275 (22) Заявлено 23. 05. 80 (2! )2934126/18-09 с присоединением заявки ¹ (23) Приоритет— (5l)M. Кл.

Н 03 8 19/00

Государственный комитет ио делан изобретений и открытий

Опубликовано 15. 08. 82. Бюллетень №30

Дата опубликования описания 15. 08. 82 (53) УДК621. 374. .44(088.8) Л, М. Ковалев, Н. ф. Парков, M. В. Лей овскии, Ж. Н. Шашкова и Ю. О. Сазоненко

М

:)л1 ; :,-и:.:. с

Могилевский машиностроительный институт (72) Авторы изобретения (7!) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к вычислительной технике и может быть использовано в качестве умножителя частоты сети для устройств с непосредственной связью с сетью, а также для управления цифровыми пусковыми органами релейной защиты объектов электрических станций или электрических цепей.

По основному авт.св. М 860275, известен умножитель частоты, содержащий фазовращатель, выход которого подключен к первым входам сумматора и вычитателя, а вход соединен с их вторыми входами, пять компараторов, выходы которых подключены к соответствующим входам элемента ИЛИ, при этом первый вход первого компаратора соединен с первым входом второго компаратора, второй вход первого компаратора соединен с первым входом третьего компаратора, а первый вход четвертого компаратора соединен с первым входом пятого компаратора, между выходом фазовращателя и вторым входом первого компаратора включен первый выпрямитель, между выходом сумматора и первым входом первого компаратора включен второй выпрямитель, между выходом вычитателя и первым входом четвертого компаратора включен третий выпрямитель а между выходом фазовращателя и вторым входом второго компаратора включен четвертый выпрямитель, при этом вторые входы второго, третьего и чет" вертого компараторов соединены между собой,а первый вход третьего компаратора соединен с вторым входом пято го компаратора 1 ).

Однако известный умножитель частоты имеет недостаточно высокий коэф фициент умножения.

Цель изобретения - повышение коэффициента умножения.

951638

Для достижения цели в умножитель частоты, содержащий фазовращатель, выход которого подключен к первым входам сумматора и вычитателя, а вход соединен с их вторыми входами, пять % компараторов, выходы которых подключены к соответствующим входам- элемента ИЛИ, при этом первый вход первого компаратора соединен с первым входом второго компаратора, второй вход первого компаратора соединен с первым входом третьего компаратора, а первый вход четвертого компаратора . соединен с первым входом пятого компаратора,. между выходом фазовращателя и вторым входом первого компаратора включен первый выпрямитель, между вы ходом сумматора и первым входом первого компаратора включен второй выпрямитель, между выходом вычитателя и первым входом четвертого компаратора включен третий выпрямитель, а между . выходом фазовращателя и вторым входом второго компаратора включен четвертый выпрямитель, при этом вторые входы 2s второго, третьего и четвертого компараторов соединены между собой, а первый вход третьего компаратора соединен со вторым входом пятого компаратора, между выходом каждого из вы- зв прямителей и соответствующим дополнительным входом элемента ИЛИ включен один из четырех введенных дополнительных компараторов, вторые входы которых соединены между собой, а меж- 35 ду входом фазовращателя и точкой соединения вторых входов дополНительных компараторов введены последовательно соединенные амплитудные детектор и делитель напряжения. 40

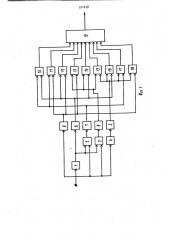

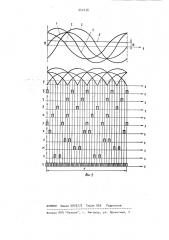

На фиг. 1 приведена структурная электрическая схема предлагаемого умножителя частоты;.на фиг. 2 - временные диаграммы его работы.

Умножитель частоты содержит фазовращатель 1, сумматор 2, вычитатель

3, амплитудный детектор 4, делитель

5 напряжения, выпрямители 6-9, компараторы 10-18, элемент ИЛИ 19.

Умножитель частоты работает следующим образом.

Фазовращатель 1 преобразовывает синусоиду в косинусоиду, сумматор 2 складывает синусоиду и косину оиду, вычитатель 3 вычитает из синусоиды косинусоиду, амплитудный детектор 4 формирует постоянный сигнал, равный модулю амплитуды входного сигнала, который с помощью делителя 5 напряжения уменьшается до величины а=

=PU Q sin 11,25

Таким образом, получается группа из пяти сигналов (см.фиг.2а). Входной сигнал и сигналы с выходов фазовращателя 1, сумматора 2, вычитателя 3 выпрямляются выпрямителями 6-9 (см. Фиг. 2б ). Сигналы с выходов выпрямителей 6-9 и сигнал с выхода делителя 5 напряжения подаются попарно на компараторы 10-18, которые формируют узкие импульсы в момент равенства поданных сигналов на их входах (см.фиг.2в,г,д,ж,з,к,л.м,н ). Сигналы с выходов компараторов 10-18 поступают на входы элемента ИЛИ 19, с выхода которого снимается сигнал в виде узких импульсов с частотой в 32 раза бояьше, чем частота входного сигнала (см.фиг.2п).

Исполь зова ние и редлагаемого изобретения в сравнении с известным позволяет увеличить коэффициент умножения вдвое.

Формула изобретения

Умножитель частоты по авт.св.

Ю 860275, отличающийся тем, что, с целью повышения коэффициента умножения, между выходом каждого из выпрямителей и соответствующим дополнительным входом элемента

ИЛИ включен один из четырех введенных дополнительных компараторов, вторые входы которых соединены между собой, а между входом фазовращателя и точкой соединения вторых входов дополнительных компараторов введены последовательно соединенные амплитудный детектор и делитель напряжения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

И 860275, кл. Н 03 В 19/00, 1980 (прототип).