Демодулятор импульсного сигнала,модулированного методом расщепленной фазы

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистические

Республик (ii) 951690

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свитт-ву

Ф (22) Заивлено 02. 10. 80 (21) 2989053/18" 21 (51)м. Кл. с присоединением заявки М

Н 03 1(9/04

3ЪоударствеииыЯ комитет

СССР ио делам иаабретеииЯ и открытиЯ (23)приоритет(53) УДК621 ° 376 ° .55(088.8) Опубликовано 15. 08. 82. Ьктллетень Xi 30

Дата опубликования описания 17.08.82 (72) Автор изобретения

Ю. Г. Бай ков

).

1

s.1;„ (71) Заявитель (54) ДЕМОДУЛЯТОР ИМПУЛЬСНОГО СИГНАЛА, МОДУЛИРОВАННОГО МЕТОДОМ РАСЩЕПЛЕННОЙ

ФАЗЫ!

Изобретение относится к импульсной технике и может быть использо" вано при создании кабельных линий связи с трансформаторной развязкой.

Известно устройство, содержащее элемент И и триггер 1 1j.

Известно устройство, содержащее интегратор, первый вход которого соединен с шиной. входного сигнала, триггер, выход которого соединен с то шиной выходного информационного сиг" нала,,элемент И, выход которого соединен с шиной выходного тактового сигнала 1 2), Недостатком известных устройств является низкая помехозащищенность.

Цель изобретения - повышение помехозащищенност.

Поставленная цель достигается тем, что в устройство, содержащее интегра" 20 тор, первый вход которого соединен с шиной входного сигнала, триггер, выход которого соединен с шиной выходного информационного сигнала, эле2 мент И, выход которого соединен с шиной выходного тактового сигнала, введены два компвратора, источник по- ложительного смещения, источник отрицательного смещения и формирователь уровней, причем выход интегратора соединен.с инвертирующим входом пер-вого компаратора и с неинвертирующим входом второго компараторв, выходы которых соединены с соответствующими входами элемента И и триггера, выход которого через формирователь уровней соединен с вторым входом интегратора, неинвертирующий вход первого компаратора соединен через источник положительного смещения с общей шиной, инвертирующий вход второго компаратора соединен через источник отрицательного смещения с общей шиной.

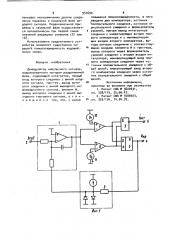

На фиг. 1 представлена схема демодулятора импульсного сигнала, модулированного методом расщепленной фазы; на фиг. 2 " временные диа1.раммы, поясняющие его работу.

95169

Демодулятор импульсного сигнала, модулированного методом расщепленной фазы, содержит интегратор 1, первый вход которого соединен с шиной 2 входного сигнала, триггер 3, выход кото- 5 рого соединен с шиной 4 выходного информационного сигнала, элемент 5 И, .выход которого соединен с шиной 6 выходного тактового сигнала, выход интегратора 1 соединен с инвертирующим входом компаратора 7 и с неинвертирующим входом компаратора 8, выходы каждого из которых соединены с соответствую" щими входами элемента 5 И и тригге" ра 3, выход которого через формирова- >> тель 9 уровней соединен с вторым вхо дом интегратора 1, неинвертирующий вход компаратора 7 соединен через источник 10 положительного смещения с общей шиной, инвертирующий вход компаратора 8 соединен через источник 11 отрицательного смещения с общей шиной.

На шину 2 входного сигнала с внешнего источника поступает кодовый

25 сигнал, представленный кодом с расщепленной фазой. !

На фиг. 2а на примере кодовой последовательности 001101 изображен

30 сигнал, закодированный двухфазным кодом с расщепленной фазой, Этот сигнал квантован во времени и может принимать положительный или отрицательный уровень. Передача информации двухфазным кодом осуществляется по тактам.

При этом каждой "1" кодовой последовательности соответствует переход с верхнего уровня на нижний, расположенный в центре соответствующей разрядной позиции, а каждому "0" - переход с

40 нижнего уровня на верхний, также расположенный в центре разрядной позиции.

При передаче последовательности ну" лей или последовательности единиц используются добавочные переходы, рас 4 положенные на границах соответствующих разрядных позиций. Интеграл по текущему значению времени от этого сигнала соответствует пилообразной функции (инверсная форма показана на фиг. 2б), которая колеблется в положительной области при передаче единиц и в отрицательной области - при передаче нулей и обращается в ноль на границах тактов.

Ы

Сигнал на выходе интегратора изменяется под воздействием сигнала 2а, поступающего на шину 2 устройства, 0 4 и сигнала 2в, поступающего по цепи обратной связи. Выбор параметров схемы производится так, чтобы установившееся,значение составляющей этого сигнала, соответствующее сигналу обратной связи, и приращение составляющей, соответствующей входному кодовому сигналу, за время равное 1/4 Т, где Т - длительность периода тактовой частоты, были равны по абсолютным значениям порогам срабатывания компараторов 7 и 8.

Устройство работает следующим образом.

В момент времени, соответствующий началу очередного такта, состояния триггера 3 (фиг. 2 r) и сигнала обратной связи (фиг. 2 в ) соответствуют значению предыдущего разряда информации, а сигнал на выходе интегратора 1(фиг, 2,б) равен нулю. В течение такта этот сигнал достигает предельного отклонения от нулевого значения и вновь возвращается к нулю со знаком, соответствующим значению текущего разряда поступающей информации.

При этом он выходит за пределы, определяемые уровнями срабатывания компараторов 7 и 8 (на фиг. 2,б)обозначены пунктиром), что приводит к формированию сигналов (фиг. 2,д, е) на их выходах. Благодаря объединению этих сигналов на элементе 5 И формируется последовательность выходных тактовых импульсов (фиг. 2,ж). Эти же сигналы, воздействуя на входы триггера 3, устанавливают его в состояние, соответствующее значению текуц его разряда информации (фиг. 2,r), если это значение не совпадает со значением предыдуц его разряда. Состояние триггера 3 передается на шину 4 и через формирователь 9 - на второй вход интегратора 1. Таким образом к началу следующего такта исходное состояние устройства восстанавливается.

При поступлении длинной последовательности единичйых или нулевых разрядов состояние триггера сохраняется неизменным, а сигнал обратной связи фиксирует на выходе интегратора средний уровень, относительно которого совершаются тактовые колебания его выходного сигнала, Значение этого уровня (s соответствии с указанными выше условиями выбора параметров ) совпадают с уровнем срабатывания соответствующего компаратора. Это обеспечивает неограниченно долгое сохранение привязки к начальной фазе кодового сигнала. Первоначальная привязка к начальной фазе осуществляется автоматически при первой смене значений разрядных символов (01 или

1O).

Использование предлагаемого устройства позволяет существенно повысить помехозащищенность кодовой . линии связи.

Формула изобретения

Демодулятор импульсного сигнала, модулированного методом расщепленной фазы, содержащий интегратор, первый вход которого соединен с шиной входного сигнала, триггер, выход которого соединен с шиной выходного ин" формационного сигнала, элемент И, выход которого соединен с шиной выходного тактового сигнала, о т л ич а ю шийся тем, что, с целью

51690 6 повышения помехозащищенности, в него введены два компаратора, источник положительного смещения, источник отрицательного смещения и формирователь

S уровней, причем выход интегратора соединен с инвертирующим входом первого компаратора и с неинвертирую" щим входом второго компаратора, выходы которых соединены с соответствующими входами элемента И и триггера, выход которого через формирователь уровней соединен с вторым входом интегратора, неинвертирующий вход первого компаратора соединен через источник положительного .смещения с об" щей шиной, инвертирующий вход второ" го компаратора соединен через источник отрицательного смещения с общей шиной.

20 Источники информации, принятые во внимание при экспертизе

1. Патент США И 3820031, кл. 32М119ф 25а06.47.

2. Патент СИА и 3506923, кл. 329/104, 14.0ч.70. 1

951690

Составитель Н. Коновалов

«Ре8актоо Л. Веселовская Техре8 К "ы4ьо Корректор А, Дзятко

Заказ 5973/75 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра шская наб. а. 4//»5

«

«3» «ъ.л.»»».В «»е в..В»«».й» « А»8 с, Филиал ППП Патент, r. Ужгород, ул. Проектная, ч