Устройство для исправления ошибок в дискретной информации

Иллюстрации

Показать всеРеферат

Союз Советскии

Социапистическиз

Республик

ОП ИСАНИ Е (ц951740

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к авт. саид-ву 14 860335 (22)Заявлено 11.07.80(2!) 2957199/18-09 (5l )M. Кл.

H 04 11/08

//Н 03 К 13/34 с присоединением заявки J% (23) Приоритет

3Ъеударетееааый кематет

СССР аа aaattttt аэоеретенвй я вткрытяЯ

Опубликовано 15,08.82. Бюллетень щ 30 (53) УДК 621. .394. 14 (088. 8) Дата опубликования описания 17.08.82

К . К. Ещин, А. К. Заволокин, В. И. Зарорскмй,,Л. А. Мошков

И. Ф. Мусатов, В. И. Рейнер и Е К. Юферова (72) Авторы изобретения (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

В ДИСКРЕТНОЙ ИНФОРМАЦИИ

Изобретение относится к технике n peA9÷è информации и может использовать-", ся в многоканальных системах передачи информации, а также в UBM, в которых информация передается в корректирующем коде.

По основному авт. св. Ж 860335 известно устройство дпя испражения ошибок в дискретной информации, закодированной корректируквцим кодом, содержа1О щее последовательно включенные сумматоры, локализатор ошибок, дешифратор, блоки ключей 3t дополнительные сумматс ры, другие входы каждого из которых подключены K соответствующей грутспе

15 входов устройства, другие входы кажд го блока ключей — к выходам соответствуимцего сумматора, все выходы локализатора ссцибок подключены к входам элемента ИЛИ (1) .

Однако известное устройство имеет низкую исправляющую способность.

Бель изобретения - повышение исправляющей способности.

Для достижения этой пепи в устройство для исправления ошибок в дискретной информации, закодированной корректирующим кодом, введены последовательно соединенные дополнительный элемент

ИЛИ, инвертор и элемент совпадения, а также бпоки сравнения и первые и вторые элементы И, каждых по числу сочетаний по два из числа прсеерочных разрядов в блоке корректнрукнпего кода, при этом первый и второй входы каждого блока сравнения объединены с сит нальными входами соответствунхцих .блоков япочей, первый и второй входы каждого первого элемента И объединены с соответствутсецими входами дешифратора, выход каждого блока сравнения через соответствукеций второй элемент И, второй вход которого соединен с выходом соответствукицего первого элемента И, соединен с соответствуквпим входом дополнитеп.ного элемента ИЛИ, а выход элемента ИЛИ соединен со вторым входом элемента совпадения.

3 9517

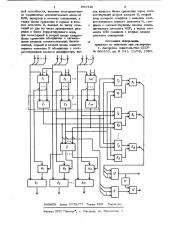

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство дпя исправления ошибки в дискретной информации, закодированной корректирующим кодом, содержит и1 сумматоров 3q - 3,ь„, локализатор 2 ошибок, состоящий из щ элементов ИЛИ

2„2„„, дешифратор 3, ьь блоков ключей 4, - 4,, Vt дополнительных сум- ьо маторов 54 - 5> ь элемент ИЛИ 6, 5 блоков сравнения 7.ь - 7, первых элементов И 8ь - 8, 5 вторых элементов И 9,1 - 9, дополнительный элемент ИЛИ 10, инвертор 11, элемент совпадения 12.

Устройство работает следующим образом.

При поступлении на входы устройства входного корректирующего кода в каждом сумматоре 1, 1, ... 1„„осуществляется проверка соответствующего контрольного соотношения путем вычитания по модулю P значений соответствующих информационных Р-ичных разрядов из соответствутсщего контрспьнаго разряда. Если ошибок нет, результат в каждом сумматоре равен нулю, сигналы на выходах всех элементов ИЛИ 2„, 2, ... 2 локализатора ошибок 2, дойолнитепьного элемента ИЛИ 10 и элемента совпадения 12 также равны нулю, ace блоки ключей 44, 42 ... 4 заперты и входной кОд через дрполнительные сумматоры

5<, 5 ... 5> без изменения поступает на выход устройства.

4 ь

При наличии ошибки в одном P-ичном разряде на выходе одного, нескольких ии всех суЧ 14. 14 - 1и1 р —. зультат оказывается отличным от нуля; при этом во всех таких сумматорах результат один и тот же, равный величине ошибки с соответствукпдим знаком (+», если ошибка возникла в контрольном ри ряде, - - если в информационном). 4

В этом случае на выходе соответствующих элементов ИЛИ 2„, 2 .„2и локализатора ошибок 2 и элемента ИЛИ 6 появпяется сигнал 1 . Дешифратор 3 сформировывает на соответствующем выходе сигнал, отпирающий бюки ключей того разряда, где возникло искажение, и s соответствующем дополнительном сумматоре значение ошибки, поступающее с выхода соответствующего сумматора Ы через открытъ|й блок ключей прибавляется (вычитается) к искаженной группе разрядов в

40 1

Таким образом, происходит исправле- . ние одиночнои ошибки. Блоки сравнения

74 ь 7,4 ... 7 сформировывают сигнал

"1 там, где результатъ на выходах двух соответствую них сумматоров не совпадают, а первые элементы И 8, .у ь .8 ... 8 - там, где оба результата отличны от нуля. Так как. при одиночной

Ошибке все нулевые результаты совпадают, то на выходах всех вторых элементов И 9,, 9,ь ... 9с; ь а также допсьпнительного элемента ИЛИ 10 сформировывается сигнал О, а на выходе элемента совпадения 12 — сигнал 1 . Это свидетельствует о наличии ошибки в одной и отсутствии ошибок в другой группах разрядов кода.

При наличии ошибки в двух P-ичных разрядах на выходах сумматоров 1<, 1, ... l „появпяются нулевые результаты, из которых хотя бы один отличает ся от других. В этом случае соответствующий блок сравнения и соответствующий первый элемент И одновременно сформировывают сигнал "1, который через соответствующий второй элемент И проходит на вход дополнительного элемента ИЛИ 10, сигнализируя о наличии двойной сшибки и одновременно через инвертор 11 запрещает появление сигна,ла об одиночной ошибке на выходе эле мента совпадения 12, Тем самым неверно исправленный код на выходах дополнительных сумматоров 5,, 5 ... 5 „не воспри:нимается как правильный.

Технико-экономические преимущества предложенного устройства по сравнению с известным заипочаются в том, что оно обеспечивает более высокую достоверность выходной информации, сигнализиРуя о наличии ошибок в ней в том случае, когда корректирующих способностей кода и устройства недостаточно дпя исправления этих сатибок.

При этом обнаруживается подавляющее большинство двоичных ошибок; не обнаруживается только ряд таких ошибок, когда в определенных парах P-ичных разрядов возникак г одинаковые ошибки.

Формула изобретения

Устройство дпя исправления ошибок в дискретной информации, закодированной- корректирующим кодом по авт. св.

34 860335ь отлича юшее ся тем, что, с целью повышения исправпяю

951740

БНИИПИ Заказ 5976/77 Тираж 688 Подписиюо

Филиал ППП Патент, r. Ужгород, ул. Проектная, Ч щей способности, введены последовательно соединенные дополнительный элемент

ИЛИ, инвертор н элемецт совпадения, а также блоки сравнения и первые и вторые элементы И, каждых по числу сочетаний по два из числа проверочных раэ. рядов в блоке корректирукнцего кода, при этомпервый и второй входы каждого блока сравнения объединены с сигналь ными входами соответствуюших блоков юпочей, первый и второй входы каждого первого элемента И объединены с соответствукииими входами дешифратора, вы-! ход каждого блока сравнения через соответствукнций второй элемент И, второй вход которого соединен с выходом соответствукюцего первого элемента И, сое5 динен с соответствукядим входом дополнительного элемента ИЛИ, а выход эл мента ИЛИ соединен с вторым входом элемента совпадения.

Источники информапы, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 860335, кл. Н 04 Ь 11/08, 1980.