Частотно-импульсный компаратор

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистических

Ресгтттбттик

ОП ИСАНИЕ

ИÇOSPETKН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Н 03D 13/00 с присоединением заявки №

Геаударстеенный комитет

СССР но делам наебретенкй н отерытнй (23) Приоритет

Опубликовано 23.08.82. Бюллетень № 31

Дата опубликования описания 23.08.82 (53) УДК621.317. .7 (088,8) М. А. Цуда, Р. A. Дуда, М. Г. Опаец и А. А. Столяров (72) Авторы изобретения (7I) Заявитель

Тернопольский финансово-экономический институт. (54) ЧАСТОТНО-ИМПУЛЬСНЫЙ КОМПАРАТОР

Изобретение относится к импульсной технике, автоматике и вычислительной технике и может использоваться при построении автоматизированных систем контроля и регулирования, а также в прибо5 ростроении.

Известно устройство дпя определения знака разности двух импульсных последовательностей, содержащее блок искпючения совпадающих импульсов, R5 -триг- 0 геры, элементы И и инверторы (11 .

Недостатками этого устройства являются его сложность, обусповпенная необходимостью применения бпока искпючения т> совпадающих импульсов, и малые функционапьные возможности, так как оно не определяет меньшей входной частоты и не находит модуля разности частот.

Наибопее близким по технической суш-2î ности к предлагаемому является .устройство дпя определения знака разности двух частот, содержащее два триггерных блока вычитания частот, первые входы которых подключены ко входам устройства, а вторые к выходу элемента совпадения 121

Недостатками известного устройства являются его малые функциональные воз-. .можности, так как оно не мажет использоваться дпя вьгдепения меньшей из входных частот и модуля разности частот.

Цепью изобретения явпяется расширение функциональных возможностей путем обеспечения возможности выде пения меньшей входной частоты и разности входных частот.

Поставленная цель достиг ается тем, что в частотно-импульсном компараторе, .содержащем выходной триггер знака, первый и второй блоки вычитания частот, первые входы которых подключены соответственно к первой и второй входным шинам устройства, а выходы - соответст» венно к 5, R-входам выходного триггера знака, выходы которого соединены соответственно с первой и второй выходными шинами устройства, введены выход3 95369 ной эпемент ИЛИ и бпок выдепения меньшей частоты, первый и второй входы которого подкпючены соответственно к первой и второй входным шинам устройства, а выход блока выдепения меньшей частоты соединен со вторыми входами первого и второго блоков вычитания частот и с третьей выходной шиной устройства, первый и второй входы выходного эпемента

ИЛИ соединены с соответственно с вы- to ходами первого и второго бпоков вычитания частот, а выход выходного элемента

ИЛИ - с четвертой выходной шиной уст1 ройства, причем бпок вычитания частот содержит эпемент ИЛИ-НЕ, инвертор и 35 блок привязки частот, первый вход которого соединен с вторым входом блока вычитания частот, а второй выход — со входом инвертора и первым входом бпока вы- ° читания частот, выход блока привязки час«д тот подкпючен к первому входу элемента

ИЛИ-НЕ, второй вход которого соединен с выходом инвертора, а выход эпемента

ИЛИ-HE соединен с выходом блока вычитания частот. 25

Блок привязки частот содержит эпемент И и триггер, 5 -вход которого подключен к первому входу блока привяз-! ки частот. R-вход — к выходу бпока привязки частот и выходу эпемента И, пер- 5п вый Bxoll которого соединен с вьЖодом триггера, а второй вход - с вторым входом блока привязки частот.

В качестве бпока выделения меньшей частоты испопьзуется бпок привязки частот.

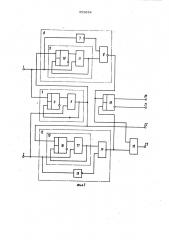

На фиг. 1 изображена структурная схема предпагаемого устройства; на фиг. . временные диаграммы, характеризующие работу устройства.

Компаратор содержит первую и вторую входную шины 1 и 2, бпок 3 выдепения меньшей частоты, состоящий из триггера

4 и эпемента 5 И, первый блок 6 вычи: тания частот, состоящий из инвертора 7, элемента 8 ИЛИ-НЕ, бпока 9 привязки частот состоящего из триггера 10, эпемента 11 И, второй бпок 12 вычитания частот, состоящий из инвертора 13, 50 элемента 14 ИЛИ-НЕ, бпок 15 привязки частот, состоящий из триггера 16„ эпемента 17 И, выходной триггер 18 знака, выходной элемент 19 ИЛИ, первую, вторую, третью и четвертую выходные шины 20, 21, 22 и 23 устройства.

Частотно-импупьсный компаратор работает следующим образом.

4 4

На первую и вторую входные шины 1 и 2 поступают сравниваемые частоты, представленные в виде последовательностей коротких импульсов (фиг. 2 а, 6).

Бпок 3 выделения меньшей частоты осушествпяет выдепение меньшей из .входных частот, подаваемых на первую и вторую входные шины 1, 2.

Ю

Бпок работает следующим образом (фиг. 2).

Импупьсами частоты, поступающей на первую входную шину 1 компаратора (фиг. 2 а), триггер 4 устанавпивается, например, в единичное состояние (фиг.2 a), разрешающее прохождение последующего за этим моментом импупьса второй входной шины 2 устройства (фиг. 2 6) через эпемент 5 И на выход блока 3 выдепения меньшей частоты на R-вход триггера 4 (фиг. 2 г) с появпением которого триггер 4 устанавпивается в нупевое состояние (фиг. 2 в), подготавпиваясь к приему последующего импупьса с первой входной шины 1 устройства. Еспи 5 (,1 (левая часть временных диаграмм, показанных на фиг. 2), то на выходе бпока 3 выдепения меньшей частоты выдепяется частота „, причем импупьсы этой частоты будут привязаны во времени к импульсам частоты Г1. В этом спучае указанное устройство работает в качестве бпока привязки частот. Еспи „ ) Хо (правая часть временных диаграмм, приведенных на фиг. 2), то, так как сброс триггера 4 осушествпяется в соответствии с импупьсами частоты, поступающей на вторую входную шину 2 устройства (фиг.2 6), на выходе бпока 3 выделения меньшей частоты выдепяется частота 1

Таким образом, при f >Е, на третью выходную шину 22 устройства поступают импупьсы частоты <,8 при g„сf,2 частоты f„,т. е. в обоих спучаях устройство выделяет меньшую из входных частоты . ипи !

Возможность предварительного определения меньшей частоты позвопяет осуществить упрощение первого и второго блоков 9 и 12 вычитания частот, работу которых рассмотрим на первом бпоке 6 компаратора при E„ >Fq.В связи с тем, что известная уже меньшая частота б подается на вход вычитаемого первого блока 6 вычитания частот, который является информационным входом бпока 9 ,привязки частот, а бопьшая частота f„ подается на вход уменьшаемого первого блока 6 вычитания частот, который яв4 6 первые входы которых подкпючены соот- ветственно к первой и второй входным шинам устройства, а выходы - соответственно к S R-входам выходного триггера знака, выходы которого соединены соответственно с первой и второй выходными шинами устройства, о т и и ч а юш и и с я тем, что, с целью расширения функциональных вбзможностей путем обеспечения возможности выдепения меньшей входной частоты и разности входных частот, в него введены выходной эпемент

ИЛИ, и блок выдепения меньшей частоты, первый и второй входы которого подкпючены соответственно к первой и второй входным шинам устройства, а выход.бпока выделения меньшей частоты соединен с вторыми входами первого и второго блоков вычитания частот и с третьей выходной шиной устройства, первый и второй входы выходного элемента ИЛИ соединены соответственно с выходами пер. вого и второго блоков вычитания частот, . а выход выходного эпемента ИЛИ-с чет-. вертой выходной шиной устройстве;

2. Компаратор по п. 1, о т и и ч аю ш и и с я тем, что бпок вычитания частот- содержит элемент ИЛИ-НЕ, инвертор и бпок привязки частот, первый вход которого соединен со вторым входом бпока вычитания частот, а второй выходс входом инвертора и первым входом бпока вычитания частот, выход блока привязки частот подкпючен к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с выходом инвертора, а выход эпемента ИЛИ-НŠ— с выходом бпока вы5 95369 ляется и синхронизируюшим входом бпока

9 привязки частот, на выходе бпока 9 выдепяется частота f,импупьсы которой привязаны во времени к импупьсам частоты Это позвопяет осушествить вы1 читание частот путем искпючения совпадаюших импульсов двух синхронизированных импупьсных поспедоватепьностей, что обеспечивается инвертированием импупьсов большей частоты (в данном спучае 1р частоты f ) инвертором 7, с поспедую1 шей подачей этих импупьсов на второй вход эпемента 8 ИЛИ-НЕ, на первый вход которого поступают импупьсы меньшей частоты. 15

В связи с тем, что на вторые входы первого и второго блоков 6 и 12 вычитана;. частот подается меньшая иэ входных н,1 частот, а на первые входы - частоты 1„и 1,1, »а выходах первого и

20 второго бпоков б и 12 возможны спедуюшие ситуации. При f„CЕ на выходе первого бпока 6 импупьсы отсутствуют а на выходе второго бпока 1 2 выделяется неравномерная последовате пьность прямых

25 импупьсов со средней частотой, равной модушо разности входных частот:

=(Е -Я11=,1-ЕПри f )f на выходе первого блока 6 выделяется неравномерная последовательность прямых импульсов со сред-ЗО ней частотой равной модупю разности частот. Х = Е,-F<)< 1„-61,а на выходе второго блока 12 импупьсы отсутствуют.

Это позвопяет при шобом отйошении входных частот получить модуль разнос- 35 ти входных частот „и ц путем подачи выходных сигнапов первого и второго бпоков 6 и 12 вычитания частот на входы эпемента 19 ИЛИ, а знак разности— путем подачи этих же сигналов íà R,S — 40 входы выходного триггера 18 знака.

Таким образом, предлагаемое устройство, так же как и известное устройство, осушествпяет определение знака разности входных частот и, кроме того, до- 45 попнитепьно выдепяет меньшую из входных частот и модуль разности входных частот. Спедоватепьно, благодаря введению блока 3 выдепения меньшей частоты, в качестве которого используется бпок привязки частот, функционапьные воэможности предлагаемого устройства расширились, причем удапось упростить схему первого и второго бпоков 6 и 12 вычитания частот. 55

Формупа изобретения

1 ° Частотно-импульсный компаратор, содержаший выходной триггер знака, первый и второй блоки вычитания частот, читания частот.

3. Компаратор по и. 2, о т п и ч аю ш и и с я тем, что бпок привязки частот содержит элемент И и триггер, 5 -вход которого подкпючен к первому входу блока привязки частот R-входк выходу блока привязки частот и выходу элемента И, первый вход которого соединен с выходом триггера, а второй входс вторым входом блока привязки частот.

4. Компаратор по и. 1, о т л и ч аю ш и и с я тем, что в качестве блока выделения меньшей частоты используется блок привязки частот.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетепьство СССР по заявке % 27 53 66 4/1 8-2 1, кл. G 01 R 23/00, 21.02.80.

2. Авторское свидетепьство СССР

% 481979, кп» Н 03 Э 13/00, 1975 (прототип).

953694

Ь и ,У! Cgg

Составитель И, Каппин.

Редактор Г. Волкова Техред М. Надь Корректор М. немчик

Закаэ 6291/79 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектнай, 4