Устройство задания выдержек времени

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнапнстнческнх республик

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 953714 (61 ) Допол н и тельное к а вт. с вид-ву— (22) Заявлено 04.01.81 (21) 3230104/18-21 с присоединением заявки № (23) Приоритет

Опубликовано 23.08.82. Бюллетень № 31

Ю

Дата опубликования описания 23.08.82 (si)м. К.ч .

Н 03 К 5/13

ВеУаерстеапаб кемитет

СССР ио делен изебретеиий и атирмтий (53) УДК.621.318, .5(088.8) (72) Авторы изобретения

И. Б, Казаков и М.А. Бек

Ф

ll

Всесоюзный проектно-конструкторский институт технологии электротехнического производства (ВПТИЭЛЕКТРО) (71) Заявитель

l (54) УСТРОЙСТВО ЗАДАНИЯ ВЫДЕРЖЕК

ВРЕМЕНИ

Изобретение относится к автоматике и импульсной технике и может быть использовано, в частности, в системах управления промышленными роботами.

Известно устройство задания выдер5 жек времени, которое состоит из отдельных реле времени, подключенных к обшему источнику эталонного напряжения. Количество реле времени определяется числом необходимых выходов устройства.

Каждое реле времени содержит времязадаюшую R с -цепь, параметры которой определяют выдержку времени. Кроме тэго устройство содержит блок сравнения по числу реле времени.

Данное устройство обеспечивает получение нескольких различных выдержек времени, используя в каждом реле времени различные времязадаюшие цени 11.

Йедостатками устройства являются 2о сложность схемы, обусловленная тем, что количество отдельных реле времени определяется количеством необходимых вы-. держек времени, а также необходимость

2 для получения больших выдержек времени использования времязадаюших R t -ue пей с большой постоянной времени, что уменьшает точность и стабильность работы устройства.

Наиболее близким к изобретению по технической сушности является устрой ство задания выдержек времени, которое содержттт времяэадающие RC -цепи.

;и кольцевых регистров с числом разрядов rn, причем времязадаюшие RC -цепи включены между разрядами только одного из регистров, соединенных таким образом, что выход первого разряда (n -1) регистра соединен с входом последнего разряда и регистра, выход второго разряда (и-1 ) регистра соединен с входом предпоследнего разряда и регистра и т. a. ao соединения последнего разряда (n -1 J регистра с первым разрядом т1,регистра.

Устройство содержит также и RS -триггеров. Каждый из прямых выходов R5триггеров соединен с входом первого

953714 разряда соответствующего регистра, а кажный из входов установки в 0" RS триггеров соединен с выходом второго разряда соответствующего регистра, при этом входы установки в 1" RS -триггеров объединены.

Известное устройство обеспечивает получение различных выдефкек времени, определяемых номером кольцевого регист ра и номером разряда кольцевого регист 1О ра при использовании в устройстве времязадающих RC -цепей по числу разрядов только одного регистра, а не в зависимости от необходимого количества выдержек времени, что значительно упрощает 15 схему устройства (21.

Однако разрешающие сигналы поступают с выходов RG -триггеров на первые разряды всех п регистров одновременно и присутствуют на входах первых разря- щ дов регистров длительно, |то может привести к появлению ложных сигналов на выходах устройства при появлении импульс ной помехи на сигнальном входе разряда регистра. 25

Целью изобретения является повышение помехоустойчивости.

Для достижения поставленной цели в устройстВо задания выдержек времени, содержащее времязадаюшие РС -цепи, . включенные между разрядами одного из и кольцевых регистров„соединенных таким образом, что выход первого разряда и -1 регистра соединен с входом последнего Разряда и -Р гис р . вь ход второго разряда и -1 регистра соединен с входом предпоследнего разряда

11 -го регистра, выход последнего разряда (n -1)-го регистра с, первым разрядом п -го регистра, n RS -триггеров, прямой выход кажного из RS -триггеров соединен с входом первого разряда соответствуквцего регистра, вход установки в 0" первого RS-триггера соединен с выходом второго разряда первого регистра, а его вход установки в 1» подключен к клемме запуска устройства, введено и -1 блоков установки второго и последующих RS триггеров в 0", причем вход каждого блока установки соединен

50 с прямым выходом соответствующего фS -триггера, выход блока установки соединен с входом установки в 0 того же триггера, а вход установки в 1" RSтриггера, начиная со второго, соединен

55 с выходом последнего разряда предыду щего регистра.

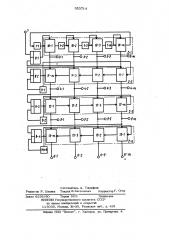

На чертеже показана блок-схема предлагаемого устройства.

Устройство задания выдержек времени содержит времязадающие ЙС -цепи

1-1-1-т,n †.кольцевых регистров 2-1-2-n выходные шины первого регистра

3-1-3-tn, выходные шины второго регист ра 4-1-4-m, выходные шины третьего регистра 5-1-5-rn, выходные шины и -го регистра 6-1-6-rn, клемму 7 запуска, п 95 -триггеров 8-1-8-n, (n -1) блоков установки 9-1-9-(и -1)Й5 -триггеров в "0". Каждый кольцевой регистр 2-1-2»»п состоит иэ разрядов. Так первый регистр 2-1 состоит из разрядов 10-1-.10-Al. Второй кольцевой регистр состоит из разрядов 11-1-11-т. Третий коль-цевой регистр состоит иэ разрядов

12-1-12-1п, последний и кольцевой регистр состоит из разрядов 13-1-13-m.

Времязадающие RC -цепи 1-1-1- тп включены между разрядами 10-1-10- п регистра 2-1, и число таких цепей равно т1т (на чертеже 4 цепи). Вход установки в. "1" RS -триггера 8-1 соединен с клеммой 7, вход установки в "1" RS— триггера, начиная со второго триггера, соединен с выходом гп -го разряда (1 1 -1 )-го регистра.

Прямой выход Q p -го RS -триггера соединен с входом первого разряда п -го регистра.

Прямые выходы В5 -триггеров, начиная с RS -триггера 8-2, дополнительно соединены с входами блоков установки 9-1-9-(11 -1), выходы которых соединены с входами установки в "0" того же RS -триггера.

Устройство задания выдержек времени работает следующим образом.

В исходном состоянии все разряды регистров 2-1-2-rl u RS - триггеры 8-1-8-11 выключены, и на выходных шинах (3-l-3-nl)-(6-1-6- гу1) сигналы отсутствуют.

Регистры 2-1-2-и построены таким образом, что запись "1" в п1-й разрщ возможна только при наличии входного сигнала и разрешающего сигнала на шине разрешения,тт. е. если включен предыду щий (rn -1)-й разряд.

Устройство запускается разовым импульсом, подаваемым на клемму 7. При этом RS -триггер 8-1 перебрасывается в противоположное состояние, выдавая сигнал разрешения первому разряду пер» вого регистра. Разряд регистра включается, так как его шины разрешения и входная объединены.

Через время, определяемое параметрами R -цепи 1-1, включается разряд

714 6 срабатывания последнего разряда предшествукхпего регистра, а появление синхронных помех на обоих входах разрядов регистров маловероятно.

Формула изобретения же триггера, а вход установки в 1 RS

Количество членов =n -2 гае n — номер кольцевого регистра; .триггера, начиная со второго, соепинен с выходом последнего разряда предыдуmего регистра.

t  — время задержки RC -uemr. 40

По сравнению с известным предлагае- Источники информации. мое устройство задания выдержек времени принятые во внимание при экспертизе обладает большей помехоустойчивостью, 1. Патент Японии 34 52-19070, так как сигнал на шинах разрешения . кл. 98/5 2 0 опублик 1977. первых разрядов каждого регистра, посту4 2. Авторское свидетельство СССР пающий с выходов RS -триггеров, крат- по заявке N - 2750916, кл. Н 03 К 5/13, ковременный и появляется только после 12 04.79.

5 953

10-2 регистра 2-1. Выходной сигнал разряда 10 2 перебрасывает AS -триггер 8-1 в

"0 . состояние, исключая его из дальнейшей работы.

Таким образом, занесенный в первый регистр 10-1 сигнал "1" циркулирует в нем с периодом Т, опреаеляемым параметрами Rr -цепи 10-1.

Включаясь, разряд 10-р1 регистра 2-1 перебрасывает RS -триггер 8-2 в про- 10 тивоположное исходному состояние.

При этом триггер 8-2 выдает сигнал разрешения разряду 1 1-1 регистра 2-2, и разряд 11-1 включается.

Одновременно сигнал с триггера посту- пает на вход блока 9-1 установки AG — триггера 8-2, Выходной сигнал блока 9-1 поступает на вход установки в "0" RSтриггера 8-2. При этом триггер перебрасывается и исключается из дальнейшей err работы.

После следующего цикла работы регистра 2-1 с выхода разряда 10-3 регистра 2-1 íà вход разряда 11-2 регистра 2-2 поступит входной сигнал, и 25 разряд 1 1-2 включается.

Таким образом, после каждого цикла работы (n -1)-го регистра в п -м регистре сигнал "1 продвигается на один разряд, и на выходных шинах имеем последовательность импульсов, следующих с периодом Т, определяемым выраже нием,Т = - 3и ".rq+ (3" + 3и +,.....,), 35

Устройство задания выдержек времени, содержащее времязааающие RC -цепи, включенные между разрядами одного иэ кольцевых регистров, соединенных таким образом, что выход первого разряда р -1 регистра соединен с входом с входом последнего разряда регистра, выход второго разряаа р -1 регистра соединен .с входом предпоследнего раэрипа и -го регистра, выход последнего разряда (n -1)-го регистра с первым разрядом р -ro регистра, р ЯS -триггеров, прямой выход каждого из ЯЬ -триггеров соединен с входом первого разряда соответствующего регистра, вход установки в . 0 первого ЯЯ «триггера соединен с выходом второго разряда первого регистра, а его вход установки в 1 " подключен к клемме:запуска устройства, о т л и— ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введено п -1 блоков установки второго и последующих Р$ -триггеров в 0", причем вход каждого блока установки соединен с прямым выходом соответствующе-. го RS -триггера, выход блока установки соединен с входом установки в 0 того

983714

Составитель А. Тимофеев

Редактор Р. Цицика Техред Ж.Кастелевич Корректор Г. Огар

Заказ 6292/80 Тираж 959 Подлисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4