Транзисторное реле

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Н 03 К 17/60

Ркудвретванньй кемнтет

СССР аю делам изобретений и открытнй (53) УДК 621.374.. 3(088.8 ) Опубликовано 23,08.82. Бктллетень № 31

Дата опубликования описания 23.08.82

В. П. Лнмов, Н.А. Брюкно„В. Я. Гребенщик (72) Авторы изобретения (7l) Заявитель (S4) ТРАНЗИСТОРНОЕ РЕЛЕ

1.

Изобретение предназначено для использования преимущественно в виде полупроводниковой интегральной микросхемы в устройствах автоматики и управления.

Известно высокочувствительное по току транзисторное реле на транзисторах раэ5 ного типа . проводимости, прнднаэначенное для работы в условиях импулвсных динамических помех, включающее в себя два-три транзистора, первый иэ которых имеет, по отношению к остальным, проти», воположный тип проводимости, и его эмиттер через один или несколько диодов смещения соединен с шиной питания, цепь положительной резистивной обратной сВВ зи, т1ервьтй и второй резисторы которой соединены с базой первого транзистора, второй вывод первого резистора соединен с шиной питания, а второй вывод второго резистора подключен к коллекто- zo ру второго транзистора, соединенному через третий резистор с шиной питания, Цепь положительной обратной связи обео-. пеиюает помехоустойчивость в условиях

2 импульсных динамических помех. Помехсьустойчивость транзисторного реле определяется величиной коэффициента возврата, равного отношению тока отпускания к току срабатывания реле (1) .

Недостатком устройства является то, что его реализация методами полупроводниковой интегральной технологии, особенно если транзисторное реле должно иметь высокую чувствительность по току (не сколько сот микроампер и менее), затруднена, так как второй резистор этих уст ройств будет иметь номинал несколько сотен килоом. Для получения этого резистора необходимо проводить отдельные специализированные технологические операции получения высокоомного слоя, что повышает трудовые затраты и сннжеет выход годных.

Наиболее близким по технической сути к предлагаемому устройству является транзисторное реле (усилитель релейного типа, управляемый током), цепь обратной связи которого содержит делитель напря7 4

Так как каждый резистор делителя апряжения зашунтирован диодом, то при зменении температуры и напряжения иоочника питания падение напряжения на этом делителе будет изменяться оаинакоо с потенциалом базы первого транэиоора, что стабилизирует ток обратной свяи, протекающий через второй резистор и стабилизирует коэффициент возврата.

Вывод из одного резистора, входящего состав реэистивного делителя и подюченного к второму выводу второго резистора обеспечивает необходимую величину коэффициента возврата.

Такая схемотехника позволяет получить наименьшее число изолированных областей, необходимых для реализации резисторов делителя напряжения методами полупроводниковой интегральной технологии, так как резистор и диод можно выполнять в одной изолированной области совмещенными.

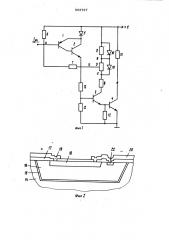

На фиг. 1 изображена электрическая схема предлагаемого устройства; на фиг. 2 — разрез диоаа и резистора делителя напряжения; на фиг. 3 - вид сверху.

Устройство выполнено в виде полупроводниковой интегральной микросхемы с диэлектрической изоляцией элементов .

Транзисторное реле (фиг. 1 ) состоит из четырех транзисторов 1 - 4. Первый транзистор 1 р-и-р типа, а второй 2, третий 3 и четвертый 4 - tl-p- tl типа, Эмиттер первого транзистора подключен через диод смешения 5 к шине источника питания (+Е). База транзистора 1 (точка А) соединена с цепью положительной резистивной обратной связи, состоящей з резисторов 6 - 8 и делителя напряжения иэ двух последовательно соедине +ных одинаковых резисторов 9, каждый нэ которых зашунтирован диодом 10. Один иэ резисторов имеет вывод ll, который соединен с резистором 7.

Резисторы 12 задают рабочие режимы транзисторов 3 и 4, В цепь коллектора транзистора 4 включена нагрузка 1 3.

Резисторы 9 и диоды, составляющие делитель напряжения, выполнены следующим образом (фиг. 2 и 3). На поликристаллической подложке 14 с диэлектрической изоляцией 1 5, монокристаллическими областями 16 (например, из кремния П -типа), покрытыми аиэлектричес ким споем 17, сформирован диффузией бора резистор 18, к которому поавеаены шины алкминиевой металлнзации 1 9 — - 21 .

Шина с наиболее низким потенциалом с помощью невыпрямляющего контакта 22

3 95372 жения, образованный, третьим и четвертым резисторами. -1етвертый резистор н включен между коллектором третьего и транзистора и общей точкой второго и т третьего резисторов. Величина второго резистора уменьшается ориентировочно в в столько раз, в сколько четвертый резис- т тор больше третьего (2). з

Недостатком устройства при его реализации методами технологии интеграль р ных схем является сильная зависимость в коэффициентавозврата,, определяющего по- кл мехоустойчивость устройства, от температуры окружающей среды и напряжения источника питания. Зависимость коэффи- 1 диента возврата от температуры в основном обусловлена температурным изменением прямого падения напряжения на диодах смещения и эмиттерном переходе первого транзистора, а от напряжения питания - зависимостью величины падения напряжения на третьем резисторе в цепи об ратной связи.

Цепь изобретения — повышение помехоустойчивости. 2$

Поставленная цепь достигается тем, что в транзисторном реле, содержащем два каскада усиления, выполненных соответ ственно на первом и втором транзисторах разного типа проводимости и третьем и четвертом транзисторах одинакового типа проводимости, база первого транзистора подключена к общему выводу первого и второго резисторов, другие выводы zoторых подключены соответственно к по— ложительной шине источника напряжения и к резистивному делителю напряжения, включенному в коллекторную цепь третьего транзистора, эмиттер первого тран- и зисгора — к катоду первого иэ Н последоЯО вательно соединенных диодов, а анод

tL -го диода соединен с положительной шиной источника напряжения, эмиттер второго транзистора через третий резистор подключен к базе третьего транзистора и через четвертый резистор - к общей шине, ЯЗ которая соединена с эмиттером и через пятый резистор с базой четвертого транзистора, нагрузка включена между положи, тельной шиной источника напряжения и коллектором транзистора, каждый иэ и +1 © последовательно соединенных резисторов делителя напряжения зашунтирован диодом, при этом анод первого из них подключен к положительной шине источника напряжения, катод И +1-го шунтируюшего диода через шестой резистор — к коллектору е третьего транзистора, а входная шина соеаине*.и с базбй первого транзистора.

27 б рии 522 КН позволит отменить температурные испытания, повысить выход годных в 2 раза. Экономический эффект от внедрения на программе 20 тыс..шт. микросхем составит более 10 тыс. руб.

Транзисторное реле, содержащее два каскада усиления, выполненных соответственно на первом и втором транзисторах разного типа проводимости и третьем и четвертом транзисторах одинакового типа проводимости, база первого транзистора подключена к обшему выводу первого и второго резисторов, другие выводы которых подключены соответственно к положительной шине источника напряжения и к резистивному делителю напряжения, вклк ченному в коллекторную цепь третьего (транзистора, эмиттер первого транзистора — к катоду первого из N последователь но соединенных диодов, а анод N -го диода соединен с положительной шиной источника напряжения, эмиттер второго тран зистора через третий резистор подключен к базе третьего транзистора и через чет вертый резистор - к обшей шине, которая соединена с эмиттером и через пятый резистор - с базой четвертого транзисто ра, нагрузка включена между положитель ной шиной источника напряжения и коллектором четвертого транзистора, о т л Ич а ю щ е е с я тем, что с целью повышения помехоустойчивости, каждый из N +1 посладовательно соединенных резисторов делИтеля напряжения зашунти рован диодом, при этом диод первого из них подключен к положительной шине ио точника напряжения, катод М +1-го шун тирующего диода через шестой реэисторк коллектору третьего транзистора, а входная шина соединена с базой первого транзистора.

Hei очники информации, принятые so внимание при экспертязе

1. Вороскалевский В.И. Полупроводниковые реле на транзисторах разного типа проводимости. Сб. статей ЭТвА, вып. 2, N.. Энергия, 1971, с.-3542.

2. Технические условия б Ко 347122ТУ на микросхемы серии

522 KHl, Внедрение в производство предлагае мого устройства вместо микросхемы се5 9537 падсоединена к монокристаллической области 16. Вывод 11 выполнен путем фор мирования контактной области 23 в резисторе. 1 8.

Устройство работает следукецим образом.

В исходном состоянии транзисторы

1 - 4 заперты. При подаче входного то- Ф о р м у л а и з о б р е т е н и я ка 1 достаточной величины и равного току срабатывания потенциалом в точке 16

A (фиг. 1) открывается транзистор 1.

При этом в цепи его коллектора на резисторах возникает падение напряжения, достаточное для открывания транзистора

3. При открывании транзистора 3 в цепи 1 его коллектора начинает протекать ток, потенциал точки Б (фиг. 1) уменьшается, и через резистор 7 начинает течь ток положительной обратной связи. Открывается транзистор 4 и коммутирует напряже- и

we на нагрузку 1 3. При уменьшении входного тока до величины тока опускания, pasHoro разности тока срабатывания и тока обратной связи, потенциал точки

А уменьшается до величины, при которой закрываются транзисторы 1 и 2, После этого закрываются транзисторы 3 и 4.

Нагрузка 13 от положительной шины ис точ ника напряжения отключается.

При изменении температуры потен циал точки С (фиг. 1) при открытых транзисторах 1» »3 изменяется одинакоso с потенциалом точки А, поэтому разность потенциалов А и Б будет равна О.

Это стабилизирует ток обратной связи и

3$ коэффициент возврата будет зависеть только от температурного изменения величины резисторов.

При изменении напряжения питания потенциал точки С при открытых транзисторах 1 - 3 будет изменяться незначительно вследствие того, что диоды 10 включены s прямом направлении параллельно резисторам 9. Ток обратной связи будет стабилизирован и коэффициент воэвра та от напряжения зависеть не будет.

Резисторы 9 и диоды 10 выполнены совмещенными (фиг. 2 и 3), что позволяет проводить их формирование с наименьшим количеством изолированных обSO ластей.

953727

Составитель А. Егорычев

Редактор P. Бипика Техред К. Мы адьо Корректор Г. Решетник

Заказ 6293 в Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Филиал ППП Патент, г. Ужгород. ул. Проектная, 4