Делитель частоты с любым целочисленным коэффициентом деления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ

Союз Советсник

Социалистичесиик

Республик и 953236 (6I ) Дополнительное к авт. свид-ву ¹ 843246 (22) Заявлено 14.01.81 (21) 3238639/18-21 с присоединением заявки М (23) Приоритет

Опубликовано 23.08.82. Бюллетень J4 31

Дата опубликования описания 23.08.82 (5I)M. Кл.

Н 03 К 23/ОО

Веударстыииы5 комитет

СССР ае делам извбретеиий и открытий (53) УЙ К621.374. .44(088. 8) (72) Авторы изобретения

А. П. Ермолаева и П. Н. Смирнов (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ЛЮБЫМ

БЕЛОЧИСЛЕННЫМ КОЭФФИБИЕНТОМ

ДЕЛЕНИЯ

Изобретение относится к импульсной технике, в частности к делителям частоты, может быть использовано в автоматике, вычислительной технике и радиотехнике.

По основному авт. св. ¹ 843246, известен делитель частоты с любым целочисленным коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной. шиной, а выходы разрядов, кроме первого и второго подключены ко входам дешифратора, регистр сдвига и элементы И, первые входы которых и первый С-вход регистра

cABKT B обьединены H подключены K Bxojl ной шине, второй С-вход регистра сдвига подключен к выходу первого элемента

И, вторым входом соединенного с выходом первого разряда счетчика импульсов, а вход регистра сдвига соединен с вы- 2о ходом дешифратора, D -входы обьединены и подключены к выходу второго разряда счетчика импульсок, а выход первого разряда регистра сдвигa подключен K

2 второму входу второго элемента И, выход которого соединен с установочным входом счетчика импульсов Г1

Недостаток известного устройстваограниченные функциональные возможнос ти, так как оно ие может быть использовано в составе более сложных устройств> робота которых должна быть син хронизирована отдельным запускаюшим сигналом в случае, когда запускаюший сигнал имеет значительную длительность, а моментом синхронизации должен быть момент появления его переднего фронта.

Белью изобретения является расширение функциональных воэможностей делителя частоты с любым целочисленным коэффициентом деления, путем обеспечения синхронизации работы с передним фронтом запускакацего сигнала, а тапке формирования укороченного сигнала по переднему фронту запускающего сигнала, Поставленная цель достигается тем, что. в делитель частоты с любым цело численным коэффициентом деления вве953736 дены Р-триггер и дополнительный элемент И, первый вход которого соединен с выходом последнего разряда регистра сдвига и С-входомП-триггера, второй вход — с D - и Р -входами Э-триггера, и дополнительной входной шиной, гретий вход — с выходом О--триггера, а выход " с дополнительными -входом регистра сдвига и стробирующим входом дешифра гора.

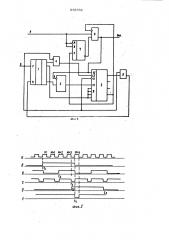

На фиг. представлена структурная схема устройства; на фиг, 2 — 4 — временные диаграммы, поясняющие его ра боту.

Устройство содержит счетчик 1 импульсов, дешифратор 2, регистр 3 сдвига, элемен гы 4-6 И;9-триггер 7, входные шины 8 и 9. .В

Устройство работает следукзцим образом.

Регистр 3 может работать в двух режимах. В том случае, если на выходе

1, соединенном с выходом дешифратора

2, имеется высокий потенциал, регистр

3 работает в режиме параллельной записи информации, При этом по синхронизирующим импульсам, подаваемым нв второй С-вход регистра 3 в его разряды производится запись информящии, подаваемой на егоР-входы.

Если vaV-входе имеется низкий потенциал, то регистр 3 работает в режиме сдВига. При этом по синхрониэирующим импульсам, подаваемым на первый

С-вход регистра сдвига производится сдвиг ранее записанной информации, при-. чем в первый разряд производится запись информации, подаваемой на V2-вход, соединенный с выходом дополнительного элемен га И.

Рассмотрим работу устройсгва в режиме делителя частоты. При этом нв шину 8 поступает непрерывная последовательность импульсов (фиг..2о), а на шине 9 имеется низкий потенциал, приводящий по R-входу D pmrepa 7 в. нулевое состояние, т.е. на его инверсном выходе имеется :высокий потенциал. Зле мент 6 закрыт низким потенциалом на его втором входе, что соответствует отсутствию сигнала на выходе устройства и разрушению работы дешифратора 2.

На выходе элемента 4 имеется непрерывная последовательность импульсов, следухщих с частотой, равной половине входной и образукзцвяся как резуль гвт логического перемножения высокого потенциала на выходе первого разряда сче гчика 1 с тактовым импульсом.

1О

Потенциалы на выходах всех разрядов регистра 3 имеют низкий уровень, твк как при отсутствии высокого потенциала с выхода дешифратора 2 регистр 3 работает в режиме сдвига, заполняется сигналами низкого уровня, подаваемыми на его V -вход с выхода закрытого элемента 6. Элемент 5 закрьгг низким потенциалом с выхода первого разряда регистра 3, ч го соответствует отсутствию сигнала обнуления aaR-входе счетчика. 1.

Для определенности допустим, что требуемый коэффициент деления делителя частоты может быть представлен в следующем виде К М + 2 + 2 + 1, тогда выходной сигнал с дешифратора 2 примет высокий уровень (дешифратор сработает) по

М-му импульсу входной последоватепь20 ности (4, фиг. 2 ). Начиная с этого момента, регистр 3 переилючается в режим параллельной записи, однако состояние выходов разрядов регистра 3 не изменякггся, поскольку счетчик 1 предполагает25 ся суммирующим и перенос в какой-либо старший разряд, вызывающий появление сигнала на выходе дешифратора, соответствует обнулению ьащдших разрядов счет» чика, т.е. низкому потенциалу на выходах зо как первого, так и второго разряда. По (М+2)-му импульсу входной последовательнос ги устанавливается высокий потенциал на Р-входах регистра 3 (t2, фиг. 2о).

По (М-3)-му импульсу устанавливается высокий потенциал на первом разряде счетчика 1, что обеспечивает прохождение через элемент 4 паузы после (М+3)-го входного импульса. (45, фиг. 2g)

4О момент времени соответствует измене» нию состояния на выходах всех разрядов регистра 3. На фиг. 2 (эпюра 8) приведена временная диаграмма изменения потенциала на выходе 4-го разряда ре45 гистра 3.

Так квк элемент 5 подготовлен к от- крытию высоким потенциалом на выходе

1-го разряда регистра 3, то (М+3+1)-й импульс входной последовательности проходит на его выход (,4, фиг. 2е), пос гупая на К-вход счетчика 1, вызывая его обнуление, Обнуление счетчика 1 приводит к пропаданию сигнала на выходе дешифратора 2, что вызывает пере° ключение регистра 3 в режим сдвига

55 импульсов и постепенное установление низких потенциалов на всех его выходах.

Твк, установление низкого потенциала на 4-м выходе регистра 3 произойдет

9537

20 по 4-му заднему фролу входных имрульсов (4g фиг. 2g)

Рассмотрим работу делителя частоты в режиме формирователи импульсов, Если предположить чго момент появления 5 высокого потенциала на шине 9 случаен, то необходимо рассмотреть два случая.

Первый соответствует появлению сигнала на шине 9 тогда, когда потенциал на выходе последнего разряда регистра 3 . имеет низкий уровень (вне интервала

4 5),фиг- 2j)

Второй случай соответствует появлению сигнала на шине 9, когда на выходе последнего разряда регистра 3 высокий потенциал (внугри интервала t>- t,> фиг. 2 ).

Рассмотрим первый случай. В момент появления входного сигнала на шине 9 (», фиг. 30) начинается формирование выходного сигнала (4», фиг. Зг), так как элемент 6 о гкрыт высоким потенциалом с инверсного выхода 0- григгера

7 и низким потенциалом с выхода 4-ro разряда регистра 3 сдвига, На выходе дешифратора 2 с этого момента независимо от текущего состояния счетчика 1 поддерживается низкий потенциал, гак ка дешифратор 2 закрывается выходным сигналом по стробирующему входу, т.е. регистр 3 работает в режиме сдВига им-- ЗО пульсов.

Выход элемента 6 соединен cV» -вхо дом регистра 3 сдвига, поэтому все разряды регистра постепенно заполняются сигналами с высоким потенциалом (6, 35

t,g, и соответственно, фиг. 3,9

8, Ж, 3 ). Начиная с момента t, элемент 5 открывается высоким потенциалом с выхода 1-ro разряда регистра 3 сдвига, поэтому на его выход проходят 40 импульсы входной последовательности все время, пока первый разряд регистра сдвига имеет высокий уровень высокого напряжения (-

Сигналы с выхода элемента 5 (фиг. З с) as периодически появляясь, поддерживают счетчик 1 в обнуленнсм состоянии.

При появлении высокого потенциала на выходе последнего разряда регис гра (, фиг. 33) происходит переключение

0 триггера 7, вызывающее прекращение выходного сигнала 4g (фиг. 3Z), т.е. появление низкого потенциала на Ч»-входе регистра, что вызывает появление низкого потенциала на выходе первого разряда регистра 3 46 (фиг. З ) и прек ращение сигнала обнуления на R-входе

36 6 счетчика 1. Таким образом, через один период после окончания выходного импульса счетчик 1 начинает работу в режиме делителя частоты. Появление высокого потенциала на инверсном выходе

Р-триггера 7, т.е. возврат устройства в, иСходное состояние» производится при прекращении действия на втором входе устройства входного сигнала 1» (фиг. 3 ).

Второй случай-появления входного сигнала „соответствует его появлению

1 (фиг-. 4 ), когда на выходе 4-го разряда регистра 3 имеется высокий потенциал (интервал -

Таким образом, введение в делитель .частоты с произвольным целым коэффициентом деления дополнительных элементов и связей позволило, кроме выполнения им основной функции — деления частоты, использовать его и как формирователь одиночного импульса по переднему фронту, сигнала, подаваемого на его второй вход, причем работа делителя частоты также синхронизирована с моментом окончания выходного сигнала.

Формула изобретения

Делитель частоты с любым целочисленным коэффициентом деления по авт. св.

N84З246,,о т л и ч а ю m и и с я тем, что, с целью расширения функциональных возможностей, в него введены

D-триггер и дополнительный элемент И,, первый вход которого соединен с выходом последнего разряда регистра сдвига; и

С-входом D- григгера, второй вход - с D- и R -входом D григгера и дополнительной входной шиной, третий вход - с выходом D--триггера, а выход - с дополнительными -входом регистра сдвига и стробирующим входом дешифратора.

В

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N84З246,,кл. Н 03 К 23/00, 06.08.79.. 953736

t2

<и

Сосгавитель О. Кружилина

Редакгор Р; Видика Техред К.Мьщьо Корректор Г. Решетник

Заказ 6293/81 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", r. Ужгоррд, ул. Проектная, 4