Компенсационно-параметрический импульсный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Соцналистнческик республик

< >954976 (61) Дополнительное к авт. свил-ву - 1" 657422 (22) Заявлено 29; 12. 80 (21) 3226392/24-07 с присоединением заявки М (23) Приоритет (5l )M. Кл.

G 05 F 1/56

9вуларстеапвй кавнтет

CCCP ев аман кзебрвтеикй. в открытий (53) УДК621.316, . 722. 1 (088. 8) Опубликовано 30.08.82 ° бюллетень РЬ 32

Дата опубликования описания 30.08.82 ь (71) Заявитель

Куйбышевский институт инженеров железнодорожного транспорта (54) КОМПЕНСАЦИОННО-ПАРАМЕТРИЧЕСКИЙ

ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО

НАПРЯЖЕНИЯ

Изобретение относится к электро- технике, а именно к импульсным ста билизаторам постоянного напряжения.

По основному авт. св. 11 657422 известен компенсационно-параметри5 ческий импульсный стабилизатор постоянного напряжения, содержащий

1 включенные последовательно в питающую шину силовой транзистор и дроссель LCD-фильтра, между обц|ей точ- to кой которых и общ ей шиной включен диод фильтра, конденсатор которого соединен с выходными выводами, соединенными с входом резисторного делителя напряжения, средняя точка которого соединена с одним .из входов сравнивающего усилителя, другой вход которого соединен с источником опорного напряжения, интегрирующую цепочку из последовательно соединенных двух резисторов и конденсатора, включенную между питающими шинами, пороговый блок, один из входов которого соединен с обц1ей точкой конденсатора, и одного из резисторов интегрирующей цепочки, а выход - с входом согласующего усилителя, одним выходом подключенного к управляющему входу силового транзистора, замыкающий транзистор, коллектор которого соединен с общей точкой резисторов интегрирующей цепочки, а эмиттер." с общей шиной, дополнительный интегрирующий преобразователь, входы которого подключены к выходу сравнивающего усилителя и к обц ей точке дросселя и диода LCD-фильтра, а выход через дополнительно введенный резис" тор соединен с другим входом порогового блока и коллектором дополнительного введенного транзистора, эмиттером соединенного с общей шиной, а базой - с другим выходом согласующего усилителя, с которым соединена база замыкающего транзистора (1) .

Однако период модуляции (Т) этого стабилизатора связан с величиной

95!г 97 где CR1И R2

К- он

3 выходног о напряжения (Uq) и определяется выражением ср г= „(к„я, с, t

rpe Uñ, Р< R2 и C параметры эпемен тов схемы.

Из приведенного выражения видно, что если напряжение U;H изменяется в значительных пределах, когда, например, стабилизатор является регули- >6 руемым, то в значительных пределах изменяется и период модуляции. По кольку сглаживающий фильтр обычно расчитывается на нижний предел частоты модуляции, то он а этом случае будет имет ь большие ма ссу и габариты. При малых значениях U, период может достигать недопустимо большой величины, По указанным причинам диапазон регулирования выходного напря- женил импульсного стабилизатора ограничен.

Цель изобретения - расширение пределов регулирования выходного напряжения стабилизатора путем стабилизации частоты модуляции.

Поставленная цель достигается тем, что в компенсационно-параметрический импульсный стабилизатор постоян" ного напряжения по авт. св. И 657М2 в пороговый блок введен дополнитель 1 ный вход, подключенный через введенный резистор к выходу сравнивающего усилителя, а через переход коллекторэмиттер введенного транзистора - к

35 общей пине, причем база этого транзистора подключена к выходу согласу" ющего усилителя.

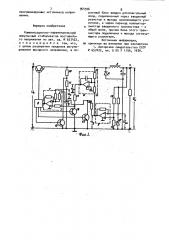

На Фиг. 1 приведена схема импульсного стабилизатора; иа фиг. 2 - графики поясняющие его работу.

Стабилизатор содержит силовую часть и схему управления. Силовая часть состоит из силового транзистора 1 и LCD-Фильтра, состоящего из диода 2, дросселя 3 и конденсатора

Схема управления включает в себя сравнивающий усилитель (CY) 5, двух" входовый интегрирующий преобразоаа" тель (ИП) б, трехвходовый пороговый элемент (ЦЭ) 7, согласующий усили56 тель 8 и интегрирующую цепочку из конденсатора 9 и резисторов 10 и 11.

К входным клеммам СУ подключены источник 12 опорного напряжения и средняя точка резисторного делителя выходного напряжения 011 из резисторов 13 и 14. Выход СУ 5 подключен к входу 15 ИП 6. Вход 16 ИП подключен

6 4 параллельно диоду 2 LCD-фильтра. Выход ИП через резистор 17 подключен к инверсному входу ПЗ 7. Параллельно этому входу ПЭ включен замыкающий транзистор I8. К одному из двух неинверсных входов ПЭ подсоединен конденсатор 9 интегрирующей цепочки.

К точке соединения резисторов 10 и

11 подсоединен замыкающий транзистор 19. К другому, дополнительному неинверсивному входу ПЭ через резистор 20 подключен вход СУ 5, параллельно этому входу подключен дополнительный замыкающий транзистор 21.

Базы замыкающих 18, 19 и 21 и силового 1 транзисторов подключены к выходам согласующего усилителя 8. Этот усилитель согласует по мощности и полярности выход ПЭ и управляющие цепи транзисторов 1, 18, 19 и 21. При отрицательном напряжении на выходе

ПЭ транзисторы l и 18 открыты, а транзисторы 19 и 21 заперты, при положительном, наоборот. ПЭ имеет один порог

1 срабатывания (0ср), равный нулю, другой (-О ) отрицательный (Фиг. 2а) .

Характерйстика ПЭ (фиг. 2а) показана для сигналов на неинверсных входах.

Стабилизатор работает следующим образом.

В интервале времени t„, когда ПЭ находится а состоянии, соответствующем нижней ветви его характеристики (Фиг. 2а), силовой транзистор 1 и замыкающий транзистор 18 открыты, а замыкающие транзисторы

19,и 21 заперты. На входе ПЭ действует напряжение Uq конденсатора 9 интегрирующей цепочки положительной полярности и выходное напряжение U|1 СУ отрицательной полярности.

Эти напряжения определяются выражениями t

"ц K{Ueq-nUp)) (2) емкость конденсатора 9 сопротивления резисторов

10 и 11 соответственно; напряжение питания стабилизатора; коэффициент усиления СУ опорное напряжение коэФФициент передачи делителя напряжения, состоящего из резисторов 13 и 1 <. о о

5 9549

Изменение напряжения на выходе И!1 в интервале t„ происходит согласно уравнению

))„(С) =+0 -»}())»-«()) -«0»ДД).;(S) где ()), - коэффициент передачи ИП.

Временные диаграммы напряжений

0 и UH приведены на фиг. 2б и в.

Пока напряжение U по величине остается меньше напряжения 0, суммарный сигнал на инверсных входах ПЭ имеет отрицательный знак, состояние

ПЭ не изменяется. Когда в момент времени t-=t< напряжение 0< достигает значения U, т.е. наступает равенство

ОпД « — 0 (C,1 0ср = 0.(4)

ПЭ срабатывает, через согласую- 2в щий усилитель запирает транзисторы

1 и 18 и отпирает транзисторы 19 и

21. Формирование интервала t закон1 чено.

Напряжение на выходе ИП при tt И ( равна .

I ))н(«)= Оср i«.J «»»-»()) -nu«))4),. ()) о

Конденсатор 9 через резистор 1 и открытый транзистор 19 разряжается до нулевого напряжения. На входе (инверсном) ПЭ действует только выходное напряжение ИП, которое, начиная с момента й=С4, изменяется под действием выходного напряжения СУ в соот- 35 ветствии с выражением

)))»() «,).u„(«,) и)» ()),Ä-»u»}u)Ä («)

Ц

Когда напряжение 0> по абсолютной величине достигает значения U ср

ПЭ срабатывает, через согласующий усилитель запирает транзисторы 19 и

21 и отпирает транзисторы 1 и 18.

Формирование интервала t законче =но. Далее процесс циклически повто.ряется.

В момент срабатывания ПЭ (t=t<+t )

C имеем

util),)=»u„() =«u„(). )+ J»(u „

""и) d< = 0" (Т) ср> где T=t<+t< - период модуляции.

Из выражений (5) и (7) получаем

t т ц»й=«J(u,„ïu„}u),. (8) 76 6

Это соотнсшение повторяет соотHàèeHíe между Uz 0оп 0н, tt и Т, ðåàë). зу емое схемой управления ст абипизатора, являющегося предметом основного изобретения, выходное напряжение стабилизатора в этом случае не зависит от напряжения питания и обеспечивается стабилизация по току нагрузки и по другим дестабилизирующим факторам.

Период модуляции Т определим иэ уравнений (4) и (8). Решая их совместно с учетом соотношения (2),получим

Т, ))))н=))„(ц, От сюда

)ц)„(). ) ()),ар )с т где 0 = — U dt - среднее на период модуляции значение выходного напряжения СУ.

Если уровень пульсаций напряжения U мал и 0) (1) Uq, то Т (й„. и 1С. . Из этого выражения видно, что пе" риод модуляции предлагаемого стабилизатора зависит только от параметров интегрирующей цепочки и не зависит от значений входного и выходного напряжений. Поэтому выходное напряжение стабилизатора можно регулировать в ши" роких пределах, не ухудшая его работу.

Это выгодно отличает предлагаемую схему от существующей.

При высоком уровне пульсаций напряжения 0 для улучшения работы стабили3 затора в схему управления между выхо" дом СУ и входом ПЭ можно включить небольшой Фильтр.

Таким образом, в результате предлагаемого усовершенствования импульсного стабилизатора без ухудшения качества стабилизации и заметного услож". нения схемы появляется возможность регулирования выходного напряжения в широком диапазоне.

Применение предлагаемого стабилизатора целесообразно в тех случаях, когда наряду с высоким КПД и высоким качеством стабилизации требуется обеспечивать регулирование а4ходного напряжения в больших пределах, например при построении универсальных высокостабильных регулируемых источников питания измерительных устройств, а также при построении программируеьех источников напряжения.

Формула изобретения

Комденсационно- параметрический импульсний стабилизатор постоянного напряжения по авт. св. Р 657422, отличающийся тем, что, с целью расширения пределов регулирования выходного напряжения, в по954976 8 роговый блок введен дополнительный вход, подключенный через введенный резистор к выходу сравнивающего усилителя, а через переход коллекторэмиттер введенного транзистора - к общей шине, причем база этого транзистора подключена к выходу согласующего усилителя.Источники информации, tO принятые во внимание при экспертизе

3. Авторское свидетельство СССР

Н 657422, кл. G 05 F 1/56, 976.

95497á .

Составитель О.Мещерякова

Техред.3.Палий

Корректор В, Бутяга

Редактор А. Мотыль

33 9 ираж 9 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 илиал ППП Патент, г. Уагород, ул. Проектная,