Квадратор

Иллюстрации

Показать всеРеферат

On ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсиик

Соцнапнстнчзсинл республик

<»>955043 (6l ) Дополнительное к авт. свид-ву (22) Заявлено 10.12.80(2l ) 3215584/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 30.08.82. Бюллетень № 32

Дата опубликования описания01.09.82 (51) М. Кд.

С1 06 F 7/552

ГееудератввлннН кемктвт

СССР ао делам лзвбрвтвнкк и еткрнткк (53 ) УД К 68 1.325 (088.8) (72) Авторы изобретения

Е. Ф. Киселев и Л. А. Кожирнова (7I ) Заявитель (54) КВАДРАТОР

Изобретение относится. к вычислительной технике и может быть использовано в в специализированных цифровых вычислительных машинах.

Известны устройства для возведения в квадрат числоимпульсных кодов flj

5 к (21

Недостатком данных устройств является низкое быстродействие. Например, в 2) каждое приращение квадрата формируется в числоимпульсном коде, что обусловливает воепроизведение функции у = х2 за время Г < 2 ", t где т период частоты представления чнслонмпульсного кода. 13

Наиболее близкий к предлагаемому квадратор $2J содержит счетчик, элемент задержки, ключи и сумматор.

Квадратор l lj реализует алгоритм . 11„=х„. =x. +gx..5+ () 2о

X„. =(x„14 5)> О где 1 = О, н — 1 — номер итерации;

8 = < — приращение аргумента.

Быстродействие алгоритма (1) определяется формулой прот -" п >о .п и . где t — период частоты следования импульсов приращения аргументаХ.

Низкое быстродействие квадратора (2g обусловлено неполным использованием функциональных возможностей сумматора.

Бель изобретения — повышение быстродействия квадратора.

Поставленная цель достигается тем, что квадратор, содержащий счетчик н сумматор, содержит дешифратор, первый и второй выходы которого подключены к входам установки сумматора, вход переноса которого соединен с шиной логической единицы квадратора, а вход младшего разряда соединен с первым входом дешифратора и с входом младшего разря» да аргумента квадратора, вход старшего разряда аргумента квадратора соединен с вторым входом дешифратора и с (q-2) входами старших разрядов сумматора, 43 4 заносятся все нули, т.е. переполнение сумматора не фиксируется, так как это не влияет на результат вычислений).

По содержимому счетчика 1 и значениям О „и 0 и формируется дополнитель- ный код Sign о х„, а по значению переноса С и дополнительному коду

Ы(п 8 Х „ — дополнительный код Д

02

2к„„8+ 8, поступающий на вход сумматора. Знак каждого из кодов определяется значением 9 и .

После окончания импульса установки квадратора на счетный вход счетчика

1 и тактовый вход сумматора поступают с входа 5 импульсы приращений (о ). .В момент окончания каждого импульса содержимое счетчика 1 увеличивается на . единицу младшего разряда (т.е. аргумент

X изменяется, соответственно, на о ), а содержимое сумматора 2 на ь„=2 „„8 6 .

После окончания М -ro импульса (б ) с выходов 10 можно снимать код равный

r х, до прихода следующего импульса установки квадратора.

Из описанного следует, что число импульсов (о ) определяется выражением

hi=

g () Х) tQ К (4)

Время вычисления функции (1) опреде ляется выражением

) (и)2 -x) t«n X) и-2 (5)

2 2 =ТтаК.

Сравнивая выражения (4) .и (5), полу чим прот, max

4. (6)

"ma x

Таким образом, быстродействие предлагаемого квадратора (см. оценку (6) выше, чем прототипа. При этом его счетчик и сумматор проще, так как .счет-: чик имеет разность (и -1), а сумматор(2П -2) (выход младшего разряда квадратора определяется младшим разрядом аргумента, а второй разряд при возведении в квадрат любого числа всегда содержит нуль).

Технико-экономическая эффективность изобретения заключается в том, что предлагаемый квадратор не сложнее прототипа, но имеет более высокое быстродействие.

3 988.0 начиная с (2n-2) по П +1 (где и — старший разряд аргумента), остальные входы сумматора подключены к выходам счетчика, вход установки которого соединен с третьим входом дешифратора и с входом установки квадратора, выходы двух младших разрядов квадратора соединены соответственно с входом младшего разряда аргумента и шиной логического нуля квадратора, (2 и -2) выходов квадратора 10 соединены с выходами сумматора, синхровходы сумматора и счетчика подключены к управляющему входу квадратора.

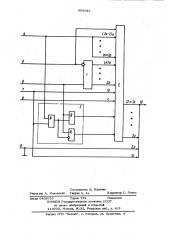

На чертеже представлена блок-схема устройства..

Квадратор содержит счетчик 1, сумматор 2, дешифратор 3, вход 4 старшего разряда аргумента, тактовый вход 5, вход 6 установки квадратора, вход 7 младшего разряда аргумента, шину 8 логической единицы, шину 9 логического нуля и выход 10 квадратора.

Предлагаемый квадратор реализует алгоритм (1) при: =2 + /) 8 (3) (а (г - i о. <) где sign 3=(-<) " — знак приращения аргумента х, ;

30 йп - разрядная цифра старшего разряда аргумен

Квадратор работает цйклически. Перед началом каждого цикла в сумматор 2 35 заносится начальная установка условия вычисления, цикл начинается с поступления на вход 6 импульса установки квадратора. В течение каждого цикла на входы 4 и 7 подаются логические сигналы 40

n«I = a „ n7 = a, определяемые разрядными цифрами соответственно старшего (a ) и младшего (а, ) разрядов кода аргумента х. По каждому импульсу установки квадратора счетчик l устанавли- 45 вается в "0", а в сумматор 2 в зависимости от Оп и Q заносится код начальных условий вычислений в соответствии с таблицей.

Вес младшего разряда сумматора по входу (выходу) равен 4, поэтому в сумматор заносятся старшие 2п -2 разряда кода х (при х., =2 "в сумматор 2 2 2п

955043

+ 2 0 0 0 0...0

+2 1 1 0 0 ... 0

0...0

0...0

0 0

0 1

-2 2 2 1 1 1

- 2 2 -.1 (2 -1) 1 1...1

О ... 0

0 ... 0

0 1

1 l

Формула изобретения

Квадратор, содержащий счетчик и сумматор, отличающийся тем, что, с целью повышения быстродействия, он содержит дешифратор, первый и второй ® выходы которого подключены к входам установки сумматора, вход переноса которого соединен с шиной логической единицы квадратора, а вход младшего разряда соединен с первым входом дешифратора и с входом младшего разряда аргумента квадратора, вход старшего разряда квадратора соединен с вторым входом дешифратора и с (tl-2) входами старших разрядов сумматора, начиная с (2n-2) по ЗО

Д + 1 (где П -старший разряд аргумента), остальные входы сумматора подключены к вьцсодам счетчика, вход установки которого соединен с третьим входом дешифратора и с входом установки квадратора, вьцсоды двух младших разрядов квадратора соединены соответственно с входом младшего разряда аргумента и шиной логического нуля квадратора, (2 и-2) выходов квадратора соединены с выходами сумматора, синхровходы сумматора и счетчика подключены к управляющему входу квадратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

%,703806; кл. C j06 F 7/552, 1979, 2. Авторское свидетельство СССР

Ж475619, кл. 9 06 F 7/552» 1975.

955043

Составитель Е. Киселев

Редактор А. Маковская Техред А. Ач Корректор Е. Рошко

Закаэ 6438/53 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открьгтий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4