Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Специальное конструкторское бюро промьшлейной автоматики (7I ) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к автоматике и вычислительной. технике и может ать использовано в оконечных устройствах автоматизированных систем управления, а также в универсальных и специализиро. ванных цифровых вычислительных машинах.

Известно микропрограммное устрой- . ство управления с использованием микрокоманд переменного формата, содержащее два блока памяти для хранения микрокоманд соответственно с четными и нечетными адресами, входы блоков памя- . ти соединены с выходами двух адресных регистров. Содержимое регистров определяется видом выполнения микрокомаид, а таиже четносгью либо нечетностью ее адреса (1J .

Недостатками данного устройства являются большой обьем оборудования и невсзможность использования одного и того же поля микрокоманды по различным смысловым назначениям.

Наиболее близким к предлагаемому по технической сущности является микроп рог. раммное устройство, содержащее регистр адреса, блок памяти, блоки элементов И и регистры микрокоманд P)

Недостатком такого устройства является то, уго под индикаторные разряды, не имеющие смыслового значения отведен определенный объем блока памяти. 1О

Hem. изобретения — экономия оборудования.

Поставленная цель достигается тем, что в микропрограммном устройстве управпения, содержащем регистр адреса, блок памяти, 2п блоков элементов И (где tl - число зон в блоке памяти) и

2 П регистров микрокоманд, причем группа разрядных выходов регистра адреса соединена с группой адресных входов ра блока памяти, каждый i -ый выход блока памяти, кроме адресного, соединен с первым входом i -го (1+1)-го блока элементов И, выходы которых соединены с входами соответствующих регистров

3 9550 микрокоманд, выходы которых являются информационными выходами устройства, адресный выход- блока памяти соединен с .входом регистра адреса, первый и (й-1)-ый выходы регистра адреса соединены со вторыми выходами с первого до д -го и с (П+1)-го до 2 Yl -ro блоков элементов И соответственно.

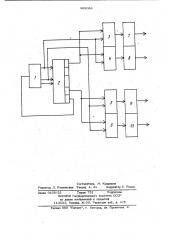

На чертеже приведена блок-схема устройства. 10

Устройство содержит регистр 1 адреса, блок 2 памяти, блоки 3-6 элементов И, регистры 7-10 микрокоманд и информационные выходы 11 устройства.

Предлагаемое устройство работает 15 следующим образом.

В регистре 1 содержится адрес микрокоманды, подлежащей выполнению. С выходов регистра 1 код адреса микрокоманды поступает на входы блока 2, на выходах которого появляется код микрокоманд.

При этом коды зон микрокоманды с переменным смысловым значением поступают на соответствующие входы блоков

3-6 элементов И на другие входы которых подак гся сигналы с регистра 1, соответствующие адресу микрокоманды. В зависимости от значения сигналов с выходов регистра адреса 1 открываются соответствующие блоки элементов И, блок элементов ИЗ или блок элементов И4 и блок элементов И5 или блок элементов

И6. При этом коды зон микрокоманды с переменным смысловым значением за35 писываются соответственно в регистр 7 микрокоманды или в регистр 8 микрокоманды и в регистр 9 микрокоманды или в регистр 10 микрокоманды..Сигнал, соответствующий коду зоны следующего адреса микрокоманды, поступает с адресного выхода блока 2 на вход регистра 1 адреса.

Ьь 4

Использование в качестве индикаторных разрядов микрокоманды отдельных разрядов адреса позволяет сократить длину поля микрокоманды, а следовательно, и объем памяти микропрограмм.

Применение изобретения позволяет за счет использования в качестве инди-. каторных разрядов отдельных разрядов регистра адреса, сократить объем блока памяти.

Формула из о бретения

Микропрограммное устройство управления, содержащее регистр адреса, блок памяти, 2й блоков элементов И (где П число зон в блоке памяти) и 2П регист- . ров микрокоманд, причем группа разрядных выходов регистра адреса соединена с группой адресных входов блока памяти, каждый < .-ый выход которого, кроме адресного, соединен с первым входом 3 -го (+1)-го блока элементов И, выходы которых соединены с входами соответствующих регистров микрокоманд, выходы которых являются информационными выходами устройства, адресный выход блока памяти соединен с входом регистра ! адреса, о т л и ч а ю щ е е с я тем, что, с целью экономии оборудования, первый и (tl-1)-й выходы регистра адре

1 са соединены со вторыми входами с первого до q -го и с (t1+1)-го до 2й-го блоков элементов И соответственно.

Источники информации, принятые во внимание при экспертизе

1. Заявка Японии % 54-10220, кл. 97(7), 1979.

2. Заявка Японии М 58-22826, кл. 97(7), 1978 (прототип).

955056

Составитель М. Кудряшев

Редактор Л. Пчелинская Техред А. Ач Корректор E. Рош о

Заказ 6438/53 Тираж 731 Поддисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4