Устройство для контроля цифровых систем

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советск ик

Социалистических

Республик („)955073 (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.06.80 (21) 2947164/18-24 (51) М. Кл. б 06 F 11/16 с присоединением заявки №вЂ”

Гасударственный кюмнтет (23) Приоритет—

СССР

Опубликовано 30.08.82. Бюллетень №32

Дата опубликования описания 30.08.82 (53) УДК 681.326..7 (088.8) вв делам нзабретеннй н аткрмтнй (72) Авторы изобретения

Ю. 3. Горелик, В. В. Мит (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СИСТЕМ

Изобретение относится к вычислительной технике и может найти применение для контроля цифровых систем (ЦС) универсального или специального назначения.

Известны устройства для контроля ЦС, содержащие матрицу команд, регистры ввода-вывода команд и ответных реакций и блок индикации (1) и (2).

Недостатки таких устройств — невозможность осуществления контроля не в реальном масштабе времени, ручная индикация результатов контроля и отсутствие диагностических возможностей.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля цифровых систем, содержащее блок задания регистров, матрицу команд, 15 счетчик, блок переключения частоты опроса, блок управления, блок формирующих усилителей и блок индикации состояния аппаратуры контролируемой цифровой системы (3).

Недостатками известного устройства для контроля ЦС являются отсутствие возможности определения неисправного объекта контроля по времени возникновения сигнала о его неисправности, ручная инициация процедуры контроля, проводимой не в реаль2 ном масштабе времени (в специальном режиме), и необходимость наличия в контролируемой аппаратуре специально организованных контрольных цепей для введения в- них импульсов из устройства контроля.

Цель изобретения — расширение функциональных возможностей устройства за счет обеспечения возможности определения неисправного объекта системы по времени возникновения сигнала о его неисправности.

Указанная цель достигается тем, что в устройство для контроля цифровых систем, содержащее блок задания режимов, блок памяти команд и коммутатор, причем первый выход блока задания режимов соединен со входом блока памяти команд, выход которого соединен с первым входом коммутатора, группа выходов коммутатора соединена со входами контролируемой системы группа входов коммутатора соединена с группой выходов контролируемой системы, введены блок памяти констант, счетчик импульсов и блок формирования адреса неисправности, содержащий регистр команд, регистр кодов времени, блок памяти неисправности и регистр результата, причем выход блока памяти команд, первый выход

955073

З0

35 0

55 счетчика импульсов, второй, третий и четвертый выходы блока задания режимов соединены соответственно с информационным входом регистра команд, информационным входом регистра кодов времени, управляющим входом регистра команд, управляющим входом регистра кодов времени и управляющим входом регистра результата блока формирования адреса неисправности, выход регистра результата соединен со вторым входом коммутатора, первый и второй выходы коммутатора соединены соответственно с первым и вторым входами блока задания режимов, первый и пятый выходы которого соединены соответственно со входом блока памяти констант и первым входом счетчика импульсов, выход блока памяти констант соединен со вторым входом счетчика им-. пульсов, второй выход которого соединен с третьим входом блока задания режимов, причем в блоке формирования адреса неисправности информационные выходы регистра команд соединены с первой группой входов блока памяти неисправностей, информационные выходы регистра кодов времени соединены со второй группой входов блока памяти неисправностей, информационные выходы которой соединены с группой входов регистра результатов.

Блок задания режимов содержит счетчик импульсов, дешифратор, первый и второй элементы ИЛИ, триггер, элемент,И, генератор импульсов и элемент задержки, причем первый вход блока соединен с информационными входами счетчика импульсов, выходы которого соединены с группой входов дешифратора, выходы дешифратора соединены со входами первого элемента ИЛИ и являются первым выходом блока, выход первого элемента ИЛИ соединен с первым входом триггера и является вторым выходом блока, второй вход блока соединен с первым входом второго элемента ИЛИ и входом элемента задержки, первый и второй выходы которого являются соответственно третьим и четвертым выходами блока, третий вход блока соединен с управляющим входом счетчика импульсов и вторым входом второго элемента ИЛИ, выход которого соединен со вторым входом триггера, выход генератора импульсов соединен с первым входом элемента И, выход триггера соединен со вторым входом элемента И, выход которого является пятым выходом блока.

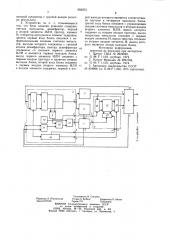

На чертеже представлена блок-схема предл а гаем о го устрой ств а.

Устройство содержит счетчик 1, блок 2 задания режимов, блок 3 памяти команд, коммутатор 4, блок 5 формирования адреса неисправности и блок 6 памяти.

Блок 2 предназначен для задания режимов работы и выработки сигналов управления и включает в себя счетчик 7, информационным входом связанный с первым входом, счетным входом — с третьим вхо4 дом блока 2, а выходом — с дешифратором 8, выход которого соединен со входами элемента ИЛИ 9 и первым выходом блока 2.

На один вход триггера 10 поступает сигнал с выхода элемента ИЛИ 9, а на другой — с выхода элемента ИЛИ 11. Элемент

И 12 одним входом подключен к выходу генератора 13 импульсов, другим — к выходу триггера 10, а своим выходом — к пятому выходу блока 2 задания режимов. К третьему и четвертому выходам этого блока подсоединены выходы элемента 14 задержки, вход которого подключен ко второму входу блока 2.

Блок 5 предназначен для выработки адреса неисправности и содержит блок 15 памяти, регистр 16 команд и регистр 7 кодов времени, подключенные ко входам блока 15 памяти, и регистр 18 результатов, подключенный к его выходам. Информационный и управляющий входы регистра 16 и информационный и управляющий входы регистра

17 соединены соответственно с первым, третьим, вторым и четвертым входами блока 5 формирования адреса неисправности, выход которого подключен к выходу регистра 18, а пятый вход — к упра вляющему входу этого регистра.

Предлагаемое устройство работает следующим образом.

ЭВМ цифровой вычислительной системы инициирует начало проведения контроля объектов в системе путем выдачи в устройство адреса первой команды, которая должна поступить в систему. Код адреса от ЭВМ поступает через первый выход коммутатора 4 на первый вход блока 2 задания режимов и на информационный вход счетчика 7 этого блока. С выхода счетчика 7 информация поступает на дешифратор 8, выходы которого подключены через первый выход блока 2 ко входу блока 3 памяти команд и блока 6 памяти констант, и, следовательно, по сигналу на соответствующей возбужденной шине происходит считывание первой контрольной команды в систему из блока 3 памяти команд. через коммутатор 4 и константы в счетчик 1 из блока 6 памяти констант (константа указывает длительность до момента выдачи очередной команды). Кроме этого, при возбуждении любой шины дешифратора 8 срабатывает элемент ИЛИ 9, обеспечивая запись в регистр 16 блока 5 команды выдаваемой в систему (сигнал записи поступает по тракту: выход элемента ИЛИ 9, второй выход блока 2, третий вход блока 5, код команды поступает на регистр 16 с первого входа блока 5). Сигнал с выхода элемента ИЛИ 9 устанавливает триггер 10 в состояние, при котором потенциал на его выходе обеспечивает подбор на втором входе элемента И !2, разрешая прохождение импульсов от генератора 13 на пятый выход блока 2, который соединен со счетным вхо955073

1О

Формула и зобретения

l5 дом счетчика 1. Таким образом, в систему выдается первая контрольная команда, в счетчике 1 находится код константы, определяющей время до выдачи очередной команды, и, кроме этого, на счетчик начали поступать импульсы для отсчета этого времени. Если за время отсчета пришел сигнал из системы о неисправности, он поступает со второго выхода коммутатора 4 на второй вход блока 2 задания режимов. Со второго входа блока 2 сигнал о неисправности поступает как через элемент ИЛИ ll на триггер 10, сбрасывая его и тем самым прекращая прохождение импульсов на счетчик 1, а следовательно, и отсчет временного интервала, так и на вход элемента 14 задержки с которого через время 1 и третий выход блока 2 на четвертый вход блока 5 поступает управляющий сигнал, обеспечивающий запись кода со счетчика 1 в регистр 17 блока 5.

Следовательно, на блок 15 памяти неисправностей блока 5 поступают информации с регистра 16 блока 2 (в котором хранилась выдаваемая команда) и с регистра 17 блока 2, на котором появилась информация со счетчика, свидетельствующая о длительности временного интервала, не сосчитанного счетчиком 1, так как пришел сигнал о неисправности. На основании информации, поступившей с указанных регистров, из блока 15 в регистр 18 блока 2 по сигналу с выхода элемента 14 задержки (время )

) "ь ) блока 2 через четвертый выход этого блока и пятый вход блока 5 считывается код. Этот код указывает адрес наиболее вероятного места возникновения неисправности в приборах системы и поступает на вход ЭВМ через коммутатор 4.

Если во время отсчета сигнал из системы о неисправности не приходит, то с выхода 2 счетчика 1 снимается сигнал, свидетельствующий о прохождении счета через «О», т. е. интервал отсчитан, и поступает через третий вход блока 2 и элемент ИЛИ 11 на сброс триггера 10, тем самым прекращает счет. Сигнал с третьего входа также поступает на счетный вход счетчика 7 блока

1 (используется для модификации адреса, т. е. увеличивает его на + 1), и процесс начинается после дешифрации сначала.

Технико-экономическое преимушество предлагаемого устройства заключается в том, что оно обеспечивает значительное расширение возможности устройства, так как реализует автоматическое начало процедуры контроля по команде из ЭВМ системы с любого адреса, имеющегося в памяти устройства, и изменение этого адреса в процессе работы, позволяет легко наращивать объем проверок и вести их с большой скоростью и достоверностью без участия в процессе контроля ЭВМ системы, как правило специализированной и имеющей ограниченный объем памяти и загруженную логико-вре20

25 зо

З5

4О

55 менную диаграмму. При этом сигнал с аппаратных средств контроля используется не только для фиксации факта неисправности, а также для идентификации места ее возникновения, что кроме расширенных возможностей устройства позволяет на процедуру поиска адреса отказавшего оборудования не тратить ресурс ЭВМ системы. Кроме того, очевидна простота подключения устройства к объектам контроля и отсутствие необходимости введения в последнее дополнительных контрольных трактов и специального оборудования.

1. Устройство для контроля цифровых систем, содержащее блок задания режимов, блок памяти команд и коммутатор, причем первый выход блока задания режимов соединен со входом блока памяти команд, выход которого соединен с первым входом коммутатора, группа выходов коммутатора соединена со входами контролируемой системы, группа входов коммутатора соединена с группой выходов контролируемой системы, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности определения неисправного объекта системы по времени возникновения сигнала о его неисправ-ности, в него введены блок памяти констант, счетчик импульсов и блок формирования адреса неисправности, содержащий регистр команд, регистр кодов времени, блок памяти неисправностей и регистр результата, причем выход блока памяти команд, первый выход счетчика импульсов, второй, третий и четвертый выходы блока задания режимов соединены соответственно с информационным входом регистра команд, информационным входом регистра кодов времени, управляющим входом регистра команд, управляющим входом регистра кодов времени и управляющим входом регистра результата блока формирования адреса неисправности, выход регистра результата соединен со вторым входом коммутатора, первый и второй выходы коммутатора соединены соответственно с первым и вторым входами блока задания режимов, первый и пятый выходы которого соединены соответственно со входом блока памяти констант и первым входом счетчика импульсов, выход блока памяти констант соединен со вторым входом счетчика импульсов, второй выход которого соединен с третьим входом блока задания режимов, причем в блоке формирования адреса неисправности информационные выходы регистра команд соединены с первой группой входов блока памяти неисправностей, информационные выходы регистра кодов времени соединены со второй группой входов блока памяти неисправностей, информационные выходы

955073

Составитель И. Сигалов

Редактор,Л. Пчелинская Техред А. Бойкас Корректор О. Билак

Заказ 6171/54 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, % — 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4 которой соединены с группой входов регистра результата.

2. Устройство по п. 1, отличающееся тем, что блок задания режимов содержит счетчик импульсов, дешифратор, первый и второй элементы ИЛИ, триггер, элемент

И, генератор импульсов и элемент задержки, причем первый вход блока соединен с информационными входами счетчика импульсов, выходы которого соединены с группой входов дешифратора, выходы дешифратора соединены со входами первого элемента

ИЛИ и являются первым выходом блока, выход первого элемента ИЛИ соединен с первым входом триггера и является вторым выходом блока, второй вход блока соединен с первым входом второго элемента ИЛИ и входом элемента задержки, первый и второй выходы которого являются соответственно третьим и четвертым выходами блока, третий вход блока соединен с управляющим входом счетчика импульсов и вторым входом второго элемента ИЛИ, выход которого соединен со вторым входом триггера, выход генератора импульсов соединен с первым входом элемента И, выход триггера соединен со вторым входом элемента И, выход которого является пятым выходом блока.

1О

Источники информации, принятые во внимание при экспертизе

l. Г атент США № 2824923, кл. G 06 F 11/10, опублик. 1974.

2. Патент Франции № 2201784, кл. G 06 F 11/10, опублик. 1974.

3. Авторское свидетельство СССР № 404089, кл. G 06 F 11/02, 1973 (прототип) .