Распределитель импульсов с обнаружением ошибок

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (>1)955074 (61) Дополнительное к авт. саид-ву— (22) Заявлено 01.08.80 (21) 2966777/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

С 06 F 11/18

G 06 F 1/04

Гееудеретееннмк немнтет

СССР (53) УДК 681.326 (088.8) Опубликовано 30.08.82. Бюллетень №32

Дата опубликования описания 30.08.82 по делам нзебретеннй н еткрмтнй (72) Авторы изобретения

А. А. Иванов и В. В. Смородинский (71) Заявитель (54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

С ОБНАРУЖЕНИЕМ ОШИБОК

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках синхронизации ЦВМ повышенной надежности.

Известен распределитель импульсов на кольцевом сдвигающем регистре с самовосстановлением нормального функционирования после ошибки (1) .

Однако этот распределитель не вырабатывает внешнего сигнала о появлении ошибки и поэтому не обеспечивает исправления искажений информации в других узлах ЦВМ, вызванных ошибкой в распределителе.

Известно также устройство для обнаружения ошибок в регистре сдвига, обнаруживающее ошибку и выдающее соответствующий внешний сигнал (2).

Однако контроль по модулю два, применяемый в этом устройстве, не позволяет обнаруживать ошибки четной кратности (например, появление в регистре трех единиц вместо одной).

Наиболее близким к предлагаемому является распределитель импульсов с обнаружением ошибок, содержащий и-разрядный кольцевой сдвигающий регистр, выход разряда п которого соединен с первыми входами

2 элемента И и первого элемента ИЛИ, вторые входы которых соединены с выходом второго элемента ИЛИ, входы которого соединены с выходами всех разрядов регистра, кроме разряда и. Контроль основан на том, что в каждом такте должна возбуждаться одна и только одна выходная шина распределителя. Если регистр не содержит единиц, то на выходе первого элемента ИЛИ появляется нулевое значение сигнала. Если регистр содержит более одной единицы, то на выходе элемента И появляется логическая единица (3).

Однако данный распределитель и другие известные распределители имеют недостаток, заключающийся в том, что при возникновении ошибки на выходы распределителя проникают ложные сигналы, которые могут исказить информацию в других узлах ЦВМ.

В последующих тактах, даже несмотря на обнаружение ошибки и восстановление нормального функционирования распределителя, распространение искаженной информации может привести к непредсказуемому и необратимому нарушению вычислительного процесса раньше, чем смогут быть введены в действие программные средства восстанов955074

10 соединен с выходом элемента И, выход мажоритарного элемента соединен со входом 40 жоритарный элемент 4, тактируемый К$-триг- 50

3 ления. Наиболее вероятным источником такого нарушения является запись в оперативную память ЦВМ искаженной информации по произвольному адресу. Поэтому первым шагом к восстановлению нормальной работы ЦВМ в случае ошибки в распределителе является запрет выдачи распределителям импульса, по которому осуществляется запись в оперативную память. Рассмотренные известные распределители не обеспечивают такого запрета.

Цель изобретения — повышение надежности распределителя.

Поставленная цель достигается тем, что в распределитель импульсов с обнаружением ошибок, содержащий п-разрядный регистр сдвига, элемент ИЛИ, элемент ИЛИ-НЕ, причем выход элемента ИЛИ-НЕ соединен с информационным входом первого разряда регистра сдвига, вход синхронизации которого является синхровходом распределителя, выходы разрядов 1 — (п — 1) регистра сдвига являются информационными выходами распределителя, выход элемента ИЛИ соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом (и — 1)-ro разряда регистра сдвига, выходы разрядов с первого по (п —, 2) которого соединены соответственно со входами элемента ИЛИ, введены тактируемый RS-триггер, элемент И и мажоритарный элемент, первый вход которого соединен с выходом элемента ИЛИ, второй вход мажоритарного элемента соединен с выходом (п — 1) -го разряда регистра сдвига, выход и-разряда которого соединен с третьим входом мажоритарного элемента и с первым входом элемента И, второй вход которого соединен с входом тактируемого RS-триггера и является выходом сигнала ошибки распределителя, вход запрета по ошибке которого установки в «О» тактируемого RS-триггера, вход установки в «1» которого является управляющим входом распредеителя, синхровход которого соединен с синхровходом тактируемого RS-триггера.

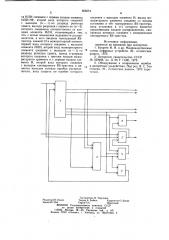

На чертеже приведена схема предлагаемого распределитея.

Распределитель импульсов с обнаружением ошибок содержит регистр I сдвига, элемент ИЛИ 2, элемент ИЛИ-НЕ 3, магер 5 и элемент И 6.

Распределитель работает следующим образом.

В исходном состоянии, при отсутствии ошибок, в регистре 1 хранится и, по мере поступления на вход синхронизации распределителя тактовых импульсов, сдвигается по направению к выходу и регистра 1 одна и только одна единица. Пока эта единица

25 зо

4 находится на любом из выходов регистра 1, кроме выхода и, она поступает на один из входов элемента ИЛИ 2 либо элемента

ИЛИ-НЕ 3. При этом на информационном входе первого разряда регистра 1 сохраняется нулевое значение сигнала, и регистр заполняется нулями по мере поступления тактовых импульсов. Когда единица появляется на выходе п регистра 1, а на остальных выходах регистра 1.остаются нули, на информационный вход первого разряда регистра поступает единица, которая и записывается в него очередным тактовым импульсом.

При отсутствии ошибок на выходе мажоритарного элемента 4 сохраняется нулевое значение сигнала, тактируемый RS-триггер 5 сохраняет исходное единичное состояние, импульс выхода и регистра 1, стробирующий запись в память ЦВМ, беспрепятственно поступает со входа элемента И 6 на его выход. В случае обнаружения ошибки (появление в регистре более одной единицы) триггер 5 перебрасывается в нулевое состояние единичным импульсом с выхода мажоритарного элемента 4 и запрещает выдачу импульсов элементом И 6, предотвращая необратимое искажение информации в памяти ЦВМ. Нулевой уровень с выхода триггера 5 является выходным сигналом распределителя, указывающим на наличие ошибки. Поступающий на управляющий вход распределителя (на вход установки единицы триггера 5) сигнал о завершении процесса восстановления нормальной работы

ЦВМ устанавливает триггер 5 в единичное состояние и вновь разрешает выдачу импульсов стробирования записи в память ЦВМ.

В отличие от известных распределителей предлагаемый распределитель предотвращает необратимое нарушение вычислительного процесса ЦВМ при сбоях синхронизации, что позволяет избежать полной перезагрузки программ и обеспечивает быстрое автономное восстановление нормальной работы

ЦВМ программными средствами, существенно повышая надежность необслуживаемых систем, систем, работающих в реальном масштабе времени, а также сокращает потери машинного времени на восстановление в обслуживаемых системах, Формула изобретения

Распределитель импульсов с обнаружением ошибок, содержащий и-разрядный регистр сдвига, элемент ИЛИ, элемент

ИЛИ-НЕ, причем выход элемента ИЛИ-НЕ соединен с информационным входом первого разряда регистра сдвига, вход синхронизации которого является синхровходом распределителя, выходы разрядов 1 — (и — 1) регистра сдвига являются информационными выходами распределителя, выход элемен955074

Составитель Н. Торопова

Редактор Ю. Ковач Техред А. Бойкас Корректор О. Билак

Заказ 6171 54 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и от крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 та ИЛИ соединен с первым входом элемента

ИЛИ-НЕ, второй вход которого соединен с выходом (и — 1)-но разряда регистра сдвига, выходы разрядов с первого по (и — 2) которого соединены соответственно со входами элемента ИЛИ, отличающийся тем, что, с целью повышения надежности распределителя, в него введены тактируемый RSтриггер, элемейт И и мажоритарный элемент, первый вход которого соединен с выходом элемента ИЛИ, второй вход мажоритарного элемента соединен с выходом (и — 1) -го разряда регистра сдвига, выход и-разряда которого соединен с третьим входом мажоритарного элемента и с первым входом элемента И, второй вход которого соединен с выходом тактируемого RS-триггера и является выходом сигнала ошибки распределителя, вход запрета по ошибке которого соединен с выходом элемента И, выход мажоритарного элемента соединен со входом установки в «О» тактируемого RS-триггера, вход установки в «1» которого является управляющим входом распределителя, синхровход которого соединен с синхровходом тактируемого RS-триггера.

Источники информации, принятые во внимание при экспертизе

1. Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., «Советское радио», 1975.

2. Авторское свидетельство СССР

Мв 529488, кл. G 06 F 11/00, 1975.

3. Обнаружение и исправление ошибок в дискретных усьройствах. Под ред. В. С. Толстякова, М., «Советское радио», 1972 (прототип) .