Интегратор

Иллюстрации

Показать всеРеферат

В. Н. Лапенко, С. Д. Павликов и И. К. Герасий (72) Авторы иэобретения

Московский институт электронной техники (7! ) Заявитель (54) ИНТЕГРАТОР

Изобретение относится к вычислительной технике и может быть использовано в устройствах автоматики и измерительной техники, в частности коррелометрах, автокоррелометрах, анализаторах.

Известны компенсационные интегриру5 ющие цепи (интегрирующие усилители), состоящие из оцерационного усилителя с емкостной отрицательной обратной связью и токозацающего резистора (1) .

При использовании интегрирующих усилителей в качестве усредняющего устройства для обеспечения малых ошибок.необходимо, чтобы выходное напряжение интегратора на конечном интервале интегрирования лежало в оцрецеленном динамическом диапазоне, близком к верхней границе работы следующего за ним устройства - аналогового целителя или аналого-цифрового преобразователя (АБП) с ро регулируемым опорным напряжением.

Таким образом, цля обеспечения высокой точности измерения необходимо заранее знать среднее значение измеряемого . сигнала и выбрать соответствующую постоянную времени. В устройствах, прецнаэначенных цля исследования случайных стационарных rrpateccos, в частности, при. измерении корреля в онных функций, расцрецеления вероятносгей, средней мсщности, дисперсии и спектральной плотности мощности сцучайных величин среднее значение измеряемого сигнала заранее неиэ вестно даже ориентировочно и можег меняться в десятки раз. Постоянная времени выбирается такой, чтобы максимальное значение выходного сигнала не превышало динамического диапазона последующего устройства, т.е. она оптимальна цри измерении максимальных значений и на. несколько цорядков больше, чем необходимо при измерении минимальных сигналов. Поэтому при измерении вышеуказанных параметрах с малыми средними значениями точность измерения катастрофически падает.

3 9551

Точность усреднения может быть повышена при использовании в АБП усилителя с программным коэффициентом усиления (2(.

Однако aro усложняет устройство и . повышает etо стоимость.

Наиболее близким к предлагаемому является интегратор, содержащий токозадаюшую цепь, выходом сьязанную с входом усилителя, ь цепи отрицательной об- 10 ратной связи, которого ьключены последовательно соединенные делитель напряжения и конденсатор. г

Е! остоинстьом данного интегратора яв- И ляется простота, а также возможность подстройки при помощи делителя постоян-. ной интегрировапия, вызьанной, разбросом емкости конденсатора. При этом необходимо отметить, что абсолютная величина 20 переменного резистора, используемого h качестве делителя, не влияет на точность интегратора, которая зависит только от отношения плеч переменного резистора, т.е. от коэффициента передачи делителя(31,23

Недостатком интегратора является низкая точность при измерении случайных процессов, так как заранее неьозможно знать среднее значение измеряемого сигнала и установить необходимую величину З0

1 постоянной времени интегрирования.

Цель изобретения - повышение точности интегрирования.

Постаьленная цель достигается тем, что в интегратор, содержащий токозадаю» З щую цепь, подключенную к вхоцу операционного усилителя, выход которого является выходом интегратора, и интегрирующий конденсатор, одна обкладка. которого подключена к входу операционного усилителя, 40 введены блок с переменным коэффициентом передачи и блок управления, вход которого п.одключен к выходу операционного усилителя, а выход соединен с упраьляющим входом блока с переменным коэффициентом 4 передачи, включенным между другой обкладкой интегрирующего конденсатора и выходом операционного усилителя, при этом блок управления содержит схему сравнения, один из входов которой являет- >0 ся первым входом блока управления, другие входы соединены с выходами источника опорных напряжений, а ьыход подключен к информационному входу сцвигоього регистра, тактирующий вход которого сое- я динен с генератором тактовых импульсов, установочный вход сдьигоього регистра и вход разрешения являются соответственно

06 4 установочным входом и входом разрешения блока управления.

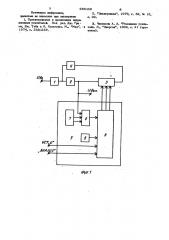

На фиг. 1 риведена функциональная схема интегратора; на фиг. 2 - ьременная диаграмма работы интегратора.

Интегратор содержит токозадающую цепь 1, операциснный усилитель 2, блок

3 с переменным коэффициентом передачи

3, интегрирующий конденсатор 4, блок 5 управлени я.

Выход операционного усилителя 2 свя-, ВаН с сигнальным входом блока 3 с переменным коэффициентом передачи (например, аттенюатором) и с сигнальным ьхо« дом блока 5 управления, выходы которого подключены к управляющим входам блока 3 С Переменным коэффициентом передачи, выход которого через интегрирующий конденсатор 4 соединен с входом операционного усилителя 2 и выходом токозадающей цепи 1. ,Блок 5 управления содержит схему 6 сравнения, источник 7 опорных. напряжений, сдвиговый регистр 8, генератор 9 тактовых импульсоь.

Вход схемы 6 сраьнения связан с источником 7 опорных напряжений, а выходс входом сдвигового регистра 8, другой вход которого подключен к генератору 9 тактовых импульсов.

Интегратор работает следующим образом.

Одновременно с началом режима интегрирования (усреднения) (момент времени, фиг. 2), на управляющий вход блока

5 управления приходит импульс начальной установки, который блокирует сдвиг и устанаьливает в нулевое состояние сдвиговый регистр 8, при этом иа единичном входе его младшего разряда псстоянно присутствует единица. Информация о состоянии каждого разряда регистра 8 с его выходов поступает на управляющие входы блока 3 с переменным коэффициентом передачи (аттенюатора), В результате чего коэффициент передачи блока 3 устанавливается максимальным и равен К,!, причем в режиме интегрирования (момент от 1о до q ) коэффициент передачи блока

3 остается неизменным до прихода сигнала разрешения анализа на управляющий вход блока 5 управления. В момент времени,! процесс интегрирования (усреднения) заканчивается и интегратор переходит в режим хранения. К этому моменту времени напряжение на конденсаторе 4 достигает величины e,, a напряжение íà вь1хопе усилителя 2 - величины В = 9o/К .Начальное значение постоянной времени интег5 955106 d ратора р е выбирается таким, чтобы максима- тегрирования. В интересующ м "ас Ре у r яжение ная величина В лежала в линейной об- ме Хранение дополнительное напряже ласти усилителя 2 и не превышала его ди- ошибки, возникающее за счет паденил нанамического диапазон.а. далее напряжение пряжения тока заряда конд с выхода усилителя 2 поступает на си 1 выходном сопротивлении блока 3i Р авно О, Iнальный вход блока 5 управления, т.е. На т.е. в этом режим т Р о ок за яда авен О вход схемы 6 сравнения, на второй вход (входным током Оу IIpeHe6peraev) ° кото ого подается напряжениебН !,с источ- жиме интегрирования эту КУ оши6 можн о ка 7 о рных напряжений. Схема 6 срав- свести к минимуму соответствующим ы нения осуществляет сравнение по модулю 1Î бором аттенюат ора (блока ) напряжения 6 с напряжением н,гр ° т е выходным сопротивлением.

6 сравнения описывается . 1 аким образом благодар следующим выражением .блока 3 с переменным коэффициентом передачи и введению блока управления пэ1, если le. l(e явилась возможность изменять после интер-! „вала интегрирования постоянную времени, 0 если!e !) о н. гр.z с которой происходило интегрирование, 1то

ПозВоляет Выбрать онтимальные постояш1ые сравнения. интегрирования при усреднении случайных сли б лежит ниже нижней границы 0 Параметров, вслепствие чего точпость пс о

Е> желаемого динамического диапазоН,гр вышается. на работы (в котором обеспечивается тре Стоимость известных устройств с аналогичными точностными характеристиказапрета на выходе сХемы 6 сравнения от- и ца 200 300 в,ше сутствует. 2S

Одновременно с началом режима хранения на другой управляющий вход блока Формула изобретения

5 управления приходит сигнал разрешения анализа в результате чего с частотой 1. Интегратор, содержащий токозадаследованиЯ генератоРа 9 тактовых импУ- ченну к о пе а льсов осуществляется последовательное ционного усилителя, выход которого являeTcR выходом интегратОра и интегрируюрегистре 8 в направлении от младшего к старшему и соответственно происходит сну- щ и пенчатое уменьшение коэффициента переда- и „ с целью повышения точности интегриро3S

5 и т Д. ПРи этом напРЯжение на выхо«вания, в него введены блок.с перемен11ым пе усилителя 2 будет ступенчато возрас-, и н и щ тать (фиг. 2). вХод которого подключен к выхопу операционного усилителя, а выход соединен с

О 4О выходе УсилителЯ 2 пРевысит юн.гр, т, р им входом блока с переме ым коэффициентом передачи включенным межси "ал запрета кот Р"й " -тУ" ет на д,у другой Обкладкой интегрирующего к сдвигового регистра 8, и сдвиг единицы в нем и, соответственно, изменение коэффициента передачи блока 3 (аттенюатора) прекращается. 2. Интегратор по и. 1, о т л и ч аПри изменении коэффициента передачи ю шийся тем, что блок управления соблока 3 с К до Kg или К напряжение держит схему сравнения, один из входов на выходе блока 3 пРактически не изме«которой является первым входом блока упНнтСЯ, таК КаК ОНО ОПРЕДЕЛЯЕТСЯ НаПРЯжЕ- >О ра„ленин д,у,.„е вход соединены с вы» нием, до котоРого зарнжзн конденсатоР 4 ходами источника опорных напряжений, а

Напряжение на выходе усилителя будет выход подключен к информационному входу равно сдвигового регистра, тактирующий вход О О е -е,(8д которого соединен с генератором тактовых („ импульсов, установочный вход сдвигового т.е. увеличится в — раз, что эквивалентно уменьшению постоянной времени регистра и вхоtl р зр

У и вхо а ешения являются со!

, ответственно установочным входом и вхоинтегРатоРа в,— Раз пеРед началом ин- дом разрешения блока уп„авлен

955 106 8

2, «Электроника», 1979, т. 52, Nt 15, с. 99.

Источники информации, принятые ю внимание щж аксиертиее

1. Проектирсвание и применение оиера. ционных усилителей, .Пои ред. Йж. Гре. 3. Чесноков А. А. "Решавшие усилима, Лж. Тоби и Л. Хьвсмана. М., Мир,,з тели, Л., «Энергия, 1968, с. 21 (про

1974, с. 233-239, тотии).

Составитель. С. Белан

Редактор С. Тараненко Техред ТМаточха Корректор Г. Огао

Заказ 6440/56 Тираж 73 1 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„д. 4/5

Филиал ППП «Патент, r. Ужгород, ул. Проектная, 4