Обучающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социапистическик

Респубики

G 09 В 7/07

3Ъвударстваилый комитет

СССР по делам нэабретеккй и открытей

Опубликовано 30.08.82. Бюллетень № 32 (53) УДК 681 ° 3 ° .071(088.8) Дата опубликования описания 02 . 09 .82

Л.В. Друзь и Ю.П. Рукоданов

i

1 (72) Авторы изобретения (71) Заявитель (54) ОБУЧАЮЦЕЕ УСТРОЙСТВО

Изобретение относится к области автоматики и может быть использовано при организации программированного обучения в различных учебных заведениях.

Известно устройство для автоматизированного контроля знаний учащихся, содержащее пульты учащихся, коммутаторы, блоки памяти, распределитель, блок эталонных ответов, блок 1о анализа, формирователь кода ответов, блоки считывания верных и ложных ответов, делитель частоты, генератор импульсов, коммутатор программ, коммутатор опроса и вычислительную маши" ну (13.

Недостаток известного устройства заключается в сложности его конструкции, а также в необходимости перестройки программы опроса в случае из- ?o менения числа пультов учащихся в про- . цессе обучения. Наиболее близким техническим решением к предлагаемому является обучас

2 ющее уст рои ство, которое содержит пульты учащихся, коммутатор, блоки анализа, блок памяти, пульт преподавателя, блок вывода, блок анализа методик, блок анализа тестов и блок формирования билетов (2g.

Недостатком известного устройства является низкое быстродействие, обусловленное последовательным опросом всех имеющихся в наличии пультов учащихся .без учета числа задействованных пультов, их исправности или неисправности, готовности к ответу учащихся.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные пульты учащихся, коммутатор и блок сравнения, подключенный к блоку памяти и пульт препода" вателя, соединенный с блоком оценки, введены первый и второй регистры, дополнительный коммутатор, блок за95517 держки, элемен ИЛИ, генератор импульсов и первый и второй блоки элементов И, причем первые входы первого регистра подключены к пультам учащихся, а выходы через последовательно соединенные элемент ИЛИ и генератор импульсов - к вторым входам первого блока элементов И, выходы которого соединены с вторыми входами первого регистра, подключенного через дополнительный коммутатор к входам блока задержки, выходы которого соединены с блоком памяти, с коммутатором, с первыми входами первого блока элемен ros И и с первыми входами второго блд- g ка элементов И, вторые входы которого подключены к выходу блока сравнения, а выходы соединены через второй регистр к.блоку оценки.

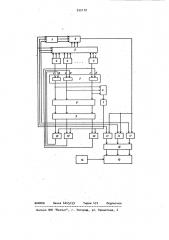

На чертеже приведена схема предлагаемого устройства. Обучащее устройство содержит блок 1 памяти, блок 2 сравнения, коммутатор 3, пульты 4 учащихся, первый регистр 5, элемент ИЛИ 6, генератор 7 импульсов, до-z5 полнительный коммутатор 8, блок 9 задержки, первый блок 10 элементов И, второй блок 11 элементов И, второй регистр 12, блок 13 оценки, пульт 14 преподавателя, Коммутатор 8 представляет с(Ьбой логическое устройство и обеспечивает приоритетный опрос входных сигналов таким образом, что, например, сигнал первым поступающий на данный вход, блокирует на время своего действия все сигналы, поступившие позже его, но действующие затем одновременно с ним на всех предыдущих и последуЮщих по отношению к данному входах. Для о одновременно поступивших сигналов приоритет на выход всегда получает сначала сигнал, действующий на предыдущем входе по отношению к си гналам на последующих входах. По окончании действия сигнала с большим приорите"

45 том разрешение на выход получает сигнал со следующего по приоритету входа блока приоритета, Таким образом, коммутатор 8 независимо от числа входных сигналов формирует выходной сиг" нал только на одном из своих выходов, соответствующем входу большего приоритетаа.

Устройство работает следующим образом.

С пульта 14 преподавателя выдается задание и отс и1ывается время решения задач у ащим :.в путем и дачи вре лен0 4 ных сигналов в блок 13 оценки. По мере решения поставленных задач от каждого пульта 4 учащихся поступают коды ответов на соответствующие входы ком" мутатора 3 и сигналы готовности - на единичные входы соответствующих разрядов регистра . Эти разряды устанавливаются в единичные состояния, Сигналы с выходов сработанных разрядов регистра 5 через элемент ИЛИ 6 включа-. ют генератор импульсов 7, а также подаются на входы коммутатора 8. Коммутатор 8 формирует сигнал только на одном из своих выходов, соответствующем входу с большим приоритетом. Этот сигнал через блок 9 задержки подается на первые входы первого и второго бло. ков элементов И, на управляющий вход коммутатора 3 и вход блока 1 памяти °

Блок 1 памяти хранит коды ответов на поставленные перед учащимися вопросы. При подаче сигнала на соответствующий вход блока 1 памяти на его выходах формируется эталонный код ответа, соответствующий данному опрашиваемому по приоритету пульту 4, кото" рый поступает на первые входы блока 2 сравнения, Одновременно при подаче сигнала на соответствующий управля" ющий вход коммутатора 3 кодовые Bblxo» ды данного опрашиваемого пульта 4 подключаются к вторым входам блока 2 сравнения, в котором сравниваются эталонный код и код ответа учащегося.

При совпадении этих кодов блок 2 сравнения формирует сигнал, который открывает соответствующий элемент И второго блока 11 элементов И и устанавливает в единичное состояние соответствующий разряд регистра 12, в котором фиксируются правильные ответы учащихся. Сигналы с выходов регистра 12 подаются в блок 13 оценки.

По окончании операции сравнения и записи результатов сравнения в блок 13 оценки формируется импульс на выходе генератора 7 импульсов. Период импульсов генератора 7 превышает вре> мя выполнения указанных операций. Импульс генератора 7 подается на вторые входы блока 10 элементов И, но открывает только соответствующий элемент И, на первый вход которого подан сигнал с выхода коммутатора 8.

Сигнал с выхода открытого элемента И блока 10 сбрасывает в нулевое состояние соответствующий разряд регистра 5. При этом приоритет на выход в коммутаторе 8 получает сигнал с выформула изобретения

Обучающее устройство, содержащее последовательно соединенные пульты учащихся, коммутатор и блок сравне30

5 9551 хода следующего сработанного разряда регистра 5, т.е. со следующего . готового к ответу пульта учащегося, который с задержкой, определяемой блоком 9 задержки и учитывающей время переходных процессов .в устройстве, управляет блоком 1,памяти, коммун татором 3, блоками 10 и 11 элементов И, и описанный выше процесс повторяется. По окончании опроса всех 10 сработанных разрядов регистра 5, т.е. всех учащихся, выполнивших задание, регистр 5 обнуляется, генератор 7 импульсов отключается, а в регистре 12 в единичные состояния уста- 15 навливаются разряды, соответствующие правильным ответам учащихся. В блоке 13 оценки с учетом времени и правильности решения по соответствующим шкалам формируются оценки учащихся. 20

Таким образом, в обучаюцем устройстве производится приоритетный опрос .только пультов учащихся, готовых к ответу, исключая незадействованные или неисправные пульты, что сокращает 25 время опроса и повышает быстродействие устройства.

6 ния, подключенный к блоку памяти, и пульт преподавателя, соединенный с блоком оценки, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, оно содержит первый и второй регистры, дополнительный коммутатор, блок задержки, элемент ИЛИ, генератор импульсов и первый и второй блоки элементов И, причем первые входы первого регистра подключены к пультам учащихся,а выходы через последовательно соединенные элемент ИЛИ и генератор импульсов - к вторым входам первого блока элементов И, выходы которого соединены с вторыми входами первого регистра, подключенного через дополнительный коммутатор к входам блока задержки, выходы которого соединены с блоком памяти, с коммутатором, с первыми входами первого блока элементов И и с первыми входами второго блока элементов 11, вторые входы которого подключены к выходу блока сравнения, а выходы подсоединены через второй регистр к блоку оценки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 654951, кл. G 09 В 7/02, 1979.

2. Авторское свидетельство СССР

11 699538, кл. G 09 В 7/07, 1979

{прототип).