Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстических

Республик

ОП ИСАН И E

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 150880 (21) 2975719/18-24 с присоединением заявки Мо—

Р 1М К„з

G 11 С 11/00

Государственный комитет

СССР но делам изобретений н открытий (23) Приоритет—

Опубликовано 300882, Бюллетень М 32

1 (Й УДК 681. 327 (088. 8) Дата опубликования описания 300882 (72) Автор. изобретения

В.И. Ткачев (71) заявитель (54) ЗЛПОИИНЛ10ЩЕЕ уСТРОйСТВО

Ф

Изобретение относится к запоминающим устройствам.

Одно из известных устройств представляет многоканальное устройство памяти и регистрации с временным разделением каналов и содержит накопитель информации .на сердечниках с прямоугольной петлей гистерезиса 1Я.

Недостатками этого устройства являются большие аппаратурные затраты.

Из известных устройств наиболее близким техническим решением к предлагаемому является запоминающее устройство, содержащее накопитель, схему формирования разрядных сигналов, содержащую распределитель, вентили и формирователи записи и считывания по количеству разрядов, схему формирования адресных сигналов, ключ перейоса и триггер управления, причем накопитель содержит две выходные ши-. ны, а разрядные цепи его включены встречно, т.е, один и тот же адресный ток является для четных разрядов током считывания, а для нечетных— записи (2J .

Применение двух выходных шин делает накопитель нестандартным и, следовательно, значительно усложняет устройство, что, в свою очередь, снижает.его надежность.

Цель изобретения — повышение надежности и упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее формирователи записи и считывания,-накопитель, адресные входы которого подключены к адресному блоку, а выход соединен с входом, усилителя считывания, и распределитель импульсов, введены дешифратор, ключи и элементы задержки, причем входы распределителя импульсов подключены соответственно к выходам формирователя считывания и первого элемента задержки, а выходы — к разрядным входам накопителя и информационным входам дешифратора, управ-. ляющий вход которого соединен с выходом формирователя записи, вход которого подключен к выходу первого . элемента задержки, входы первого ключа соединены с выходом усилите25 ля считывания, а также с выходом второго элемента задержки и входом формирователя считывания, а выходы — с входом первого элемента задержки и первач входом второго клюЗО ча, второй вход которого подключен

955196

10

20 его надежности.

60 б5

86 (прототип) . к одному из выходов дешифратора, один кз выходов — к вход BTopot о элемента задержки,, другой выход второго ключа является выходом устройства, а выходы дешифратора подключены к разрядным входам Накопителя.

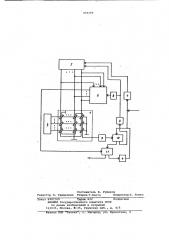

На чертеже изображена функциойальная схема запоминающего устройства. Устройство содержит накопитель 1, адресный блок 2, первый 3 и второЯ

4 элементы задержки, распределитель 5 импульсов, дешифратор 6, формирователь 7 считывания, формирователь 8 записи„ усилитель 9 считывания, первий 10 и второй 11 ключи.

Рассмотрим работу предложенного устройства в режиме счета.

При появлснии входного импульса он поступает на вход формирователя

7 считывания, выходной импульс которого через распределитель 5, установленный в ноль в предыцущий такт, попадает на вход первого разряда накопителя 1 и готовит первый выход дешкфратора 6. В этот же такт блок

2 Формирует адресный импульс считывания по необходимому каналу (адресу

Если там была записана единица, воз-. никает импульс на выходе накопителя

1, который усиливается усилителем 9 и подается на один из входов ключа

10. На его другом входе в этот такт присутствует входной сигнал, значит» с выхода ключа 10 сигнал поступит на вход ключа 11. Так как сигнала. на последнем выходе распределителя

5 нет, импульс с ключа 11 поступает на элемент 4 задержки, на выходе которого в следующем такте сформирует.ся сигнал. В этом такте импульс поступает на вход формирователя 7, и так как в предыдущем такте считывалоя сигнал из первого разряда накопи" теля 1, сейчас будет считываться сигнал из второго разряда.

Следует отметить, что в этот такт блок 2 формирует адресный импульс, записи, однако, учитывая встречное включение разрядов накопителя 1, он будет являться током считывания для второго разряда. Таким образом, пока в разрядах данного адреса накопите.ля 1 содержатся единицы, они будут считываться. При этом в разряды за-. писывается ноль. Но как только при считывании из очередного разряда на выходе накопителя 1 будет нулевой сигнал, появится импульс на другом выходе ключа 10„ и в следующем такте на выходе. элемента 3 задержКи . сформируется сигнал, который посту-. пит на вход установки в ноль распределителя 5 и на вход формирователя

8 записи, который опросит дешифратор б. Перед этим дешифратор 6 был установлен распределителем 5, поэтому он выдаст импульс в тот же разряд накопителя 1. И так как адресные импульсы записи и считывания чередуются, в этом разряде запишется единица. Устройство вернулось в исходное состояние и ждет поступления следующего входного импульса.

При этом записанное в данном адресе число ...01...1 преобразовалось и число ...10...0.

Другим вариантом окончания работы устройства является появление выходного сигнала при считывании из последнего разряда накопителя 1.

Это означает, что в накопителе 1 было записано число ...11...11 ° Тогда

K/HAH 10 H 11 управляются TBKHM образом, что импульс проходит через ключи 10 и 11 и появляется на выходе как импульс переполнения, а данный адрес накопителя обнуляется.

Технико-зкономическое преимущество предлагаемого устройства по сравнению с прототипом заключается в упрощении устройства и повышении

Формула изобретения

Запоминающее устройство, содержащее формирователи записи и считывания, накопитель, адресные входы которого подключены к адресному блоку, а выход соединен с входом усилителя считывания, и распределитель импульсов, о т л и ч а ю— щ е е с я тем„ что, с целью повышения надежности устройства, оно содержит дешифратор, ключи и элементы зацержки, причем входы распределителя импульсов подключены соответственно к выходам формирователя считывания.и первого элемента задержки,а выходы - к разрядным входам накопителя и информационным входам дешифратрра, управляющий вход которого соединен с выходом формирователя записи,. вход которого подключен к выходу первого элемента задержки, входы первого ключа соединены с выходом усилителя считывания, а также с выходом второго элемента задержки и входом формирователя считывания, а выходы — c входом первого элемента задержки и первым входом второго ключа, второй вход которого подключен к одному из выходов дешифратора, один из выходов - к входу второго элемента задержки, другой выход второго ключа является выходом устройства, а выходы дешифратора подключе". ны к,разрядным входам накопителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 224589, кл. g- 11 С 25/02, 1967.

2. Балашов Е.П., Кноль A.È. Мно-. гофункциональные запоминающие устройства. Л., "Энергия", 19 12, с.85955196

Составитель В. Рудаков

Редактор Н. Гркшанова Техред Т.Фанта Корректор Е. Роыко

Заказ б 7 60 Тиф)аж 2 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 3035, Иосква, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, r. Укгород, ул. Проектная,