Устройство для управления регенерацией памяти

Иллюстрации

Показать всеРеферат

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 12. 01. 81 (21) 3234160/18-24 (5 f ) М Кп З с присоединением заявки №

11 С 21/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет(5Ç) УДК 681. 327. . б (088. 8) Опубликовано 30.08.82. Бюллетень ¹ 32

Дата опубликования описания 30.08.82 (72) Авторы изобретения

В. A. Исаенко и H. N. Тафель (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ

ПАИЯТИ

Изобретение относится к вычислительной технике и предназначено для использования в оператив ных запоминающих устройствах (ОЗУ) .

Известно устройство для управления регенерацией информации в динамических ОЗУ, в котором для уменьшения количества тактов регенерации используется оптимизация темпа регенерации в зависимости от температуры элементов ОЗУ f17.

Однако в этом устройстве регенерации подвергаются все строки, в том числе и те, которые не нуждаются в регенерации, поскольку к ним на предЫдущем интервале допустимого времени хранения информации обращался пользователь памяти, следовательно, здесь очевидны избыточные такты регенерации.

Наиболее близким по технической сущности к предлагаемому является устройство для управления регенерацией информации в динамической памяти, содержащее адресный блок, дешифратор, вспомогательные элементы памяти, элемент ИЛИ, элементы НЕ, элементы И, шифратор и блок управления.

В известном устройстве на каждом интервале допустимого времени хранения информации ОЗУ факты обращения пользователя к строкам ОЗУ фиксируются вспомогательными элементами памяти (по элементу на каждую строку), а в конце интервала хранения регенерируются только те строки, которые нуждаются в регенерации (строки, к которым на предыдущем интервале хранения не обращался пользователь)., Благодаря этому устраняются избыточные такты регенерации при произвольном переборе адресов ОЗУ, но максимально эффективно данное устройство при последоватегьном переборе адресов, когда такты регенерации практически не возникают (23.

Однако при реализации широкого класса матричных задач эффективность известного устройства может резко падать, поскольку при обращении к векторам-столбцам перебираются элементы только одной из строк, что обуславливает низкое быстродействие и большое максимальное время ожидания ответа ОЗУ (практически равное времени регенерации всех строк).

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для управления ре955206 генерацией памяти, содержащее элементы "".àìÿòè, адресные входы которых подключены к выходам дешифратора, а выходы к входам элемента ИЛИ, выход которого подключен к входу блока управления, управляющие входы ,элементов памяти подключены к соответствующему выходу блока управленит, элементы НЕ, входы которых подключены к выходам соответствующих элементов памяти, а выходы — к входам соот- 10 ветствующих элементов И, шифратор, один вход которого подключен к выхо-. ду соответствующего элемента памяти, а другие входы подключены к выходам элементов И, выход шифратора подключен к первому входу адресного блока, выход которого подключен к дешифратору, второй вход адресного блока является соответствующим адресным входом устройства, дополнительно введен сумматор, один вход которого подключен к второму входу адресного блока, второй вход сумматора является соответствующим адреcHblM входом устройства, а выход сумматора подключен к третьему адресному входу адресного блока.

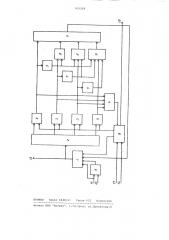

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит адресный блок

1, дешифратор 2, элементы 3 памяти, элемент ИЛИ 4, элементы HE 5, элементы И 6, шифратор 7, блок 8 управления, сумматор 9, входную шину 10 младших разрядов и входную шину 11 35 старших разрядов адреса пользователя, выходную адресную шину 12 динамического запоминающего устройства, входную шину 13 сброса, входную шину 14 запроса и выходную шину 15 сигнала 4О занятости для пользователя.

При поступлении от пользователя по шине 13 сигнала сброса блок 8 управления устанавливает элементы 3 памяти в единичное состояние и выдает 45 на управляющий вход адресного блока

1 сигнал, разрешающий прохождение на входы дешифратора 2 и на адресную шину динамического запоминающего устройства 12 адреса от пользователя, поступающего по шинам 10 и 11.

По каждому сигналу запроса, поступающему от пользователя по шине 14, происходит обращение к ОЗУ по выставленному пользователем адресу одновре1 менно сигнал одного из выходов дешиф- 5 ратора 2 записывает "0" в элемент 3 памяти, соответствующей выбранной строке ОЗУ (Wpec строки. определяется младшими разрядами адреса обращениями.

По окончании временного интервала 60 не превышающего допустимое время хранения, блок 8 управления анализирует состояние выхода элемента ИЛИ 4.

Нуль на выходе элемента ИЛИ 4 означает, что все вспомогательные элементы

3 памяти обнулены, т.е. к всем строкам .

ОЗУ на интервале i обращался подьзователь, следоватедьно, ни одна из строк в регенерации не нуждается и блок 8 управления цикла регенерации не организует. Единица на выходе элемента ИЛИ 4 означает, что имеются строки, нуждающиеся в регенерации, поскольку пользователь к ним не обра цался, в этом случае блок 8 управления организует цикл регенерации.

H цикле регенерации по шине 15 пользователю поступает сигнал занятости

ОЗУ, а на вход управления адресного блока 1 от блока 8 управления поступает сигнал, разрешающий прохождение на входы дешифратора 2 и на адресную шину 12 адресов регенерации с выходов шифратора 7. Приоритетная цепочка из элементов НЕ 5 и И б обеспечивает прохождение на входы шифратора 7 только одного единичного сигнала с текущим высшим приоритетом. Этот единичный сигнал преобразуется шифратором

7 в соответствующий адрес, по которому в очередном такте регенерации и производится обращение к ОЗУ, при этом обнуляется соответствующий вспомогательный элемент 3 памяти, и в последующем такте регенерируется очередная по приоритету строка ОЗУ, нуждающаяся в реГенерации. цикл регенерации завершается при появлении нуля на выходе элемента ИЛИ 4, при этом блок 8 управления формирует внутренний сигнал сброса, который устанавливает элементы 3 памяти в единичное состояние, снимает на шине 15 сигнал занятости ОЗУ и выдает на управляющий вход адресного блока сигнал, разрешающий пропускание на входы дешифратора 2 и адресную шину 12 адреса от пользователя. На следующем рабочем интервале Т устройство функционнрует аналогично.

Отличительной особенностью предлагаемого устройства является модификация младших разрядов адреса (физически соответствующих адресам строк кристаллов ОЗУ}, поступающего от пользователя по шине 10. При этом старшие разряды адреса, поступающие по шине

11, не изменяются. Для ОЗУ емкостью

2 бит (2 строк на 2 столбцов) модифицированная N-pasp a младшая часть адреса образуется на комбинационном N-разрядном сумматоре 9 путем суммирования по модулю 2 двух V-разрядных чисел — младших и старших разрядов адреса пользователя, поступающих соответственно по шинам 10 и 11, причем для взятия суммы по модулю 2 достаточно прогнозировать перенос из старшего разряда сумматора 9, à N-раз— рядный результат считать от его разрядных выходов. Можно отметить, что в предлагаемом устройстве старшие раз955 206 ряды адреса, поступающие по шине 11, выполняют две функции: во-первых, они служат старшей частью исполнительного адреса ОЗУ, во-вторых, используются в качестве модификатора младшей части адреса.

Модифицированный исполнительный адрес, полученный предлагаемым методом, обладает следующим свойством: последовательный перебор строк в исполнительном адресе образуется как при переборе строк, так и при перебо ре столбцов в исходном адресе пользователя. Это свойство делает предлагаемое устройство весьма эффективным при реализации матричных задач и процессов, поскольку при переборе векторов-столбцов и векторов-строк такты регенерации практически отсутствуют, что значительно повышает быстродействие устройства и резко снижает максимальное время ожидания отве- та ОЗУ пользователю.

Следует также отметить, что подобная модификация исполнительных адресов для целого ряда оперативных запоминающих устройств специализированных процессоров позволяет вообще отказаться от системы регенерации

ОЗУ, что резко упрощает их конструкцию, повышает быстродействие и надежность

Формула изобретения

Устройство для управления регенерацией памяти, содержащее элементы памяти, адресные входы которых подключены к выходам дешифратора, а . выходы — к входам элемента ИЛИ, выход которого подключен к входу блока управления, управляющие входы элементов памяти подключены к соответствующему выходу блока управления, элементы НЕ, входы которых подключены к выходам соответствующих элементов памяти, а выходы — к входам соответ 0 ствующих элементов И, шифратор, один вход которого подключен к выходу соответствующего элемента памяти, а другие. входы подключены к выходам элементов И, выход шифратора подклю15 чен к первому входу адресного блока, выход которого подключен к дешифратору, второй вход адресного блока является соответствующим адресным входом устройства, о т л и ч а юру щ е е с -я тем, что, с целью повышения быстродействия, устройство содержит сумматор, один вход которого подключен к второму входу адресного блока, второй вход сумматора является

25 соответствующим адресным входом устройства, а выход сумматора подключен к третьему входу адресного блока.

Источники информации, принятые во внимание при экспертизе

3() 1 Авторское свидетельство СССР

9 522523, кл. G 11/34, 1974.

2. Авторское свидетельство СССР

9 514346, кл. G 11 С 21/00, 1974 (прототип).