Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ол955212 (61) Дополнительное к авт. свид-ву Р 645208

{S1J М. Кл. (22) Заявлено 30 ° 01-81 (21) 3242573/18-24

Gг 11 С 29/00 с присоединением заявки М (23) Приоритет—

Государственный комитет

СССР по делам изобретений и открытий

153} УДК 681. 327. .6(088.8) Опубликовано 30.0882. Бюллетень М 32

Дата опубликования описания 30.08 82 (72) Авторы изобретения

А. С. Горбенко и В. И. Николаев (71) Заявитель (5 4) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам.

По основному авт. св. 9 645208 известно запоминающее устройство с са5 моконтролем; содержащее накопитель, подключенный к регистру адреса и регистру слова, соединенного с блоком контроля и блоком кодирования, блок управления, регистр отказов и элементы И, входы которых подключены к выходам регистра слова и блока управления, а выходы — к выходам устройства, входы регистра отказов соединены с выходами блока управления, а выходы с входами регистра слова (1 J. 15

Недостатком этого устройства является низкое быстродействие при исгравлении ошибок в считанных словах. Действительно, при обнаружении ошибки вы- 2п полняется последовательная инверсия разрядов считанного слова с проверкой результата каждой инверсии. При этом закон последовательности инвертирования не определен и, в случае обнаружения любой ошибки, инвертирование начинается одинаково, например с младших разрядов считанного числа, т.е. без учета коррекции ошибок. Вполне очевидно, что время исправления ошибок при этом велико.

Цель изобретения — повышение быстродействия устройства путем сохранения некоторой информации о предыдущих ошибках.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем введены дополнительный регистр и дополнительные элементы И, одни из входов которых подключены к выходам регистра отказов, выходы соединены с входами дополнительного регистра, а выходы дополнительйого регистра и другие входы дополнительных элементов И являются соответственно управляющими выходами и входами.

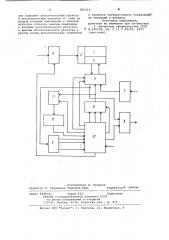

На чертеже представлена схема предлагаемого устройства.

Устройство содержит накопитель 1, в состав которого входят адресный 2 и разрядный 3 блоки. Устройство содержит также регистр 4 адреса, регистр

5 слова, регистр 6 отказов, блок 7 кодирования, элементы И 8, блок 9 конт роля, блок 10 управления, дополнительные элементы И 11 и дополнительный регистр 12.

Устройство работает следующим образом.

В режиме записи на регистр 4 поступает код адреса ячейки, в которую не955212

В случае, если имеет место отказ в младшем разряде, то выход i-ой кратности отказа блока 9 изменит свое значение, т.е. станет равным логическому нулю. Следовательно, отказ в считанном слове после первого суммирования по модулю два будет (i-1)-ой кратности.

Если кратность отказа уменьшилась на единицу (соответственно число логических единиц на выходе блока 9 стало на единицу меньше), то по сигналу блока 10 информация в регистре

60 обходимо записать слово, поступающее на вход блока 7, B блоке 7 формируются контрольные разряды для обнаружения отказов j + 1 кратности,.где некоторое целое число. Информационные и контрольные разряды слова с выходов 5 блока 7 поступают в регистр 5, На ! блок 10 подается код операции запистт .

По сигналу с выхода блока 10 код слова из регистра 5 поступает на входы разрядного блока 3 накопителя 1 и записывается по адресу, поступающему из регистра 4 на адресный. блок 2.

В режиме считывания на регистр 4 подается адрес ячейки, информацию из которой необходимо считать. По 15 сигналу от блока 10 код адреса поступает на входы адресного блока 2 и с выходов разрядного блока 3 накопителя 1 считанный код слова поступает на регистр 5. Считанный код подается 20 на вход блока 9, который обнаруживает отказы кратности 1, 2, 3, + 1.

При этом для каждой кратности отказа блок 9 имеет отдельный выход.

В случае, когда нет отказов, на всех выходах блока 9 имеются сигналы, равные логическим нулям, и блок 10 формирует сигнал, по которому элементы И 8 открываются, и код считанного слова поступает на выход устрой- 0 ства.

B случае, когда в коде слова есть отказ i îé кратности, где 1 < i < ! то на выходах блока 9, соответствующих однократному, двукратному и т.д.

1-кратному отказам, появляются cHr-- 35 налы, соответствующие логической единице. При наличии единичного сигнала, хотя бы на одном из выходов блока 9, блок 10 формирует сигнал записи единицы, например, в младшем разряде регистра б и запрещает выдачу считанного слова на выход устройства. По сигналу блока 10 единица записывается.в младшйй разряд регистра б, после чего следует операция суммирования45. по модулю два кодов в регистре 5 и регистре б. Для выполнения этой операции с выхода блока 10 поступает сигнал на регистр б, и содержимое этого регистра, имеющее единицу в младшем разряде, поступает на счетные входы регистра 5. б сдвигается на один разряд и снова выполняется операция суммирования по модулю два. Кроме того, блок 10 формирует сигнал, по которому через элементы И 11 в младший разряд регистра 12 записывается единица, В случае, когда после суммирования кратность отказа увеличивается, то и число лоTè÷åñêèõ единиц на выходе блока 9 увеличивается на единицу. Для восстановления исходного состояния значения этого разряда необходимо снова просуммировать l1o модулю два содержимое регистров 5 и 6, после чего выполнять сдвиг в регистре б. При этом в регистр

12 информация не заносится. Операция суммирования по модулю два и сдвиг выПолняются до тех пор, пока из блока 9 не поступят на блок 10 все сигналы, равные логическому нулю. После этого регистр б обнуляется. В регистре 12 сохраняются единицы в тех разрядах, при изменении значений которых кратность отказов уменьшалась.

При появлении отказов в другом считываемом слове единица записывается по сигналу 10 первоначально не в младший разряд регистра 6, а в разряд, соответствующий разряду регистра 12, хранящему единицу. Если таких разрядов в регистре 12 оказывается несколько, то блок 10 обеспечивает последовательное занесение единиц вначале в разряды регистра б, соответствующие именно этим разрядам регистра 12, путем формирования сигналов сдвига на необходимое количество разрядов. Предполагается, что регистр б имеет цепь кольцевого сдвига. В том случае, когда суммирование по модулю два указанных разрядов регистра б и содержимого регистра 5 не обеспечивает исправление всех ошибок, блок 10 будет формировать сигналы, необходимые для последовательного занесения единиц в другие разряды регистра б с пропуском уже ранее суммировавшихся разрядов до исправления всех ошибок в слове.

Поскольку ошибки в одноименных разрядах различных слов составляют значительный процент от общего числа ошибок, особенно при наличии отказов в разрядной системе запоминающих устройств, предлагаемое устройство позволяет путем учета предыдущих отказов уменьшить время исправления ошибок в указанных случаях и тем самым, повысить быстродействие устройства. формула изобретения

Запоминающее устройство с самоконтролем по авт, св, 9 645208, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия устройства, 955212

Составитель В. Рудаков

Редактор Н. Гришанова Техред М.Надь

КорректорМ Лемчик

Заказ 6448/61 Тираж 622 Подп и сн ое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 оно содержит дополнительный регистр и дополнительные элементы И, одни из входов которых подключены к выходам регистра отказов, выходы соединены с входами дополнительного регистра, а выходы дополнительного регистра и другие входы дополнительных элементов

И являются соответственно управляющь:— ми выходами и входами.

Источники информации, принятые во. внимание при экспертизе

1. Авторское свидетельство СССР

Р 645208, кл. С 11 С 29/00, 1977 (прототип).