Устройство для коррекции информации в блоках постоянной памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 955213

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 28.01. 81 (21) 3242716/18-24

У1 М. К

G 11 С 29/00 с присоединением заявки Мо

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет — (S3) УДК 681. 327 (088. 8) Опубликовано 300882. Бюллетень Мо 32

Дата опубликования описания 30.08.82 (72) Авторы изобретения

В< С оськин

А. Н. Ладыгин, И. И. Лузан, М. А. Оз еров у A (71) Заявитель (54) УСТРОЙСТВО ДЗИ КОРРЕКЦИИ ИНФОРМАЦИИ

В БЛОКАХ ПОСТОЯННОЙ ПАМЯТИ

Изобретение относится к запоминающим устройствам и может быть использовано для коррекции информации в блоках постоянной памяти, контролируемых по модулю три.

Известно устройство для коррекции информации в блоках постоянной памяти., содержащее постоянное запоминающее устройство (ПЗУ), несколько блоков полупостоянного запоминающего устройства (ППЗУ) малой емкости, счетчик и дешифратор (1).

Недостатком этого устройства является его сложность.

Из известных устройств наиболее близким техническим решением к предлагаемому является устройство для коррекции информации в блоках постоянной памяти, содержащее блоки постоянного запоминающего устройства (ПЗУ), подключенного к буферу блока полупостоянного ЗУ малой емкости (ППЗУ), подключенного к дешифратору. ПЗУ и

ППЗУ по входам включены параллельно, блоки ППЗУ распределены по разрядам адреса ПЗУ, дешифратор соединен с вспомогательной памятью, с инвертором и буфером ПЗУ, вспомогательная память соединена с буфером, который управляется от инвертора (21.

Недостатком этого устройства является низкое быстродействие, так как коррекция одной ячейки памяти осуществляется в два этапа.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для коррекции информации в блоках постоянной памяти, сог держащее накопитель и элемент НЕ, выход которого подктвочен к одному из входов накопителя, другие входы которого являются одними из входов устройства, введены схема сравнения, элементы И, элемент ИЛИ и регистр старших разрядов адреса, входы которого являются другими входами устройства, а выходы подключены соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с выходами первой группы выходов накопителя, выходы первого . и второго элементов И соединены с входами схемы сравнения, выход котсрой подключен к первым входам третьего и четвертого элементов И, вторые входы которых соединены с выходами второй группы выходов накопителя, выходы третьего и четвертого элементов

И подключень. к входам элемента ИЛИ.

955213 выход которого соединен с входом элемента НЕ, выходы третьей группы выходов накопителя и выход элемента

ИЛИ являются соответственно ииформа". ционными и управляющим выходами устройства. 5

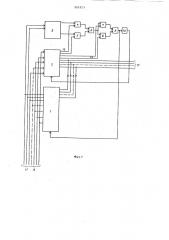

На фиг. 1 представлена функциональйая схема предлагаемого устройства,- на Фиг. 2 — временные диаграммы, поясняющие его работу. 10

Устройство содержит контролируемый блок 1 постоянной памяти (фиг. 1) накопитель 2, регистр 3 старших разрядов адреса, первый 4 и второй 5 элементы И, схему б сравнения, третий 7 и четвертый 8 элементы И, элемент

ИЛИ 9 и элемент HE 10. На фиг. 1 обозначены старшие разряды 11 адреса, младшие разряды 12 адреса, первая 13, вторая 14 и третья 15 группы выходов накопителя, Устройство работает следующим образом.

При возникновении неисправности в одной из ячеек блока постоянной памяти или необходимости коррекции информации в выбранной ячейке блока 1 (фиг. 1) постоянной памяти возникает необходимость подмены ячейки блока 1 ячейками накопителя 2 (фиг. 1), в которой заносится нужная информация, 30 а также младшие разряды 12 адреса блока 1. Для коррекции нескольких ячеек блока 1 предназначена одна ячейка накопителя 2, в соответствии с этим в,накопитель 2 поступают толь- 35 ко младшие разряды 12.адреса, а в блок 1 все разряды адреса. Уточнение ячейки накопителя 2 для коррекции выбранной ячейки блока 1 осуществляется следующим образом. Накопитель 2 40 имеет большую разрядность информации, чем блок 1, и большее быстродействие.

Выборка информации из блока 1 и накопителя 2 (Фиг. 1) начинается одновременно с поступлением в них кода адре- 4 са и заканчивается к моменту С (фиг. 2) для накопителя 2 (фиг. 1) и к моменту 1 (фиг. 2), t и (фиг. 2) для блока 1 (фиг. 1) постоянной памяти.

Распределение информации по разрядам блока 1 постоянной памяти и накопителя 2 следующее.

Разряды накопителя 2: О, 1, 2, n, n + 1, и + 2, п + 4; разряды блока 1 постоянной памяти: О, 1, 2, ..., n n + 1, n + 2, где разряды

О, ..., п — информационные; n + 1, и+2-;п+3,n+4 разрЯды, в которых указан уточненный адрес ячейки накопителя 2. 60

При уточнении принадлежности ячейки накопителя,2 ячейке блока 1 постоянной памяти происходит сравнение состояния разрядов регистра 3 (фиг.1) с разрядами (n + 3) и (n + 4) инфор- 65 мации накопителя 2, в которых указан уточненный адрес ячейки. Сигналы с выходов регистра 3 поступают на первые входы элементов И 4 и 5 (фиг. 1).

На вторые входи элементов И 4 и 5 поступают сигналы из накопителя 2, соответствующие (n + 3) и (и + 4) разрядам информации. Сигналы с выходов элементов И 4 и 5 поступают на вход схемы б сравнения, где они сравниваются. При совпадении этих сигналов вырабатывается сигнал, который подается на первые входы элементов И 7 и 8. Это соответствует моменту времени 1 на временной диаграмме (фиг.2).

На вторые входы элементов И 7 и 8 поступают сигналы с выходов 14 накопителя 2, соответствующие контроль ным разрядам (n + 1)., (n + 2). Информация, содержащаяся в блоке 1 постоянной памяти и в накопителе 2, контролируется по модулю три, поэтому контрольные разряды не содержат нулевой информации. При наличии контрольных разрядов, а следователь-. но, и корректирующей информации в накопителе 2 срабатывает .хотя бы один из элементов И 7 и 8, Сигналы с выходов элементов И 7 и 8 объединяются на элементе ИЛИ 9 и поступают на вход блока 1 постоянной памяти и на вход элемента HE 10 (фиг. 1).

Это соответствует моменту времени

t (фиг. 2), 1

Сигнал с выхода элемента НЕ 10 (фиг. 1) управляет выдачей кода информации из накопителя 2. Сигнал с выхода элемента ИЛИ 9 временно блокирует выдачу кода информации из блока 1 постоянной памяти. Это соответствует моменту t3 на временной диаграмме (фиг. 2), Сигнал с выхода элемента НЕ 10 (Фиг. 1) разрешает выдачу кода информации из накопителя

2, тем самым осуществляется коррекция информации блока 1 постоянной памяти.

Если уточненный адрес ячейки накопителя 2, указанный в (n + 3) и (n + 4) разрядах информации, не совпадает с содержимым регистра 3, то элементы И 4 и 5 и схема б сравнения не срабатывают, на первые входы элементов И 7 и 8 сйгнал не подается и с выхода элемента ИЛИ 9 не поступает сигнал временной блокировки блока 1 ° Это соответствует моменту на временной диаграмме .(Фиг. 2).

В этом случае информация выдается из блока 1 (фиг. 1), а информация, выбранная из накопителя 2, временно блокируется сигналом с выхода элемента НЕ 10, Это соответствует моменту 1б на временной диаграмме (фиг. 2).

Если накопитель 2 (фиг. 1) не содержит информации, то ни один из зле955213 ментов И 4, 5, 7, 8, элемент ИЛИ 9 и схема 6 сравнения не сработают.

В этом случае информация будет выбираться из блока 1 постоянной памяти. Это соответствует моменту t8 на временной диаграмме (фиг. 2).

Таким образом, коррекция информации в блоке 1 постоянной памяти (фиг. 1) осуществляется параллельно с выборкой из него информации.

Технико-экономическое преимущество предлагаемого устройства заключается в,его более высоком быстродействии, по сравнению с прототипом,, достигаемым за счет исключения вто.ричного обращения к накопителю при 15 коррекции информации.

Формула изобретения

Устройство для коррекции информа- 2п ции в блоках постоянной памяти, содержащее накопитель и элемент ЙЕ, выход которого подключен к одному из входов накопителя, другие входы

KoTopoI О яВляются Одними из ВХОДОВ 25 устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит схему сравнения, элементы И, элемент

ИЛИ и регистр старших разрядов адреса, входы которого являются другими входами устройства, а выходы подключены соответственно к первым входам первого и второго элементов И, вторые входы которых, соединены с выходами первой группы выходов .накопителя, выходы первого и второго элементов И соединены с входами схемы сравнения, выход которой подключен к первым входам третьего и четвертого элементов И, вторые входы которых соединены с выходами второй группы выходов накопителя, выходы третьего и четвертого элементов И подключены к входам элемента ИЛИ, выход которого соединен с входом элемента НЕ, выходы третьей группы выходов накопителя и выход элемента ИЛИ являются соответственно информационными и управляющим выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент CUR 9 4028683, кл. 340-172, опублик. 1977.

2. Патент СИ 9 4028679, кл. 340-172. 5, опублик. 1977 (прототип) .

955213

7 5 б

Ф иь.2

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель Т. Зайцева

Редактор Н. Гришанова ТехредМ.Надь Корректор М. Коста

Заказ 6448/61 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5