Устройство для фазового управления тиристором

Иллюстрации

Показать всеРеферат

п11955416

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 18 ° 12 ° 80 (21) 3219729/24-07 с присоединением заявки ¹â€” (23) Приоритет— (51) М Кл з

Н 02 М 1/08

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 300882. Бюллетень ¹ 32 (53) УДК 621, 316 .. . 727 (088. 8) Дата опубликования описания З0 (72) Авторы изобретения

Владимирский политехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ФАЗОВОГО УПРАВЛЕНИЯ

THPHCTOPOM

Изобретение относится к преобразовательной технике и может быть использовано для управления тиристорами в схемах вентильных преобразователей. Известны устройства для управления тиристорами, содержащие последовательно соединенные интегратор, пороговый элемент, формирователь импульсов, клеммы для подключения источников управляющего сигнала и синхронизации, .подключенные ко входу интегратора через коммутатор (11

Недостатком указанных устройств управления тиристорами является недостаточная надежность,. обусловленная низкой помехоустойчивостью.

Наиболее близким техническим решением к изобретению по средствам и достигаемому результату является устройство для управления выпрямителем, содержащее интегратор, выполненный на операционном усилителе, зашунтированном конденсатором, с двумя подсоединенными одними выводами к его .входу резисторами, подсоединенный к вы25 ходу интегратора пороговый элемент, блок синхронизации, инвертор, подсоединенный выходом через первый ключ, управляющий вход которого подсоединен к выходу первого блока управления,,30 ко второму выводу первого резистора, вход инвертора соединен со входом второго Ключа, элемент НЕ, второй блок управления, формирователь импульсов, элемент И и клеммы для подключения источника управляющего напряжения и управляющего электрода тиристора (2).

Недостатком известного устройства является невысокая помехоустойчивость.

Iles изобретения — повышение помехоустойчивости устройства.

Поставленная цель достигается тем, что устройство снабжено дополнительным резистором, подсоединенным одним выводом ко входу интегратора и другим — к клемме для подключения источника управляющего напряжения, соединенной одновременно со входом второго ключа, выход которого соединен со вторым выводом второго резистора, и управляющий вход — к выходу второго блока управления, выход порогового элемента соединен с одним входом элемента И, второй вход которого подсоединен через элемент НЕ к выходу первого и входу второго блока управления, выход элемента И соединен со входом формирования импульсов, подсоединенного своим выходом к клемме

955416

65 для подключения управляющего электрода тиристора, а блок синхронизации подсоединен параллельно конденсатору.

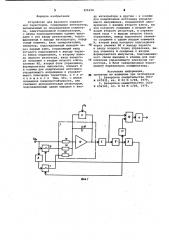

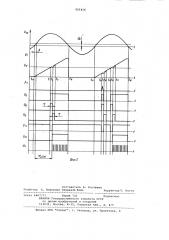

На фиг. 1 приведена принципиальная электрическая схема устройства для фазового управления тиристорами; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство для фазового управления тиристором (фиг. 1) содержит интегратор 1, пороговый элемент 2, блок 3 синхронизации, формирователь

4 импульсов, первый ключ 5, инвертор

6, второй ключ 7, первый и второй ждущие мультивибраторы 8 и 9, элемент И 10, элемент НЕ 11. Интегратор 1 выполнен на операционном усилителе 12, на входе которого включены резисторы 13-15, а в цепи обратной связи — конденсатор 16.

Устройство работает следующим образом.

В рабочий полупериод при действии управляющего сигнала на входе интегратора 1 его выходное напряжение увеличивается по линейному закону со скоростью, пропорциональной U@z.

Первый и второй ключи 5 и 7 разомкнуты. На первом входе элемента И 10 действует сигнал логического нуля с выхода порогового элемента 2, на второй — логическая единица с выхода элемента HE 11, на выходе которого действует нулевой потенциал с выхода первого ждушего мультивибратора 8. Следовательно, на выходе элемента И 10 действует сигнал логического нуля, блокирующий формирователь

4 импульсов. При достижении выходным напряжением интегратора 1 уровня переключения порогового элемента 2 (фиг. 2), последний переключается и запускает первый ждущий мультивибратор 8, который формирует импульс длительностью т . В .течение времени действия выходного импульса первого ждушего мультивибратора 7 второй ключ 7 замкнут, следовательно, на третьем входе интегратора действует выходной сигнал инвертора U6= -U (фиг. 2). Так как на двух идентичных входах интегратора действуют равные по модулю, но имеющие противоположную полярность сигналы, его выходное

Напряжение не уменьшается., На первом в оде элемента И 10 действует сигнал логической единицы с выхода порогового элемента 2 и логического нуля с выхода элемента HE 11, .на входе которого действует выходной сигнал первого ждущего мультивибратора 8.

Следовательно, выходной сигнал элемента И соответствует логическому нулю, формирователь выходных управляющих импульсов выключен. В момент окончания (t,<) действия выходного импульса первого ждущего мультивиб20

55 ратора 8 запускается второй ждущий мультивибратор 9, формируюший импульс длительностью с, который замы. кает первый ключ 5. Второй ключ 7 при этом размыкается. На первом и втором входах интегратора действуют сигналы Бв„, поэтому его выходное

1напряжение продолжает увеличиваться с удвоенной скоростью. На входах элемента И 10 действуют сигналы логической единицы с выхода порогового элемента 2 и элемента НЕ, на входе которого действует сигнал логического нуля с выхода первого ждущего мультивибратора 8. Сигнал логической единицы с выхода элемента И 10 запускает формирователь 4 управляюших импульсов.

При действии импульсной помехи на входе порогового элемента 2 в момент времени, при котором выходное напряжение интегратора П„ < Un, например t<(фиг. 2), происходит переключение порогового элемента и запуск первого ждущего мультивибратора 8. В течение времени 7 выходное напряжение 1 не изменяется, а выходной сигнал логического нуля на втором входе элемента И с выхода элемента НЕ 11, на входе которого действует логическая единица с выхода первого ждущего мультивибратора, блокирует формирователь пачки управляющих импульсов. Если длительность действия импульсной помехи не превышает 7 то за время действия выходного импульса первого ждущего мультивибратора пороговой элемент 2 возврашается в исходное состояние. Следовательно, после окончания импульса не происходит включения формирователя пачки управляюших импульсов, так как на первом входе элемента И 10 с выхода порогового элемента 2 действует сигнал логического нуля. В течение времени Г действия выходного импульса второго ждущего мультивибратора 9 увеличивается с удвоенной скоростью, так как íà его первом и втором входах действует сигнал U s . Благодаря этому компенсируется задержка в формировании управляюцего сигнала, вносимая действием первого ждущего мультивибратора. Следовательно, после окончания импульса второго ждущего мультивибратора (момент te, Фиг. 2) напряжение

На выходе интегратора совпадает с теоретическим значением, соответствующим случаю отсутствия помехи.

Таким образом, при действии импульсной помехи во время формирования управляющего сигнала не происходит ложного срабатывания устройства, кроме того, использование изобретения обеспечивает отсутствие искажений в законе формирования управляюшего сигнала.

955416

Формула изобретения

Устройство для фазового управления тиристором, содержащее интегратор, выполненный на операционном усилителе, зашунтированном конденсатором, 5 с двумя подсоединенными одними выводами к его входу резисторами, подсоединенный к выходу интегратора, пороф говый элемент, блок синхронизации, инвертор, подсоединенный выходом че- 0 рез первый ключ, управляющий вход которого подсоединен к выходу первого блока управления, к второму выводу первого резистора, вход инвертора соединен с входом второго ключа, 15 элемент НЕ, второй блок управления, формирователь импульсов, элемент И и клеммы для подключения источника управляющего напряжения и управляющего электрода тиристора, о т л ич а ю щ е е с я тем, что, с целью повьпаения помехоустойчивости, оно снабжено дополнительным резистором, подсоединенным одним выводом к входу интегратора и другим — к клемме для подключения источника управляющего напряжения, соединенной одновременно с входом второго ключа, выход которого соединен с вторым выводом второго резистора, и управля. ющий вход — к выходу второго блока управления, выход порогового элемента соединен с одним входом элемента

И, второй вход которого подсоединен через элемент НЕ к выходу первого и входу второго блока управления, выход элемента И соединен с входом формирователя импульсов, подсоединенного своим выходом к клемме для подключения управляющего электрода тиристора, а блок синхронизации подсоединен параллельно конденсатору.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 647831, кл. Н 02 М 1/08, 1979.

2. Авторское свйдетельство СССР

Р 656161, кл. Н 02 М 1/08, 1976.

955416

Составитель В. Костюхин

Редактор А. Власенко Техред М.Надь Корректор М. Коста

Заказ 6467/71 Тираж 721 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4