Цифровой умножитель частоты

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОИУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Соцналнстнческни

Реслублнк (iii 957206 (6 I ) Дополнительное к авт. свнд-ву (22) Заявлено 20. 11. 80 (21) 3223033/18-24 с присоединением заявки М (23) Прнорнтет

Опубликовано 07.09.82. Бюллетень Ме 33 (53)M. Кл, G О6 F 7/68

Ркудврсткниый кокитет

СССР (53) УДК 681.325 (088.8) пв делен изобретений н Отмрцтий

Дата опубликования описания pg.pg,82 (72) Автор изобретения

Н. А. Камынин

Куйбышевский ордена Трудового Красного Зна институт им. акад. С. П.Королева (7I) Заявитель (54) ДИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к информационно-измерительной технике.

Известен цифровой умно>китель частоты, содержащий формирователь входного сигнала„генератор импульсов эталонной частоты, первый и второй управляемые делители частоты, счетчик к регистр памяти L1 j.

Недостатком данного умножителя является низкая точность -множения часJ

1О то ы, обусловленная возникновением систематической ошибки при неизменной частоте входного сигнала и случайной ошкбки с ненулевым математическим ожиданием при изменении частоты входного сигнала. Кроме того, диапазон частоты входного сигнала этого устройства ограничен целым числом.

Наиболее близким по технической сущ.ности к предлагаемому является цифровой зо умножитель частоты, содержащий формирователь входного сигнала, первый и второй элементы И, первый и второй управляемые делители частоты, первый и вто2 рой регистры памяти, сумматор, триггер и генератор импульсов эталонной частоты (2 j.

Недостатками известного устройства являются невозможность обеспечения умножения входных сигналов на дробный коэффициент и непрерывного формирования выходного сигнала при изменениях частоты на входе умножителя.

Дель изобретения — расширение диалазона коэффициента умно>кения за счет получения ьозмо>кностк умножения на дробный коэффициент и повышение точности умножения прк изменениях входной частоты.

Поставленная цель достигается тем, что в цифровой умножитель частоты, содержащий формирователь входного сигнала, первый и второй элементы И, первый и второй управляемые делители частоты, первый и второй регистры памяти, сумматор, триггер и генератор импульсов эталонной частОты, причем вход формирователя входного сигнала является входом

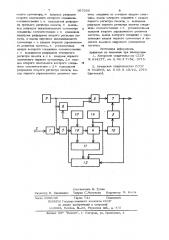

206 4 импульсов, второй регистр 11 памяти, первый сумматор 12, третий и четвертый регистры 13 и 14 памяти, второй накапливающий сумматор 15.

Устройство работает следующим образом.

Сигнал входной последовательности с периодом Т„ поступает на вход формирователя 1 входного сигнала, который формирует управляющие импульсы длительностью Т, которые с выхода 2 формирователя 1 входного сигнала поступают на вход логического элемента

И 3, разрешая прохождение импульсов с частотой f0 с выхода генератора 5 импульсов эталонной частоты на вход накапливающего сумматора 15. Б регистрах 13 и 14 памяти предварительно записаны числа о и р> соответственно.

20 Спустя промежуток времени, равный Т„ на вход сумматора 15 поступает = х оимпульсов, на вход управляемого делителя 4 частоты поступает

Мх-Ь1

Я, импульсоВ, н где n — число разрядов сумматора 15; а.„- остаток, содержащийся в сумматоре 15 по окончанию ин30 тервала времени Т„.

На вход счетчика 10 импульсов поступает

Э 957 умцожителя частоты, выход формирователя входного сигнала соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора импульсов эталонной частоты, с входом установки в единицу триггера и с первым входом второго элемента И, второй вход которого соединен с прямым выходом триг гера, а выход второго элемента И соеди-, нен с входом второго управляемого делителя частоты, разрядных выходов первого управляемого делителя частоты соединены соответственно с и старшими входнымв разрядами второго регистра памяти, а и ход переноса сумматора соедипен с входом установки в ноль триггеpQ, введены счетчик, третий и четвертый регистры памяти и второй накапливающий сумматор, причем выход первого элемента И соединен с управляющим входом . накапливающего сумматора, и входных разрядов второго слагаемого которого соединены соответственно с п выходными разрядами третьего регистра памяти, выходных разрядов накапливающего сумматора соединены соответственно с и младшими разрядами второго регистра памяти, а выход переноса накалливающего сумматора — с входом первого управляемого делителя частоты, н установочных входов которого соединены соответственно с п выходными разрядами четвертого регистра памяти и с и входами первого слагаемого первого сумматора,2 r входов второго слагаемого которого соединены соответственно с 2п входными разрядами второго регистра

ПаМятИ, BbtXOp, ПЕРВОГО унраВЛяЕМОГо делителя частоты соединен со счетным входом счетчика, выход которого соединен с входом первого регистра памяти, и выходных разрядов первого регистра памяти соединены соответственно с и установочными входами второго управляемого делителя частоты> выход которого соединен с управляющим входом первого сумматора и является выходом цифрового умножителя частоты.

На чертеж изображен цифровой умножитель частоты.

Цифровой умножитель частоты содержит формирователь 1 входного сигнала, поступающего по входу 2, первый логический элемент И 3, первый управляемый делитель 4 частоты, генератор 5 импульсов эталонной частоты, второй логический элемент И 6, второй управляемыя делитель 7 частоты, триггер 8, перв,й регистр 9 памяти, счетчик 10 „- т Ъ

35 где а - остаток со импульсов, Если 6„= а = О, то

NcL

ЬЫХ

Ьх" г" р

cL

0 < — (1

Р таккак д (2 1,то

Обозначив с о=а 2", получаем

Т„<

ТЕь!х=

I l держащийся в делителе 4 частоты по око чанию интервала времени тх.

fIo окончанию интервала времени Т„чис

40 ло Й1 из счетчика 10 импульсов переписывается в первый регистр 9 памяти и определяет коэффициент деления второго управляемого делителя 7 частоты, на выходе когорого импульсы будут появляться через интервалы

ЬЫХ

5 9572 т.е. частота выходного сигнала равна

Мх

4ых=—

С О

NoL- Ь

-Ь и 2

Ь, М -Ь т ьых р

Ре !

TÕd0 Ь1

Цифровой умножитель частоты, содержащий формирователь входного сигнала, первый к второй элементы М, первый и второй управляемые делители частоты, первый и второй регистры памяти, сумматор, триггер к генератор импульсов эталонной частоты, прячем вход формирователя входного сигнала является входом цифрового умножителя частоты, выход формирователя входного сигнала соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора импульсов эталонной частоты, с входом установки в единицу триггера и с первым входом второго элемента И, второй вход которого соединен с прямым выходом триггера, выход второго элемента И соединен с входом второго управляемого делителя частоты, и разрядных выходов первого управляемого делителя частоты соединены соответственно с и старшими входными раэрядамк второго регистра памяти, выход переноса сумматора соединен с входом установки в ноль триггере, о т— л и ч а ю шийся тем, что, с целью расширения диапазона коэффициента умножения за счет получения воэможности умножения на дробный коэффициент к повышения то:нос-.,и умножения при изменениях входной частоты, в него введены счетчик, третий и четвертый регистрь, памяти и второй накапливаюшкй -. óììàòîð, причем выход первого элемента И соединен -" управляюшкм входом шжаплква Ч +1

Т

ЬЫх

0 изменяя oL можно получить практически любой, как целый, так и дробный коэффициент умножения с достаточно высокой точностью, так как oLp меняется с шагом

7/1 . В реальных условиях ь1 Ф О, Ь2 Ф О. Это приводит к возникновению о ошибки в формировании выходной последовательности, при этом

Погрешность равна 1

ЬТ=- — + Ь

2n I fP0

Так как каждый выходной импульс име25 ет временной сдвиг дТ относительно идеальной последовательности, то этот сдвиг приводит к появлению накалливающегося временного опережения. С целью периодической компенсации данной погрешностк введены второй регистр 11 памяти, сумматор 12, триггер Я и второй элемент И 6.

В исходном состоянии единичное состояние прямого выхода триггера 8 раэ- 55 решает прохождение импульсов эталонной частоты через второй логический элемент И 6 на вход управляемого делителя 7 частоты. По окончанию временного интервала Т» остатки а„и ь< из 4О сумматора 15 и делителя 4 частоты переписываются во второй регистр 11 памяти. Затем, при появлении очередного

K-го выходного импульса, в сумматоре

2 вычисляется величина (2" р-К (Ь„+ 45 л

+ 1 ь2)). Когда эта величина становится меньше нуля, то импульс с выхода сумматоре. 12 устанавливает на выходе тркггера 8 нулевое состоянке и очередной импульс с выхода генератора 5 не по- 50 ступает на вход делителя 7 частоты, а устанавливает на выходе триггера 8 единичное состояние, поэтому на выходе делителя частоты импульс появляется через интервал времени 55

06 6 а так как в этот момент накопленная

1 ошибка равна КЬТ= то она полностью о компенсируется. С приходом очередного импульса длительностью Т устройство работает аналогично.

Благодаря введению счетчика 10 импульсов обеспечивается непрерывное формирование выходного сигнала к непрерывное слеженке эа изменениями частоты входного сигнала, так как после переписи кода в регистр 9 памяти счетчик 10 импульсов готов к работе, а делителем 7 ыастоты управляет регистр 9 памяти.

Таким образом, по сравнению с известным, предлагаемое устройство полностью устраняет указанные недостатки, что позволяет существенно расширить область применения умножителя.

Формула изобрвтения ющего сумматора, и входных разрядов второго слагаемого которого соединены соответственно с || выходными разрядами третьего регистра памяти, и выход- ных разрядов накапливающего сумматора соединены соответственно с и младшими входными разрядами второго регистра памяти, а выход переноса накапливающего сумматора — с входом первого управляемого делителя частоты, и установочных 16 входов которого соединены соответственно с и выходными разрядами четвертого регистра памяти и с и входами первого слагаемого первого сумматора, 2п входов второго слагаемого которого соеди- 15 иены соответстве|п|о с 2 о выходными разрядами второго регистра памяти, выход первого управляемого делителя частоты соединен со счетным входом счетчика, выход которого соединен с входом первого регистра памяти, п выходных разрядов первого регистра памяти соединены соответственно с || установочными входами второго управляемого делителя частоты, выход которого соединен с управляющим входов первого сумматора и является выходом цифрового умножителя частоты.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

M 634277, кл. Cj 06 F 7/52, 1975.

2. Авторское свидетельство СССР

М 663068, кл. Н 03 В 19/10) 1976 (прототип).

Составитель В. Гусев

Рваактор B. Пиаинвнко Твкрвн С.Мигунова Коррактор М. Коста

Закан 6600УВВ Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„д. 4/5

Филиал ППп "Патент", г. Ужгород, ул. Проектная, 4