Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ()957210

ИЗОВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советскик

Социалистические

Рес убпик (6l ) Дополнительное к авт. сена-ву (22) Заявлено 25. 1 2 ° 80 (21) 3254699/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 07. 09.82. Бюллетень М 33

Дата опубликования описания 12.09.82 (5 I ) M. Кл.

G 06 F 9/22

3Ъсударстееииый комитет

СССР (53) УДК 681.325 (088 . 8) по делан иэеоретеиий и открытий (?2) Авторы изобретения

Б.И. Рувинский и Ю.А. Алексенко (71) Заявитель (54} УСТРОЙСТВО МИКРОПРОГРАММНОГО

УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может найти приме" нение при построении вычислительных устройств с последовательным способом представления информации, в частности микрокалькуляторов.

Известно устройство микропрограммного управления, выполненное на программируемой логической матрице (ПЛМ), содержащее ПЛМ микропрограмм, первые то входы которой соединены с выходом

ПЛМ микропрограмм, а вторые " с шина" ми входных логических условий LI ).

Недостатком такого устройства микропрограммного управления являют1З ся большие размеры матрицы при большом количестве различных входных логич"ских условий. Это приводит к усложнению устройства, особенно при его инте -ральном исполнении. зо

Известно устройство микропрограммного управления, содержащее ПЛМ мик" ропрогоамм, ПЛМ условий, регистр ус" ловий и блок синхронизации. Выход

ПЛМ микропрограмм соединен с первым входом ПЛМ условий и входом ПЛМ микропрограмм, внешний информационный вход устройства соединен с информационным входом регистра условий, выход блока синхронизации соединен с входом регистра условий, выходы которого соединены с входами ПЛМ условий (2).

Недостатком этого устройства является его сложность, так как содержащийся в нем регистр условий - многоразрядный, поскольку на нем должны быть запомнены все логические условия, которые могут воздействовать на входы ПЛМ микропрограмм.

Кроме того, блок синхронизации должен содержать довольно сложную схему, вырабатывающую последовательность синхроимпульсов для занесения всех условий на регистр условий. А связь блока синхронизации через регистр условий с ПЛМ условий усложняет устройтсво, приводит к увеличе95721 нию площади ПЛИ условий при ее интегральном испольнении, поскольку количество различных условий в реальi <. T ä É <- T Er x

Цель изобретения — упрощение устройс ва

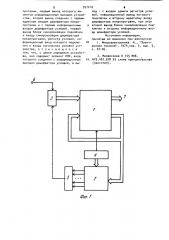

llocòавпенная цель достигается тем, что в устройство микропрограммного управления, содержащее дешифратор микропрограмм, первый выход которого является информационным выходом устройства, второй выход соединен с первым адрес,=.ûì входом дешифратора микропрограмм и с первым информационным входом дешифратора условий, первый выход блока синхронизации подключен к входу синхрснизгции дешифратора микропрограмм, регистр условий, информационный вход которого подключен к входу логических условий. устройства,>О введены элемент ИЛИ, вход которого соединен с информационным выходом дешифратора условий, а выход — с входом сдвига регистра условий, информационный выход которого подключен к второму адресному входу дешифратора ми <ропрограмм, второй выход блока сннхро -.иэации подключен к второму информационному входу дешифоатора усло :-, и у, ЗО -.:а фиг. 1 изображена функциональная схема устройства на Фиг. 2 с;<сма выпîr;:-û;år- .ия дешифратора микро;рограмм; на фиг. 3 — схема выполне, и ия ««е ифратара условий. устройство содержит дешифратор 1 микропрограмм, дешифратор 2 условий, „-.,=-Г- cr-. "." Условий, блок 4 синхрони-:=ци, элемен ИЛИ 5, вход 6 логических условий устройства, информацион;иий -.;ыхо ц 7,«<:òройст ва .

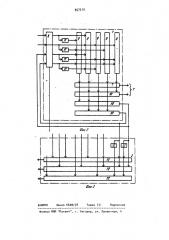

Геиикфратс р микропрограмм (Фиг. 2)

; -;. дс та в ляет собой прог рамми руемую лог. че.-:.. Q матрицу и содержит регистр блок элене;- тов И 9, блок элементо.« !«,ЛИ,9, группу -нверторов 11, ",;, è«Фоатор услсвий (фиг. 3) предс--вверяет собой программируемую логи -,еск"ю матрицу и содержит блок зле,.;вf-<ов И 12 и 1-руппу инверторов 13.

;стро IcTBG работает следующим об«арзом, Г. пе-.;вого выхода дешифратора 1 ми <рогро, рамм на первый вход дешифратора 2 условий пос — óïàåò код адреса следующего состояния дешифратора 1 микропрограмм. На вторые входы дешифрато;;а 2 условий поступают синхрониэируюцие сигналы иэ блока 4 синхрониО 4 зации. На выходах дешифратора 2 условий формируется определенная совокупность. синхроимпульсов для каждого адреса, поступающего на первый вход дешифратора 2 условий. Эта совокупность синхроимпульсов соответствует моментам появления логических условий на входе 6 в данном адресе дешифратора 1 микропрограмм. Выходы дешифратора 2 условий соединены с входами элемента ИЛИ 5, на выходе которого появится последовательность упомянутых выше импульсов, которая поступит затем на сдвиговый вход регистра 3 условий, на вход 6 последовательно во времени и синхронно с импульсами на сдвиговом входе регистра 3 условий поступают логические условия из внешнего регистра данных. Таким образом, в регистр 3 условий будет записана совокупность условий, необходимых для данного адреса дешифратора1 микропрограмм. После этого из блока 4 синхронизации на вход дешифратора 1 микропрограмм поступает синхроимпульс, обеспечивающий считывание иэ дешифратора 1 микропрограмм нового выходного сигнала, поступающего на выход j, и следующего адреса, поступающего на вход дешифратора 2 условий.

Устройство применимо для случая последовательного способа представления информации в регистре данных, когда логические условия формируются последовательно на входе 6. Предлагаемое устройство выгодно отличается от известного, так как требует значительно меньших аппаратурных затрат, поскольку разрядность регистра условий выбирается, исходя из количества условий, проверяемых s каждом конкретном адресе дешифратора 1 микропрограмм„ что значительно меньше общего количества условий. Кроме того упрощается и блок 4 синхронизации, из которого исключается схема, специально формирующая синроимпульсы для записи всех логических условий в регистратор 4 условий, поскольку формирование синхроимпульсов иэ синхронизирующих сигналов выполняется непосредственно в самом дешифраторе 2 условий одновременно с расшифровкой соответствующего кода адреса, поступающего на первый вход дешифратора 2 условий.

Формула изобретения

Устройство микропрограммногo управления, содержащее дешифратор микро957210 программ, первый выход которого является информационным выходом устройства, второй выход соединен с первым адресным входом дешифратора микропрограмм и с первым информационным входом дешифратора условий, первый выход блока синхронизации подключен к входу синхронизации дешифратора микропрограмм, регистр условий, информационный вход которого подключен к входу логических условий уст" ройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит элемент ИЛИ, вход которого соединен с информационным выходом дешифратора условий, а выход — с входом сдвига регистра условий, информационный выход которого подключен к второму адресному входу дешифратора микропрограмм, при этом

s второй выход блока синхронизации подключен к второму информационному входу дешифратора условий, Источники информации, принятые во внимание при экспертизе

1. Микроэлектроника. M. "Элект" ронная техника". 1974,сер. 3, вып. 5, с. 22-26.

2. Микросхема К 145 ИК6, и, ИУ3.487.018 Э3 схема принципиальная (прототип) .