Логарифмический преобразователь

Иллюстрации

Показать всеРеферат

ОП HCAHHE и

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

/б= —.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 15.01 ° 81 (21) 3235781/18-24 (Яф) М Кд 3 с присоединением заявки ¹

G Об F 7/556

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (53) УДК 881. 325 (088. 8) Опубликовано 1509.82, бюллетень ¹ 34

Дата опубликования описания 15.09.82

Ю. В. Хохлов, В.Д. Циделко, Ю. Г. Туманов j

A.И. Литвин, С.В. Ляшенко, B ° A. Тесленк и Н.Н. Барышевский (72) Авторы изобретения

РЛ ".Ы ) (1О ЯХ,1цг р г ;g Й уд(ущЩу е ти я

Киевский ордена Ленина политехнический ин

Великой Октябрьской социалистической ре (71) Заявитель (54) ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области цифровой вычислительной техники и может быть использовано при построении специализированных вычислителей, информационно-измерительных систем, цифровых фильтров и гибридных функциональных преобразователей.

Известен цифровой функциональный преобразователь, построенный; на основе использования табличного преобразования, содержащий накопитель постоянного запоминающего устройства, в котором записана требуемая функциональная зависимость (1).

Несмотря на предельное быстродействие такого преобразователя, его недостатком является значительный объе)ч необходимой памяти.

1Ьиболее близким техническим решением к данному является преобразователь, содержащий и -разрядные сумматор и регистр, входы которого являются входом преобразователя, а его л выходов подключены к соответствующим первым входам сумматора., выход которого является выходом преобразователя,. а также запоминающее устройство, к адресным входам которого подключены (n-2) выхода старших разря-. дов регистра, à (п-3)информационных выхода запоминающего устройства под- ключены к (л-3) вторым входам младших разрядов сумматора (2 ) .

Недостатком преобразователя является необходимость использования сравнительно большого объема памяти.

Цель изобретения - упрощение преобразователя за счет уменьшения суммарного объема блоков памяти.

Поставленная цель достигается тем, что преобразователь, содержащий регистр, сумматор и первый блок памяти, выходы регистра соединены с первыми входами соответствующих разрядов сумматора, вторые входы . п-3 (где и- разрядность. регистра и сумматора) мпадаих разрядов которого соединены с выходами первого блока памяти, содержит коммутатор и второй

20 блок памяти, причем информационные входы коммутатора соединены с п-3 выходами старших, начиная с второго разрядов регистра, выходы коммутатора соединены с входами первого

25 блока памяти, управляющий вход коммутатора соединен с выходом старшего разряда регистра и управляющим входом второго блока памяти, входы которого соединены с и-5 выходами

30 старших, начиная с второго, разря/

959073 дон регистра, выходы нторого блока памяти соединены с третьими входами и-6 младших разрядон сумматора.

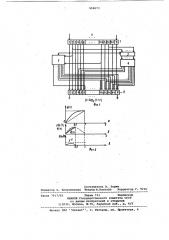

На Фиг. 1 представлена блок-схема устройства; на фиг. 2 — график аппроксимирующей функции. 5

11реобраз онат ель содержит регистр

1, сумматор 2, коммутатор 3, блоки 4 и 5 памяти.

Работа устройства основана на кусочно-линейной аппроксимации лога- fP рИФМИНЕСКОй фуНКцИИ У= ООс т (1+Х), Ке(0, 1) с использованием, таблиц корректирующих функций. График исходной и аппроксимирующих функций показан на Фиг.2,откуда видно,что вход-.. 15 ной код Х содержит часть информации о выходной величине У и может использоваться как грубое приближение исходной функции, причем Ь У1 п,с,„<2 .

Если ввести искусственную сймметрию для Функции л У„(Х) относительно оси

Х-1/2, то получим функцию Ч (Х) . Как видим, функция Ч (X) (фиг. 25) однозначна на сегменте Хе (О, 1/2 ) . Для нее также справедливо неравенство Мщц„(Х) 5 с2, поэтому объем памяти для хранения ее значений вдвое меньше, чем для функции Ь У„(Х) н известном прео образователе. Значения Ч (Х) рассчитываются заранее и заносятся в первый. блок 4 памяти. Для получения ЗО точного логарифмического преобразования на сегмеите Хе(0,1/2) необходимо дополнительно запоминать значения

Функции аут (Х)=а У (Х)-Ч(Х), причем значения функции а У п ах<2 6 записываются во второй блок памяти.

Уравнение преобразования запишется в виде: сегмент Х S (0,1/2); У(Х) = X У(Х)+ Щ

2() сегмент Х В (1/2,1); У(Х) =Х (1-X) .

Вторая корректирующая функция

d Jg (Х) на втором сегменте не используется, а в качестве аргумента для функции Ч.(Х) берется его дополнение до единицы, т.е. его обратный код.

Таким образом, работа коммутатора 3 заключается в том, что для значений

Х 6 (0,1/2) он пропускает значения Х без изменения, а для сегмента

Х е. (1/2,1) значения аргумента X инверФируются. Управление коммутатором

3 Ä очевидно, осуществляется старшим разрядом кода аргумента Х. На практике ко утатор легко ре изуется 55 на элеМентах СЛОЖЕНИЕ ПО МОДУЛЮ ДВА (например, интегральных микросхемах

К155ЛП5). При Этом первые входы этих . микросхем подключаются к выходам регистра, а вторые входы объединяются 60 и используются для управления режимом передачи. Возможны также и другие реализации коммутатора.

Время Преобразования данного преобразователя находится в пределах (2-3) @„g, где э,g- время выборки из блока памяти, которое определяется только типом используемах элементов и может быть очень малым. Объем используемой памяти уменьшен по сравнению с прототипом примерно в

1,8 раза. Преимуществом данного преобразователя является полностью комбинационный принцип его работы, что исключает необходимость использования схем синхронизации (кроме приема входного кода аргумента) и управления.

Предложенный преобразователь позволяет эффективно вычислять двоичные логарифма нормализированных чисел, что может быть использовано при построении различного рода устройств реального нремени и повышения производительности микропроцессорных систем.

Формула изобретения, Логарифмический преобразователь, содержащий регистр, сумматор и первый блок памяти, выходы регистра соединены .с первыми входами соответствующих разрядов сумматора, вторые входы и -3(где и — разрядность регистра и сумматора) младших разрядон которого соединены с выходами первого блока памяти, о тл и ч а ю шийся тем, что, с целью упрощения преобразователя за счет сокращения суммарного объема блоков памяти, он содержит коммутатор и второй блок памяти, причем информационные входы коммутатора соединены с и -3 выходами старших, начиная с второго, разрядов регистра, выходы коммутатора соединены с входами первого блока памяти, управляющий вход коммутатора соединен с выходом старшего разряда регистра и управляющим входом второго блока памяти, входы которого соединены с и-5 выходами старших, начиная с второго, разрядов регистра, выходы второго блока памяти соединены с третьими входами п -б младших разрядов сумматора.

Источники информации, принятые во внимание при экспертизе

1. Электронные цифровые вычислительные машины. Под ред. К.Г. СамоФалова. К., Вища школа, 1976, с. 247-248.

2. Авторское свидетельство СССР по заявке М 2855614/18-24, кл . G 06 F 7/557,(прототип) .

959073

И fs

tp(xp

Фиг.g

Тираж 731 Подписное . вНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Закаэ 7017/65

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель A. Эорин

Редактор О. Колесникова Техред N.Коштура Корректор Г. Огар