Цифровой коррелятор для обнаружения эхо-сигналов

Иллюстрации

Показать всеРеферат

(ц)959091

Союз Советскик

Социалистически»

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.1280 (21) 3215910/18-24 (51) М. Иа.з с присоединением заявки №

G 06 F 15/336

Государствеииый комитет

СССР ио делам изобретений и открытий

)53) УДК 681. 323 (088.8) (23) Приоритет

Опубликовано 150982. Бюллетень ¹ 34

Дата опубликования описания 150982 (72) Авторы изобретения :

В.Д. Анисимов и Е.Н. Литман (7t) Заявитель (54) ЦИФРОВОЙ КОРРЕЛЯТОР ДЛЯ ОБНАРУЖЕНИЯ

ЭХО-СИГНАЛОВ

Изобретение:относится .к области. специализированных средств вычислительной техники, предназначенной для взаимнокорреляционной обработки зхо-сигналов.

Известей цифровой коррелятор содержащий, частотно-импульсный преобразователь, логические блоки, блок . .задержки, реверсивные счетчики $1).

Однако данный коррелятор характЕрнзуется недостаточно высоким отношением сигнал - шум на выходе.

Известен также коррелятор, содержащий два блока задержки„ арифмети:ческий блок, накапливающий сумматор и блок управления (2).

Недостатком этого коррелятора as-. ляе©ся.неидентичность .обработки сиг-. налов (опорного и входного), так как в первый блок задержки записываются прореженные выборки опорного сигнала, а непрореженные выборки входного сигнала со второго блока задержки подвергаются перед подачей в арифметический блок предварительному суммированию. Это приводит к уменьшению точности вычисления:ординат взаимокорреляционной функции (ВКФ),. при чем величины ошибок различны при формировании различных зондирующих сиг налов ° Кроме того, при обработке непрерывных сигналов или сигналов значительной длительности требуется непрерывное обновление памяти не только второго, но и первого блока задержки.

Цель изобретения » »повьваЕние точности вычисления ординат ВКФ и расширение функциональных воэможностей коррелятора.

Сущность изобретения заключается в том, что обеспечивается идентичность обработки входного и опорного сигналов, включая непрерывное обнов15 ление информации в памяти корреклятора.

Поставленная цель достигаетс тем, что в цифровой коррелятор для обнаружения эхо-сигналов содержащий первый и второй блоки задержки, входы которых являются соответственно первым и вторым входами коррелятора, в выход второго блока задержки соединен со входом первого накапливающего сум25 матора, выход"которого подключен к первому входу арифметического блока, входы синхронизации арифметического блока и накапливающего сумматора подключены к первому выходу блока уп30 равления второй выход которого соеди-

959091

65 нен с управляющими входами блоков задержки, введен второй накапливающий сумматор, вход которого подключен к выходу первого блока задержки, выход соединен со вторым входом арифметического блока, а вход синхрони- 5 эации второго накапливающего сумматора подключен к первому выходу блока управления.

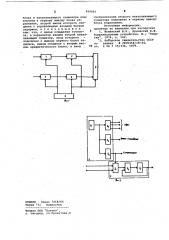

На фиг. 1 изображена структурная схема цифрового коррелятора, на 10 фиг.,2 — структурные схемы арифметического блока и блока управления.

Коррелятор содержит два блока задержки 1 и 2, два накапливающих сум матора 3 и 4, арифметический блок 5 и блок 6 управления, первый выход которого соединен с входами синхронизации накапливающих сумматоров 3, 4 и с управляющим входом блока 5, второй выход блока управления б соединен с управляющими входами блоков задержки 1 и 2, выход блока 1 соединен.через накапливающий сумматор 3 с первым входом блока 5, а выход блока

2 соединен через накапливающий сумматор 4 со вторым входом арифметического блока 5.

На фиг. 2 приведены структурные

;схемы арифметического блока 5 и блока б управления для случая, когда в качестве блоков 1 и 2 задержки -ЗО используются оперативные запоминающие устройства (ОЗУ) соответственно.

Арифметический блок 5 содержит последовательно соединенные блок умножения 5, и. накопитель, реалиэо- 35 ванный на комбинационном сумматоре

5 и элементе 5> памяти. Выход элемента 5э соединен с выходом коррелятора и со вторым входом комбинационного сумматора 5>. 40

Блок .6 управления содержит генератор 64 тактовых импульсов, счетчик 6 адресов, выходы которого подключены к адресным входам ОЗУ1 и ОЗУ2, счетчик б команд "Запись-Считывание", выход которого подключен к управляющим входам ОЗУ1 и ОЗУ2 и счетчик 64 синхронизации, выход которого подключен к синхронизирующим входам блока В умножения и накапливающих сум-, маторов 3 и 4 коррелятора., Счетчик б адресов обнуляется

М-1 входным импульсом, счетчик б команд "Запись-Считывание" обнуляется H-м входным импульсом.

Таким образом, обеспечивается по".следовательная запись входной информации в ячейки памяти ОЗУ1 и ОЗУ2.

Счетчик.64 синхронизации обнуля-. ется входным импульсом, фиксируя начало и конец интервала предва- 60 рительиого суммирования накапливающими сумматорами 3 и 4 корреклятора.

Для случая М = 4048 и = 4-8 арифметический блок и блок управле,ния реализованы на ИМС 133 серии.

Блоки задержки 1 и 2 реализованы на ОЗУ 505 Р .

Работа цифрового коррелятора происходит следующим образом.

В блоки задержки 1 и 2 с памятью

N непрерывно поступают непрореженные выборки входного и опорного сигналов. За время между двумя соседними выборками, поступающими на вход коррелятора, происходит опрос блоков

1 и 2, причем скорость опроса обоих блоков задержки одинакова. С их выходов выборки поступают на соответствующие входы накапливающих сумматоров 3 и 4, которые осуществляют текущее суммирование по t выборок из блоков 1, 2 соответственно. Результаты соответствующих суммирований образуют пару выборок, которая поступает в арифметический блок, где вы-. борки, образующие пару, перемножаются с последующим суммированием на интервале усреднения ° Таким образом, за время между двумя выборками, последовательно поступающими на вход коррелятора, осуществлен полный опрос памяти блока задержки 1 и 2 и образование N/E nap выборок, произведено перемножение выборок составляющих пары, а результат умножения усреднен. Вычисление следующей ординаты

ВКФ происходит на следующем интервале между входными выборками, поступающими на вход аналогичным методом, при этом самая "старая" выборка в памяти блоков задержки 1 и 2 заменяется вновь поступившей. Вычисление ВКФ происходит непрерывно, информация снимается с выхода коррелятора в темпе поступления входных выборок, т.е. коррелятор обеспечивает обработку входного сигнала в реальном масштабе времени. БУ предлагаемого устройства аналогичен известному. Изменять задержку между входным и опорным сигналами можно с помощью дополнительного устройства задержки (на фиг. 1 . не показано).

Использование данного устройства позволит реализовать более высокие точностные параметры обнаружения и анализа и расширить функциональные возможности тракта обработки сигналов.

Формула изобретения

Цифровой Коррелятор для обнаружения эхо-сигналов, содержащий первый и второй блоки задержки, входы которых являются соответственно первым и вторым входами коррелятора, выход второго блока задержки, соединен с входом первого накапливающего сумматора, выход которого подключен к первому входу арифметического блока, входы синхронизации арифметического

959091 блока и накапливающего сумматора подключены к первому выходу блока управления, второй выход которого соединен с управляющими входами блоков задержки, отличающийся тем, что, с целью повышения точности, в коррелятор введен второй накапливающий сумматор, вход которого подключен к выходу первого блока задержки, выход соединен с вторым входом арифметического блока, а вход 30

ВНИИПИ Заказ 7018/66

Тираж 731 Подписное

Филиал ППП "Патент", r,. Ужгород, ул.Проектная,4 синхронизации второго накапливающего сумматора подключен к первому выходу блока управления.

Источники информации, принятые во внимание при экспертизе

1. Жовинский В.Н., Арховский В.Ф.

Корреляционные устройства. М.; "Энергия", 1974, с. 142. 2, Авторское свидетельство СССР по заявке 9 2876354/18-24, кл. G 06 F 15/336, 1979 °