Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ ф

"Ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 17.12. 80 (21) 3242885/18-24 ($ t) М. КП. с присоединением заявки ¹

G 11 С 11/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 150982, Бюллетень ¹ 34

) 3) УДК 681.327 (088. 8) Дата опубликования описания 15. 09 . 82 (72) Авторы изобретения

T .М.Агаханян, И.С.Любченко, Ю.П.Фирстов, и М.И.Якобсон

МоскЬвский ордена Трудового Красного Зна инженерно-физический институт (71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЦКс УСТРОЙСТВО

Изобретение относится к запоми- . нающим устройствам и может быть использовано:в высокопроизводительных типовых. модульных системах. сбора и обработкн информации.

Известно оперативное -;.àïîìèíàþщее устройство (ОЗУ) выполненное на микросхемах 527 РУ2 (13.

Недостатком этого устройства являются ограниченные функциональные возможности, что не позволяет ггспользовать его в системах сбора и обработки информации с высокой производительностью. Кроме того, система команд накладывает принципиальные ограничения на объем памяти.

Наиболее близким техническим решением к данному изобретению явля ется ОЗУ, содержащее накопители, входные регистры, адресный регистр, мультиплексоры, схему управления, " блоки согласования, логические эле-. менты .Г2).

Недостатками известного ОЗУ яв-, ляются ограниченные функциональные возможности. В частности, невозможно использовать ОЗУ в качестве.таб» личного вычислителя для коррекции записанных в него экспериментальных данных. Кроме того, система команд и архитектура накладывают ограничения на увеличение объема ОЗУ, так как возможна только прямая адресация ОЗУ, что крайне усложняет работу с большим массивом данных; при большом объеме ОЗУ ограничения по мощности не дают возможности использовать быстрые микросхемы памяти, что приводит к резкой потере быстродействия; выведение данных из больших массивов ОЗУ требует много времени, так как отсутствует возможность проведения поисковых операций, предварительных операций с массивами.

Целью изобретения является расширение функциональных возможностей устройства за счет выполнения логи20 ческих и арифметических операций.

Поставленная цель достигается тем, что в оперативное запоминающее уст. ройство, содержащее первый и второй входные мультиплексоры, первый и второй в.-.îäíûå регистры, регистр адреса, блок согласования уровней напряжения, регистр управляющей информации, первый выходной мультиплексор, первый,второй и третий накопители, nepayh и вторую группы усилителей, причем входы накопителей подключены к

959159 выходам регистра адреса, первого входного гэгистра и второго входного мультиплексора, входы которого подключены к выходам второго входного регистра и первого входного регистра, входы которого соединены с выходами первого входного мультиплексора, выходы первого выходного мультиплексора подключены к входам усилителей пер. вой группы, одни из входов первого выходного мультиплексора подключены к выходам накопителей и выходам регистра Управляющей информации, входы усилителей второй группы соединены с выходами третьего накопителя, введены первая и вторая группы регистров, второй выходной мультиплексор, третий входной мультиплек-. сор, регистр команд, логический блок, регистр кодов операций, дополнительный регистр адреса и четвертый накопитель, входы которого подключены к выходам регистра адреса, а выходы— к одним из входов второго выходного мультиплексора, другие входы которого соединены .с выходами первого входного регистра к дополнительного регистра адреса, выходы логического блока подключены соответственно к одним из входов второго входного мультиплексора, входам регистра адре- Зр са, другим входам первого выходного мультиплексора и одним из входов первого входного мультиплексора, входы логического блока соединены соответственно с выходами регистра 35 кодов операций и выхОдами регистров групп, одни иэ входов которых подключены к выходам регистра команд, а другие -, к выходам второго входного мультиплексора, другие вхо- 4р ды которого соединены с выходами первого входного мультиплексора,и блока согласования уровней напряжения, входы которого подключены к выходам первого выходного мультиклексора, 45

-входы регистра команд, регистра кодов операций, дополнительного регистра адреса являются одними из входов устройства, выход второго выходного мультиплексора является . одним иэ выходов устройства.

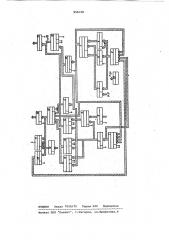

На чертеже изображена Функт(иональная схема оперативного запоминающего устройства.

Оперативное запоминающее устройство содержит первый 1 и второй 2 входные мультиплексоры, первую 3 и вторую 4 группу регистров, первый 5 . и второй 6 входные регистры, логический блок 7, выполненный в .виде сборки стандартных микросхем 155 ИПЗ, 6Р выполняющей стандартный набор функций 3, третий входной мультиплексор

8, регистр 9 управляющей информации, первый выходной мультиплексор 10 второй .выходной мультиплексор 11, 65 предназначенный для передачи на выход устройс1ва Запроса обслуживания однобитной информации, первый 12, второй 13 к третий 14 накопители, четвертый накопитель 15, предназначенный. для проведения операций над массивами данных, хранящихся в накопктелях 12 и 13, первую 16 и вторую

17 группы усилителей, регистр 18 ад реса дополнительный регистр 19 адреса, предназначенный для хранения кода, определяющего номер бита информации, выводимого мультиплексором

ll, регистр 20 команд, регистр 21 кода операций и блок 22 согласования уровней.. напряжений.

ОЗУ может работать в режимах записи и считывания информации, а также проведения арифметических операций и операций над массивами.

Возможны следующие режимы работы устройства: запись в регистр 5 и одновременно в регистр группы 4, за-. пись в один из регистров группы 3, запись информации в накопители 1214, запись информации в регистр группы 4 и подготовка к считыванию иэ ячейки накопителей 13 и 14., запись кода операции в регистр 21, перезапись содержимого ячейки памяти накопителя. в регистр группы 3, подготовка к считыванию ячейки памяти накопителя, запись в накопитель 12 (13) содержимого регистра 5(б), счи-.. тывание информации с.выходов блока 7, читыванке содержимого регистра 9. "

В качестве примера рассмотрим режим записи в накопители 12-14 12разрядного слова.

ИнфорМация, которую необходимо записать, поступает с входов устройства в регистр 5 и записывается в него по первому тактовому импульсу. По второму тактовому импульсу генерируется сигнал Выбор кристалла для накопителей 12 и 13 и сигнал ответа на:.. выходе устройства.

Прк обращении к накопителям 13, и 14 адрес формируется как сумма содержимого регистров групп 3 и 4.

При организации цараллельной модульной магистральной системы на основе предложенного.ОЗУ, в стандарте KANAK возможна, быстрая реализация алгоритмов.

3J

Поиск максимума записанной в модулях. информации. В режиме.автоматического наращивания адреса выбирается содержимое ячеек накопителей 12 и 13 к в накопитель 15 по адресу, определяемому этим числом, записывается l . По окончании этого процесса в режиме последовательного убывания адреса производится считывание из. накопителя 15. При считывании из наконителя 15 1 модуль

959159 отключается. Аналогиуно можно производить поиск минимума.

Иодуль позволяет производить смещение информации по амплитуде на некоторую величину.

Предложенное устройство. также способно производить построение гистограмм, имеется возможность организации режима многоканального анализатора, памяти цифрового фильтра (обеспечивается широкими возможностями адресации), режима табличного вычислителя и другие функции.

При организации параллельной структуры за счет возможности совмещения операций. достигается устранение недостатков, связанных с малым быстродействием большого объема памяти. За счет возможности выведения однобитной информации имеется; возможность организации из модулей

ОЗУ и специального вычисления быстрых вычислительных структур.

Формула изобретения

Оперативное запоминающее устройство, содержащее первый и второй входные мультиплексоры, первый и второй входные регистры, регистр адреса, блок согласования уровней, напряже-. ния, регистр управляющей информации, первый выходной мультиплексор, первый, второй и третий накопители, первую и вторую группы усилителей, причем входы накопителей подключены,к выходам регистра адреса, первого входного регистра и второго: входного мультиплексора, входы которого подключены к выходам второго входного регистра к первого вход. ного регистра, входы которого соедийены с выходами первого входного мультиплексора, выходы первого выходного мультиплексора подключены: к входам усилителей первой группы, одни из входов первого выходного мультиплексора подключены к выходам накопителей и выходам регистра уп- : равляющей информации, входы усилителей второй группы соединены с вйходами третьего накопителя, о т— л и ч а ю щ е е с я тем, что, с целью расширения функциональных воз,можностей устройства за счет выполнения логических и арифметических .операций, оно содержит первую и вторую групйы регистров, второй выходной мультиплексор, третий. входной мультиплексор., регистр команд, логический блок, регистр кодов опе— раций, дополнительный регистр адреса и четвертый накопитель, входы которого подключены к выходам регистра адреса, а выходы — к одним из входов второго выходного мультиплек- сора, другие входы которого соедине15 ны с выходами первого входного регистра и дополнительного регистра адреса, выходы логического блока

° подключены соответственно к одним из входов .второго входного мульти2g плексора, входам регистра адреса, другкм входам первого выходного мультиплексора и одним из входов первого входного мультиплексора, входы логического блока соединены

25 соответственно с выходами регистра кодов операций и выходами регистров групп, одни из входов которых подключены к выходам регистра команд, а другие — к выходам второго вход39 ного мультиплексора, другие входы которого соединены с выходами первого входного мультиплексора и блоа. ка согласования уровней напряжения, входы которого подключены к выходам

35 первого выходного мультиплексора, входы регистра команд, регистра кодов операций, дополнительного регистра адреса являются одними из входов устройства, вход второго выходного

4О мультиплексора является одним из выходов устройства.

Источники информации, принятые во внимание при экспертизе

1. Описание модуля ОЗУ 1. Каталог,модулей КАИАК. М., ИРЭА СО AH СССР, 1978»

В

2. Проспект фирмы Enertec Schbum-

berger., CANAC Nemory пюйпЯе type

УИ1 -40, 1977 (прОтотип).