Однофазный сдвиговый регистр

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву

Союз Советских

Социалистических

Республик

<>959163

Ф. (22) Заявлено 04.12.80 (21) 3211792/18-24

Р1УМ К з с присоединением заявки ¹â€” (23) Приоритет

11 С 19/00

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 1 0982, Бюллетень №34

Дата опубликования описания 15. 09. 82

f53) УДК 681. 327, . 66 (088. 8) A.Ä.Âäîâè÷åíêî, Ю.В.Гуляев, Ю.М.Клименко, Ю.Н.Субботин и Г.И.Фурсин (72) Авторы изобретения

Иосковский ордена Трудового Красного Знаме физико-технический институт (71) Заявитель (54) ОДНОФЛЗНЫЙ СДВИГОВЫИ РЕГИСТР

Изобретение относится к автоматике и вычислительной технике.

В. различной радиоэлектронной аппаратуре широко используются сдвиговые регистры, например, при построении операционных и управляющих автоматов вычислительных машин как последовательного, так и параллельного действия. 10

Известен реверсивный сдвиговый регистр, выполненный на RS<-триггерах (1).

Недостатком такого регистра является необходимость применения логических элементов в цепях передачи информации с триггера на триггер.

Наиболее близким к предлагаемому по технической сущности является однофазный сдвиговый регистр, содержащий в каждом разряде первый и вторбй триггеры, выход второго триггера соединен с входом установки первого триггера, вход установки второго триггера каждого разряда, кроме первого, соединен с выходом первого триггера предыдущего разряда, входы сброса вторых триггеров соединены с тактирующим входом регистра, вход установки второго триггера первого разряда является информационным входом регистра, выход первого триггера последнего разряда является информационным выходом регистра (2 ).

Недостатками известного сдвигового регистра являются невозможность реверсивного сдвига чисел и обусловленная этим его узкая обЛасть применения.

Целью изобретения является расширение области применения регистра эа счет осуществления реверсив ного сдвига.

Поставленная цель достигается тем, что в регистр введены элемент ИЛИ-НЕ и в каждый разряд регистра третий триггер, причем вход установки первого триггера соединен с выходом третьего триггера, другой выход первого триггера каждого разряда, кроме первого, соединен с входом установки третьего триггера предыдущего разряда, вход установки третьего триггера последнего разряда является дополнительным информационным входом регистра, другой выход первого триггера первого разряда является дополнительным информацион ным выходом регистра, входы сброса третьих триггеров соединены с дополнительным тактирующим входом ре959163

65 гистра и первым входом элемента ИЛИНЕ, второ.. вход элемента ИЛИ-HF. соединен с тактирующим входом регист.ра, входы .сброса первых триггеров соединены с выходом элемента ИЛИ-НЕ. .Каждый триггер выполнен на и-р-итранзисторе Шоттки и трехколлекторном р-п-р-транзисторе, база р-и-ртранзистора соединена с коллектором и-р-и-транзистора Шоттки эмиттер

Р

10 и-р-и-транзистора Uîòòêè соединен с шиной нулевого по".енциала, база и-р-и-транзистора Шоттки соединена с третьим коллектором р-и-р-транзистора и является входом установки триггера, первый.и второй кол,лекторы р-и-р-транзистора являются выходами триггера, эмиттер р-п-ртранзистора является третьим входом сброса триггера.

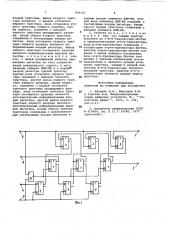

На фиг.l представлена функциональная схема реверсивного однофазного сдвигового регистра; на фиг.2 электрическая схема триггера и его. обозначение, использованное на фиг.l.

Сдвиговый регистр содержит в каждом разряде три триггера — первый триггер 1, второй триггер 2, третий триггер 3. Сдвиговый регистр содержит также информационный вход 4, 30 информационный выход 5, через которые осуществляются соответственно ввод и вывод кода числа, начиная с младших разрядов, тактирующий вход 6, посредством которого осуществляется. 35 последовательная передача информации в регистре от старших разрядов к младшим, дополнительные информационный вход 7 и информационный выход

8, через которые осуществляется со- 40 ответственно ввод и вывод кода числа, начиная со старших разрядов, дополнительный тактирующий вход 9, посредством которого осуществляется последовательная передача инфор- 45 мации в регистре от младших разрядов к старшим, и двухвходовый элемент .ИЛИ-НЕ 10.

Каждый триггер 1,2 и 3 выполнен на и-р-и-транзисторе Шоттки 11 и трехколлекторном р-и-р-транзисто50 ре 12. База p.-n-р-транзистора 12 соединена с коллектором и-р-итранзистора Шоттки 11, эмиттер транзистора Шоттки 11 соединен с шиной нулевого потенциала (заземлен).

База и-р-п-транзистора Шоттки ll соединена с третьим коллектором р-и-р-транзистора 12 и является входом установки 13 триггера. Первый и второй коллекторы р-и-р-транзис- 60 тора 12 14 15 трИггера. Эмиттер р-и-р-транзистора 12 является входом сброса 16 триггера, при этом между входом 16 и эмиттером р-и-р-транзистора 12 может включаться ограничительный резистор 17.

Принцип действия регистра следующий.

В исходном состоянии,на все входы регистра поданы логические О.

При последовательной записи кода числа, начиная с младших разрядов, входной сигнал подается на информационный вход 4 регистра одновременно с сигналом Tä =1 на тактирующем входе б прямого сдвига. Когда сигнал

Tä =1 на тактирующем входе б прямого сдвига окончится и на .нем будет присутствовать логический О,произой-1 дет перезапись информации из триггера 2 каждого разряда в триггер 1 этого же разряда.Для того, чтобы записать код числа во все разряды N-разрядного регистра, на вход б необходимо подать и тактов, и только после этого на информационном выходе 5 регистра появится сигнал, соответствующий информации, которая была подана на,вход 4 регистра в первый такт.

При обратной последовательности записи кода числа, начиная со старших разрядов, входной сигнал подается на дополнительный информационный вход 7 регистра одновременно с сигналом T =1 на дополнительном тактирующем входе 9 обратного сдви-: га, при этом сигнал T„ на тактирующем входе 6 прямого сдвига регистра и входной сигнал на информационном входе 4 регистра равны логическому

О. Так же, как и в предыдущем случае, для того, чтобы записать код числа во все разряды и-разрядного регистра, на вход 9 необходимо подать и тактов, и только после этого на дополнительном информационном .выходе

8 регистра появится сигнал, соответствующий информации, которая была подана на дополнительный информационный вход 7 регистра в первый такт.

В предложенном регистре после ввода информации через информациойный вход 4 возможен вывод записанной информации через дополнительный ин-, формационный выход 8. Аналогично этому можно вводить информацию через вход 7, а выводить через выход 5 °

Принцип действия триггеров 3.,2 и 3 поясняется фиг.2. При подаче на вход сброса 16 триггера логической

1 (соответствующей положительному потенциалу. О,7-3 В) поступление логической 1 (соответствующей втекающему в базу и-р-и-транзистора току величиной 1-10 мкА) на вход установки 13 приводит к регенеративному процессу увеличения тока в триггере.

При этом. триггер включается и появляется ток, вытекающий из первого..

959163 и второго коллекторов р-и-р-транзис:тора 12, соединенных с выходами 14 и 15 триггера. Этот вытекающий ток соответствует логической 1. Отсутствие тока в триггере, вытекающего из первого и второго коллекторов р;-и-ртранзистора, соответствует логическому 0 и не позволяет осуществить регенеративное увеличение тока в следующем, связанном с ним, триггере. °

Резистор 17 (показанный на фиг.2 пунктиром), имеющий обычно сопротив-:. ление около 1-3 кОм, используется для обеспечения устойчивой работы ,регистра в широком температурном диапазоне (от -60 до +125ОС). Если же определяющим требованием является высокая степень интеграции и большая информационная емкость, а температурный диапазон составляет от -10 до +70ОС, то указанный резистор может отсутствовать или может иметь малое сопротивление (50-100 Ом).

Триггер (фиг.2) характеризуется двумя параметрами — временем включения э „ и временем выключения ь 8 „. Время вкпб определяется как время между появлением логической 1 на выходах 14 и 15 и вызвавшей это такой комбинацией сигналов на входах 13 и 16, когда либо при наличии логической 1 на входе 13 появляется логическая 1 на входе 16, либо при наличии логической 1 на входе 16 появляется логическая 1 на входе 13; при этом считается, что первоначально триггер находится в выключенном состоянии. Очевидно, что для успешной работы регистра минимальная длительность сигнала на входе 13 должна быть не меньше е „

Время вы„„ определяется как время между исчезновением логической 1 на входе 16 и исчезновением логической

1 на выходах 14 и 15; при этом считается, что первоначальной триггер был включен. Время переключения элемента ИЛИ-НЕ в функциональной схе. ме, приведенной на фиг.l, определяется обычным способом как время включения „о из состояния логической 1 в состояние логического 0 и как время выключения 7 „ из состояния логического 0 в состояние логической 1.

Учитывая возможную расфазировку сигналов на выходе элемента 10 и входе б (или входе 9), для надежного функционирования регистра необходимо выполнение следующих условий.

Для записи логической 1 из триггера 2 (или триггера 3) в триггер 1 необходимо, чтобы у ("О1 "екл - "еыкл

Условия записи логической 1 из триггера 1 в -триггер 2 аналогично. При поступлении логической 1 на вход б или на вход 9) в течение времени

7 0 на входе б (или на входе 9) и на выходе элемента 10 ИЛИ-HE одновременно будет присутствовать логи-. ческая 1, что может привести после включения триггера 2 (или триггера

3) хотя бы в одном из разрядов регистра к включению триггера 1 того же разряда, а этого не должно быть при правильной работе регистра, т.е. необходимо выполнение условия

"1О "ЕКЛ

Приведенные условия выполняются на практике при различных способах

15 реализации сдвиговых регистров.

Например, при использовании для создания предложенного регистра технологии, применяемой для изготовления ТТЛ-схем с диодами Нотткн, "gun лежит в пределах 5-10 нс,тем„„ лежит в пределах i15-20 нс. Для элемента ИЛИ-НЕ, выполненного по этой же технологии, параметры Т„, и р„ лежат в пределах 0,7-3 нс.

25 Вследствие статического переноса информации в предложенном реверсивном .однофазном сдвиговом регистре минимальная частота сигналов на входе б (или на входе 9) равна нулю. Максима3О льно допустимая частота Й, „ определяется временем выключения триггеров 1, 2 или 3 регистра после исчезновения логической 1 на входе Ъб.

Следовательно, для предложенного 5 Регистра максимальная частота сигнала, поступающего на вход б (или на вход 9), составляет 5-25 МГц.

Предложенный сдвиговый регистр позволяет осуществить реверсивный сдвиг, ввод и вывод кода числа, на4О чиная со старших разрядов, упростить управление регистром (при сдвиге информации используется лишь один такти. рующий вход), расширить его функциональные воэможности. Достоинством

45 предложенного регистра является статический перенос информации (в отличие от динамических регистров на

МДП-транзисторах), когда на тактирующие входы б и 9 могут поступать как

50 периодические, так и непериодические сигналы.

Для изготовления предложенного регистра используется стандартная и хорошо освоенная в серийном произ55 водстве.технология ТТЛ-схем с диодами Шоттки. Предложенный регистр позволяет увеличить информационную емкость кристалла более чем на порядок по сравнению с другими извест6р ными регистрами со статическим переносом информации и получить до 4-64 килобит на кристалле.

Формула изобретения

1. Однофазный сдвиговый регистр, 65 содержащий в каждом разряде первый и

959163 второй триггеры, выход второго триггера соединен с входом установки первого триггера, вход установки второго триггера каждого разряда, кроме первого, соединен с выходом первого триггера предыдущего разряда, входы сброса второго триггера соединены с тактирующим входом ре" гистра, вход установки второго триггера первого разряда является информационным входом регистра, выход первого триггера последнего разряда является информационным выходом регистра, отличающийся тем, что, с целью расширении области применения регистра за счет осуществления реверсивного сдвига, в него введены элемент ИЛИ-НЕ и в каждый разряд регистра третий триггер, причем вход установки первого триггера соединен с выходом третьего триггера, другой выход первого триггера каждого разряда, кроме первого, соединен с входом установки третьего триггера предыдущего разряда, вход установки третьего триггера последнего разряда является дополнительным информационным входом регистра, другой выход первого триггера nepaoro разряда является дополнительным информационным выходом регистра, входы сброса третьих триггеров соединены с дополнительным тактирующим входом регистра и первым входом элемента ИЛИ-HE второй вход элемента ИЛИ-НЕ соединен с тактирующим входом регистра, входы сброса первых триггеров соединены с выходом элемента ИЛИ-.НЕ.

5 . 2. Регистр по п.l,. о т л и ч а юшийся тем, что каждый триггер выполнен íà и-р-и-транзисторе Шоттки и трехколлекторном р-п-р-транзисторе, база р-и-р-транзистора соединена с

10 коллектором и p-Il-транзистора Шоттки, эмиттер и-р-и-транзистора Шоттки соединен с шиной нулевого потенциала, база и-р-и-транзистора Шоттки соединена с третьим коллектором р-и-р15 транзистора и является входом установки триггера, первый и второй. коллекторы р-и-р-транзистора являются выходами триггера, эмиттер р-и-ртранзистора является входом сброса

gp триггера.

Источники информации, принятые во внимание при экспертизе

1. Букреев И.H., Мансуров В.М. и Горячев В.И. Микрозлектронные схемы цифровых устройств, М., Советсткое радио, 1973, с. 122, рис.4 ° 17..

2. Авторское свидетельство СССР

Р 410464, кл. G 11 С 19/00, 1972 (прототип).

9591б3

Фиг. 2

Составитель A.Äåðþãèí

Техред И.Гайду Корректор Ю.Макаренко

Редактор О.Персиянцева

Заказ 7050/70 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, П-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Я

19