Аналого-цифровой стробоскопический преобразователь

Иллюстрации

Показать всеРеферат

(54) . АНАЛОГО-БИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ

П РЕОБРАЗОВА ТЕЛ Ь

Изобретение относится к измерительной технике и используется для построения пифровых стробоскопических вольтметров.

Известен аналого-пирровой стробоскопический преобразователь, содержатцийдискриминатор мгновенных значений (ДМЗ)

5 подключенный одним входом к выходу строб-генератора, другим - по входу усч ройства,.третьим - к выходу цифроаналогового преобразователя (БАП) и блок управления, подключенный первым выходом.i входу декадного счетчика. Устройство содержит также два реверснвных счетчика, два коммутатора, две схемы:совпадения и многовходовы| вентиль 1Ц . 15

Недостатком данного устройства явля ется низкое быстродействие преобразования в произвольно выбранной точке.

Бель изобретения - повышение быстродействия преобразователя.

Поставленная пель достигается тем, что в аналого-пифровой стробоскопический преобразователь, содержащий дискриминатор мгновенных значений, первый вход

2 которого соединен с выходом ифроанало гового преобразователя, второй вход - с выходом строб-генератора, третий вход с первым выходом источника:входного напряжения, второй вход которого соединен с первым входом блока управления, первый выход которого соединен с входоМ сброса декадного реверсивного счетчика, второй выход - с входом вычитания декадного реверсивного счетчика, третий выI ход - с входом сложения декадного ревер; сивного счетчика; четвертый выход — с входом строб-генератора, введены два триггера, регистр сдвига и регистр хранения, прямые выходы всех разрядов кот6рого соединены с входами цифроаналого- вого преобразователя, инверсный выход старшего. разряда - с синхронизнруюшим входом первого триггера, первый входс выходом дискриминатора . мгновенных: значений, второй вход — с первым входом. регистра сдвига, входом строб-генератора и синхронизирующим входом второго триг» гера, третьи входы - с выходными регист959274 рами сдвига, выход старшего разряда которого соединен с Р -входом второго триггера, при этом четвертый вход регистра хранения соединен с выходом первого триггера и вторым входом блока управления, 5 пятый вход — с Р -входом второго триггера и пятым выходом блока управления, шестой вход - с шестым выходом блока управления и вторым входом регистра сдвига, инверсный выход старшего разря- 10 да которого соединен с Х-входом второI

ro триггера, выход которого соединен

c и g -входами первого триггера.

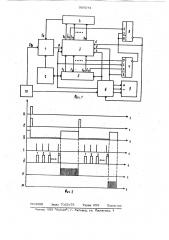

На фиг. 1 представлена структурная схема аналого-цифрового стробоскопического преобразователя; на фиг. 2 - временные диаграммы, поясняющие работу аналого-цифрового стробоскопического пре образователя (АБСП) .

АБСП содержит ДМЗ 1, строб-генера- 20 тор 2, регистр 3 хранения, ЦАП 4, регистр

5 ; сдвига, блок 6 управления, триггеры

7 и 8, декадный реверсивный счетчик 9, источник 10 входного сигнала.

Преобразователь имеет два режима ра-25 боты: режим уравновешивания, включающий И тактов; и режим обработки. В режиме уравновешивания производится преобразование входного сигнала в цифровой код по программе поразрядного уравнове- З0 шивания, а в режиме обработки - коррекция,аддитивной погрешности и преобразование двоичного кода в двоично-десятичный.

В начале цикла преобразования блок 6 управления формирует на первом выходе импульс "Сброс" (фиг. 2 ) и на шестом выходе импульс "Установка" (фиг. 2 д ) .

Импульс "Сброс" поступает на вход сброс реверсивного декадного счетчика 9, который устанавливается в нулевое состояние, а импульс Установка - на шестой вход

It Ф

40 .регистра 3 хранения и второй вход регистра 5 сдвига, при этом во всех разрядах регистра 3 хранения и 5 сдвига, кроме первого, записываются нули, а в первом разряде записывается единица

Кроме того, на четвертый вход регистра 3 . хранения с выхода триггера 8 режима поступает уровень логического нуля (фиг, 2 3 }. На выходе UAH 4, управляемого цифровым кодом с регистра 3 хранения, появляется компенсирующее напряжение Ug, соответствующее старшему разряду ЦАП, и начинается первый такт уравновешива ния.

По сигналу строб-генератора 2 (фиг,2p )l

ДМЗ 1 сравнивает мгновенное значение

1 входного сигнала 0 (с компенсирующим сигналом обратной связи 0 и, в зависимости От ИХ Соотиощеиия, выдает цнфро вой сигнал Много или Мало, на первый вход регистра 3 хранения.

Если сигнал обратной связи превышает мгновенное значение входного сигнала, то на выходе ДМЗ 1 появится сигнал

Много"„которому соответствует уровень логической единицы. Этот сигнал установит старший разряд регистра 3 хранения в нулевое состояние и, тем c&» мым, выключит старший разряд 1ИП.

Если сигнал обратной связи Ug окажется меньше входного, то в старшем разряде регистра 3 хранения останется 1, при этом одновременно блок 6 управлении выдает тактовый импульс (фиг. 2 д}, по которому в следующий разряд регистра 3 хранения .записывается 1 ", который перепишется в следующий разряд регистра 5 сдвига, и начнется второй такт уравновешивания, на котором включается следующий разряд ИАП и повторяется операция сравнения.

Тактовые импульсы, управляющие работой преобразователя в режиме уравновешивания, вырабатывает блок 6 управления, согласно сигналам синхронизации от источника входного сигнала 10.

Процесс уравновешивания протекает по программе поразрядного уравновешивания и заканчивается, независимо от величины входного сигнала, через М тактов, где,И вЂ” число разрядов преобразователя.

На N+ 1 такте включается вспомогатель ный триггер 7, в который р -ным тактовым импульсом переписывается единица из последнего разряда регистра 5 сдвига.

В регистре 3 хранения к этому моменту уже сформирован код, соответствующий мгновенному значению входного сигнала.

Уровень логического нуля, появившийся на инвертирующем выходе .триггера 7, на р+ 1 такте преобразования переключает триггер 8 в положение, соответствующее режиму обработки информации. В этом режиме на вход блокировки регистра 3 хранения поступает уровень логической "1" (фиг. 23}.

В режиме обработки блок 6 управления прекращает формировать тактовые импульсы, связанные по времени с повторяющимся входным сигналом, и включает источник счетных импульсов высокой частоты, входящий. в состав блока.

Счетные импульсы поступают из блока

6 управления на пятый вход регистра 3 и на установочный Я -вход триггера 7.

Первый импульс выключает триггер 7 и, тем самым, снимает уровень логического .

3 9592

0" с установочного входа триггера 8 режима. Вычитание импульсов иэ кода, находившегося в регистре 3 хранения к началу режима обработки, продолжается до тех пор, пока во всех разрядах регистра 3 5 хранения не появятся нули, а в старшем разряде регистра 3 хранения — единица, при этом с инвертируюшего вы ода старшего разряда поступает сипнал на синхронизируюший вход триггера 8 и устанавли-10 вает его в положение, соответствующее режиму уравновешивания.

Таким образом, число счетных импуль. сов, поступившее в регистр хранения, на единицу превышает число, записанное в этом регистре в результате уравновешивания, что эквивалентно поотоянному ад дитивному сдвигу результата преобразования. Точно такое же число счетных импульсов поступает с блока управления на де- 2й кадный реверсивный счетчик 9, причем .. число импульсов, соответствующее мгновенному значению входного сигнала в момент 4"- t. поступает с третьего выхода блока 6. уйравления на вход "Сложение (фиг. 2 8 ), реверсивного декадного счетчика 9, а число импульсов, соответствующее точке сигнала, принятой за нулевой уровень, при Ь =10 с второго выхода блока 6 управления - на вход "Вычитание% (фиг. 2Ж) счетчика 9.

Блок управления формирует импульс установки каждый раэ при включении режима уравновешивания (фиг, 2 6 ), а импульс Сброс" - только в начале цикла преобразования (фиг. 2 О}.

После завершения цикла преобразования в декадном реверсивном счетчике 9 находится двоично-десятичный код, соответствующий истинному мгновенному зна-ар чению сигнала в момент + = относи, тельно уровня, принятого за нулевой.

Задание точки на входном. сигнале, в которой производится его преобразование в цифровой код (t =+р ), и точки, в ко;ц торой уровень сигнала принимается за нулевой (4. = t < ), осуществляется путем изменения задержки тактовых импульсов, формируемых блоком 6 управления относительно сигнала - синхронизации, поступаю«у щего на блок управления от источника внешнего сигнала 10. формула изобретения

Аналого-цифровой стробоскопический преобразователь, содержащий дискриминатор мгновенных значений, первый вход которого соединен с выходом цифроанае логового преобразователя, второй входс выходом строб-генератора, третий вход- с первым выходом источника входного напряжения, второй вход которого соединен с первым входом блока управления, первый выход которого соединен с входом сброса декадного реверсивного счетчика, второй выход - с входом вычитания де» . кадного реверсивного счетчика, третий выход - с входом сложения декадного реверсивного счетчика, четвертый выход- с входом строб-генератора, о т л и ч а ю шийся тем, что, с целью повышения бис тродейс твия преобразователя, в него введены два триггера, регистр

1 сдвига и регистр хранения, прямые выхо, ды всех разрядов которого соединены с входами цифроаналогового преобразователя, инверсный выход старшего разряда — с, синхронизируюшим входом первого тригге: ра, первый вход - с выходом дискриминатора мгновенных значений, второй вход « с первым входом регистра. сдвига, входом строб-генератора и синхронизируюшим входом второго триггера, третьи входы с выходами регистра сдвига, выход старшего разряда которого соединен с „ »вхо дом второго триггера, при этом четвертый вход регистра хранения соединен с выходом первого триггера и вторым входом блока управления, пятый. вход — с P axo дом второго триггера и пятым выХодом блока управления, шестой вход — с шестым выходом блока управления и вторым входом регистра сдвига, инверсный выход старшего разряда которого соединен с -входом второго триггера, выход кото рого соединен с 3- и g -входами первого триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 565391, кл. Н 03 К 13/17, 1977 . (прототип ) . т