Устройство для интегрирования сигнала

Иллюстрации

Показать всеРеферат

Союз Советских, Сециалистичесиих

Реслублии

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<»>960853 (5I ) Дополнительное к авт. санд-ву— (22) Заявлено 17. 02. 81 (21) 3250598/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 23.09.82 ° Бюллетень № 35

Дата опубликования описания 25. 09. 82 (52 ) М. Кл.

G 06 G 7/186

2Ьеуаарстееннмй камнтет

СССР вв делам кзоеретений и открытии (53) УДК 681.

335(O88.8) (72) Авторы изобретения от Я п)()3Ц Я 11 А ТЕН ТН ОТЕХНИЧЕСКАЯ

ВИ1ЛИОТЕХА

В. М. Федулов, A. И. Майзель и В. К. Лебедев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ СИГНАЛА

Изобретение относится к электронике и вычислительной технике.

Известны устройства для интегрирования, содержащие интегратор со .схемой запоминания дрейфа (1 J и (2) .

Недостатками этих устройств являются ограниченное время интегриро,вания, низкая точность и устойчивость вследствие того, что схема запоминания дрейфа может работать толь ко до и после интегрирования.

Наиболее близким по технической сущности к предлагаемому является устройство для интегрирования сигнала, содержащее интегрирующую схему, состоящую из интегратора, включающего усилитель постоянного тока и предварительный усилитель, установленный на входе интегратора. В каче- 2о стве усилителя постоянного тока интегратора используется дифференциальный усилитель со схемой запоминания дрейфа (3 ).

Недостатками известного устройс;ва . являются ограниченное время интегрирования и нйзкая точность работы схемы вследствие того, что схема запоминания дрейфа может работать только до и после интегрирования. В процессе работы на вход интегратора подается напряжение, соответствующее дрейфу, приведенному ко входу, с запоминающего конденсатора. Это напряжение вырабатывается схемой запоминания дрейфа перед интегрированием.

Ограниченное время интегрирования снижает функциональные воэможности интегратора. Дрейф, имеющий место в процессе интегрирования, не устраняется до окончания цикла интегрирования, что снижает точность работы схемы, особенно при длительном цикле интегрирования.

Кроме того, нестабильность коэф-фициента усиления и постоянной времени интегрирования из-за того, что в интеграторе отсутствует отрицатель960853

1о

15 го

so ная обратная связь по постоянному току, снижает стабильность работы схемы. При введении отрицательной обратной связи резко уменьшается постоянная времени из-за шунтирующего действия сопротивления обратной связи.

Целью изобретения является повышение точности и стабильности постоянной времени интегрирования. Указанная цель достигается тем, что в устройство для интегрирования сигнала, содержащее предварительный усилитель, подключенный ко входу запоминающего усилителя, выход котЬрого является выходом устройства, блок запоминания дрейфа и первый ключ, вход которого через первый масштабный резистор соединен с входом устройства, введены формирователь импульсов стабильной скважности, интегрирующий конденсатор и второй ключ, включенный между выходом первого ключа и первым входом предварительного усилителя, второй 2З вход и выход которого соединены соответственно с выходом и входом блока запоминания дрейфа, интегрирующий конденсатор включен между выходом запоминающего усилителя и общим выводом первого и второго ключе%, управляющие входы которых соединены с первым выходом формирователя импульсов стабильной скважности, второй выход которого подключен к управляющему входу блока запоминания дрейфа, зз а также тем, что запоминающий усилитель выполнен на дифференциальном усилителе, неинвертирующий вход которого является входом запоминающего

4О усилителя, а инвертирующий вход через второй масштабный резистор соединен с шиной нулевого потенциала и через параллельно соединенные третий масштабный резистор и интегрирующий конденсатор — с выходом дифференциального усилителя. !

Кроме того, предварительный усили.тель выполнен на дифференциальном .усилителе, инвертирующий вход которого является первым входом предва.рительного усилителя и через четвертый и пятый масштабные резисторы соединен соответственно с шиной нулевого потенциала и выходом дифференциального усилителя, причем неинвертирующий вход и выход дифференциального усилителя явллютсл соответственно вторым входом и выходом предварительного усилителя.

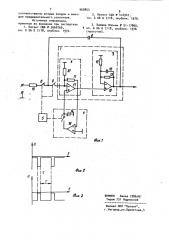

На фиг. 1 приведена принципиальная схема, устройства для интегрирования сигнала; на фиг. 2 и 3 - эпюры напряжений на управляющих входах электронных ключей.

Устройство для интегрирования сигнала содержит интегратор 1, состоящий из предварительного усилителя

2, запоминающего усилителя 3, блока

4 запоминания дрейфа, формирователь

5 .импульсов, электронные ключи 6-8.

На инвертирующем входе предварительного усилителя 2 последовательно стоят ключи б и 8. Выход предварительного усилителя 2 подключен ко входу запоминающего усилителя 3.

" Блок 4 соединен своим входом с выходом предварительного усилителя 2, а выход его через электронный ключ 7 подключен к неинвертирующему входу предварительного усилителя 2. Интегрирующий конденсатор 9 подключен меж-.

t ду выходом устройства и общим выводом ключей 6 и 8. Управляющие входы всех ключей соединены с формирователем 5 импульсов стабильной скважности. Резисторы 10 и 11 предназначены для задания коэффициента усиления предварительного усилителя 2, а 12 и

13 — коэффициента усиления запоминающего усилителя 3.

Конденсатор 14 служит для запоминания напряжения, соответствующего приведенному ко входу дрейфу, на то время, когда ключ 7 разомкнут. Интегрирующий конденсатор 15 подключен параллельно резистору 13. Вход устройства через резистор 16 соединен со входом ключа 6.

Кроме того, устройство содержит операционные усилители 17-19.

Устройство для интегрирования сигнала работает следующим образом.

Формирователь 5 импульсов генерирует импульсы со скважностью 10.

Управляющие импульсы поступают на управляющие входы ключей 6 и 8 (фиг. 2), а также на вход ключа 7 (фиг. 3).Как видно, когда ключи 6 и

8 замкнуты, ключ 7 - разомкнут и наоборот. В течение времени размыкаются ключи б и 8 и замыкается ключ

7, который включает усилитель блока

4 запоминания дрейфа в цепь отрицательной обратной связи усилителя 2.

На выходе блока запоминания дрейфа устанавливается напряжение, соот, 5 9608 ветствующее дрейфу усилителя 2, приведенному ко входу. В течение времени Т, когда ключ 7 разомкнут, напряжение комг1енсации дрейфа поступает на вход усилителя 2 с запоминающего 5 конденсатора 14. Ключ 8 служит для того, чтобы разрывать входную цепь усилителя 2 на время работы блока запоминания дрейфа, а ключ 7 - для ого, чтобы за это же время интегрирующий конденсатор не разрядился через источник сигнала. Усиление усилителя 2 составляет 2000.

Запоминающий усилитель 3 служит для того, чтобы сгладить провалы вы- 15 ходного сигнала, появляющиеся во время разрыва входной цепи предварительного усилителя.

Запоминающий усилитель 3 имеет коэффициент усиления десять и поэто- 20 му его собственный дрейФ практически не вносит искажений в выходной сигнал.

Формирователь 5 импульсов генерирует управляющие импульсы стабильной 25 скважности, что обеспечивает постоянство коэффициента усиления и, следовательно, стабильность постоянной времени устройства.

Таким образом, воэможность интегри-зо рования неограниченного во времени сиг сигнала с периодической компенсацией дрейфа, повышение точности и устойчивости работы предлагаемого устройства по сравнению с известным определяется тем, что блок запоминания дрейфа включен в цепь ОС безинерционного предварительного усилителя, что позволяет производить компенсацию дрейфа в процессе интегрирования без искажения выходного сигнала.

Разделение функций компенсации дрейфа и запоминания соответственно на предварительный и запоминающийусилители, охват их жесткими обратными связями по постоянному току позволят также получить более стабильный коэффициент усиления и постоян" ную времени по сравнению с известным.

Стабильность коэффициента усиления

54 обусловлена также постоянством скважности управляющих импульсов, генерируемых формирователем импульсов.

Предлагаемое устройство для интегрирования сигнала может применяться для интегрирования или дифференцирования с большой постоянной времени в аналоговых вычислительных машинах и других системах, где необходима

53 4 высокая точность и надежность воспроизведенной интегрирующей функции.

Формула изобретения

1. Устройство дпя интегрирования сигнала, содержащее предварительный усилитель, подключенный ко входу запоминающего усилителя, выход которого является выходом устройства, блок запоминания дрейфа и первый. ключ, вход которого через первый масштабный резистор соединен с входом устройств, отличающееся тем, что, с целью повышения точности и стабильности постоянной времени интегрирования, в него введены формирователь импульсов стабильной скважности, интегрирующий конденсатор и второй ключ, включенный между выходом первого ключа и первым входом предварительного усилителя, второй вход и выход которого соединены соответственно с выходом и входом блока запоминания дрейфа, интегрирующий конденсатор включен между выходом запоминающего усилителя и общим выводом первого и второго ключей, управляющие входы которых соединены с первым выходом формирователя импульсов стабильной скважности, второй выход которого подключен к управляющему входу блока запоминания дрейфа.

2. Устройство по и. 1, о т Ь ич а ю щ е е с я тем, что запоминающий усилитель выполнен на дифференциальном усилителе, неинвертирующий вход которого является входом запоминающего усилителя, а инвертирующий вход через второй масштабный резистор соединен с шиной нулевого потенциала и через параллельно соединечные третий масштабный резистор и интегрирующий конденсатор — с выходом дифференциального усилителя.

3. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что предвари-:, тельный усилитель выполнен на диффенциальном усилителе, инвертирующий вход которого является первым входом предварительного усилителя и че" реэ четвертый и пятый масштабные .резисторы соединен соответственно с шиной нулевого потенциала и выходом дифференциального усилителя, причем неинвертирующий вход и выход диффеоенциального усилителя являются соответственно вторым входом и выходом предварительного усилителя.

Источники информации, принятые во внимание при экспертизе

1. Патент США N 3660769, кл. G 06 G 7/18, опублик. 1972.

960853

2. Патент США 11 416947, кл. G 06 G 7/18, опублик. 1979.

3. Заявка Японии N 51- 17860, кл. G 06 С 7/18, опублик. 1976 (прототип).

ВНИИПИ Заказ 7286/61

Тираж 731 Подписное филиал ППП "Патент", r.Óæãîðîä,óë,ÏðîåêòHàÿ,4