Устройство для узловой синхронизации в системах передачи информации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рес убл (1! ) 960896 (6l ) Дополнительное к авт. свид-ву (22) Заявлено 19.03.81 (21) 3264174/18-24 (5 l ) M. Кл. с присоединением заявки .%

G 08 С 19/28

Н 04 L 1/10

QIOfA6pCT3ENHhlk KOIIIHT9T

СССР ао делам нзобретеннй н открытий (23) Приоритет

Опубликовано 23.09.82. Бюллетень № 35 (53 } Уд К 621. 398 (088 ° 8) Дата опубликования описания 25 .09 .82 (72) Авторы изобретения

О.Б. Дорохов, Т.ф. Дубова и Я.Д. Хацке (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ УЗЛОВОЙ СИНХРОНИЗАЦИИ

В СИСТЕМАХ ПЕРЕДАЧИ ИНфОРИАЦИИ

Изобретение относится к системам передачи информации по каналам связи.

Известно устройство узловой синхронизации декодера сверточного кода, содержащее схему определения метрик путей, схему сравнения метрик путей, а также схемы сравнения приращения метрик с различными порогами $13.

Однако это устройство имеет относительно низкую помехоустойчивость.

Наиболее близким к предложенному по технической сущности является устройство узловой синхронизации сверточного декодера, содержащее узел выделения и распределения последовательности принимаемых канальных символов, выходы которого подключены ко входу декодера, линию задержки, выход которой подключен к первому входу сум о матора по модулю два, выход которого подключен к решающему узлу, выход которого подключен ко входу узла вы,деления и распределения последователь2 ности принимаемых канальных симво<лов 2).

Однако в данном устройстве при ис пользовании кодового генератора, аналогичного одному из кодовых генераторов кодера сверточного кода, существуют периодические последовательности, при которых и при неправильной фазе узловой синхронизации расхождение между входной и выходной. кодовыми последовательностями небольшое.

Так как порог решающего узла, выбранный из расчета устойчивой работы устройства при минимальноч рабочем со отношении сигнал-шум, оказывается в этом случае относительно высоким, то не происходит установка правильной фазы узловой синхронизации, т.е. достоверность устройства невысока.

Целью изобретения является повыше. ние достоверности информации путем повышения чувствительности устройства к неправильной фазе синхронизации при всех возможных входных сигналах.

3 96089

Поставленная цель достигается тем, что в устройство для узловой синхронизации в системах передачи информации, содержащее опознаватель символов, первый вход которого соединен 5 .с входом устройства, выходы - с входами декодера, выход которого соединен . с выходом устройства, блок задержкИ, выход которого соединен с первым входом сумматора по модулю два, выход 1ч которого через формирователь управляющих сигналов соединен с вторым входом опознавателя символов, введен обратный кодер, выход которого соединен входом блока задержки, входы обрат 15 ного кодера подключены к соответствующим выходам опознавателя символов, выход декодера соединен с вторым входом сумматора по модулю два.

Обратный кодер выполнен на суммато- о рах по модулю два и элементах задержки, выход первого элемента задержки соединен с первым входом первого сумматора по модулю два„ выход которого через второй элемент задержки соединен с .первым входом второго сумматора по модулю два и непосредственно— с первым входом третьего сумматора по модулю два, выход второго сумматора по модулю два через третий элемент задержки соединен с вторым входом третьего сумматора по модулю два, выход которого соединен с выходом обратного декодера, вход первого элемента задержки и объединенные вторые входы первого и второго сумматоров по моду35 лю два соединены, соответственно, с первым и вторым входами обратного кодера.

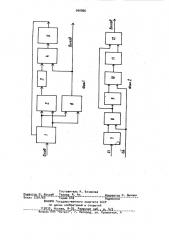

На фиг. 1 приведена схема устрой40 ства; на фиг. 2 - схема обратного кодера.

Устройство для узловой синхрониза-. ции в системах передачи информации содержит опознаватель 1 символов, об45 ратный кодер 2, блок 3 задержки, сумматор 4 по модулю два, формирователь 5 управляющих сигналов, декодер 6. Обратный кодер 2 содержит элемент 7 задержки, сумматор 8 по модулю два, второй элемент 9 задержки, второй сумма- 50 тор 10 по модулю два, третий элемент 11 задержки, третий сумматор 12 по модулю два.. Устройство для узловой синхрониза- 55 ции работает следующим образом.

Полученные в опознавателе 1 канальные символы Cl и С2 подаются на вхо6 ф ды декодера 6 и обратного кодера 2.

В обратном кодере 2 производится вос. становление входной информационной последовательности путем операций, обратных кодированию. С выхода обратного кодера 2 информационная последовательность поступает на вход блока 3 задержки, где она задерживается на время, необходимое для обработки информации в декодере 6. Полученные информационные последовательности с выхода декодера 6 и с блока 3 задерж ки подаются на входы сумматора 4 по модулю два, где происходит их сравнение.

Предлагаемое устройство в отсутствии шумов при неправильной фазе не выходе сумматора 4 .по модулю два при любой информационной последовательности имеет 50/ ошибочных символов, про шедших за время выбранного мерного ин- тервала, например если выбрать мерный интервал равным 256 символам, количество ошибок равно 12811. С выхода формирователя. 5 сигнал управления подается на опознаватель 1 символов, выставляя в нем правильную фазу узловой синхронизации, В обратном кодере 2 исправление канальных ошибок, возникающих при шумах в канале, не осуществляется и да" же увеличивается в 2-2,5 раза, однако и при наличии шумов при неправильной фазе узловой синхронизации рассогласование между двумя указанными последовательностями равно примерно половине. Обратный кодер 2 для сверточного кода с кодовым ограничителем Клб представляет собой логическую схему (фиг. 2).

Алгебраические преобразования, происходящие в обратном кодере, рассмотрим на примере работы со сверточным кодом, порождаемым полиномами

g(() д1 д - д 3+дв+дь

1 (СЫ «Д+Д -,Ць.

Зададим входную последовательность

0000001000000..., т.е. т(х) = O", тогда „=ю(х)Ь(с ) =д +д д" д д" с, =Их ) М(сг) =Д + 3 + Я" .

Проверим работу обратного кодера 2, работающего по схеме, изображенной на фиг. 2:

<. r „=С O+C2 =3 +3ь+Л +Л" Л"

Ъе дч,д ь

g

2.Д, =Д +Д

ДЬ дФ д1Ъ

g

4. Д =д9 д о„д1

Формула изобретения

Таким образом, обратный кодер 2 1$ . вырабатывает входную последовательность, задержанную на два бита.

Проведенное моделирование на ЭЦВИ показывает, что при работе в шумах при отношении энергии сигнала к спект 20 ральной плотности шума — = 2,44 при

Е

„Йо правильной фазе узловой синхронизации за время мерного интервала в 256 символов количество ошибок равно 60, при неправильной фазе узловой синхрониза- 2$ ции количество ошибок возрастает до

128.

Таким образом, устанавливая порог счетчика (не показан) формирователя 5 в середине интервала между количест- 30 вом ошибок при правильной и неправильной фазах устройства узловой синхронизации, т.е. равным 128+60 4

I обеспечивают устойчивую работу устрой3S ства для узловой синхронизации при любых входных последовательностях.

1. Устройство для узловой синхронизации в системах передачи информа" ции, содержащее опознаватель символов, первый вход которого соединен

96 6 с входом устройства, выходы — с входами декодера, выход которого соединен с выходом устройства, блок задержки, выход которого соединен с первым входом сумматора по модулю два, выход которого через формирователь управляющих сигналов соединен с вторым входом опознавателя символов, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности информации, в него введен обратный .кодер, выхрд которого соединен с входом блока задержки, входы обратного кодера подключены к соответствующим выходам опознавателя символов, выход декодера соединен с вторым входом сумматора по модулю два.

2. Устройство по и. 1, о т л и ч аю щ е е с я тем,. что обратный кодер выполнен на сумматорах по модулю два и элементах задержки, выход первого элемента задержки соединен с первым входом первого сумматора по модулю два, выход которого через второй weмент задержки соединен с первым входом второго сумматора по модулю два и непосредственно - с первым входом третьего сумматора по модулю два, выход второго сумматора по модулю два через третий элемент задержки соединен с вторым входом третьего сумматора по модулю два, выход которого соединен с выходом обратного декодера, вход первого элемента задержки и объединенные вторые входы первого и второго сумматоров по модулю два соединены, соответственно, с первым и вторым входами обратного кодера.

Источники информации, принятые во внимание при экспертизе

1. Патент С!ЧА " 3872432, кл. Н 04 L 1/10, опублик. 1975.

2. Авторское свидетельство СССР

1 467484, кл. H 04 -1 1/10, 1975 (прототип).

960896

Составитель Н. Бочарова

Реаактоо fl. Коссей Техреа А. Ач Коаректор М. немчик

«н ° »»«««««««««ъг »« ° а

3» В ° « ° Закаэ 7291/63 Тираж 642 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Рауаская наб. д. 4/5 и» +» «2 ã

Филиал ППП "Патент, г. Ужгород, ул. Проектная,