Транзисторный инвертор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическик

Республик

«»961079 (6!) Дополнительное к авт. свид-ву

Р М К з (22) Заявлено 17.02. 81 (21) 3248382/24-07 с присоединением заявки М

Н 02 M 7/537

{53) УДК 621.314. . 57 (088. 8) Государственный комитет

СССР но делам изобретении и открытий

{23) Приоритет

Опубликоваио23.09.82. Бюллетень Мв 35

Дата опубликования описания 23.09.82 (72) Автор изобретения

В ° А. Рычков

l g ) г .-.- -, (:р, j « г »

/ г.

Волжское объединение по производству легковых.,,-- / автомобилей (71) Заявитель (54 ) ТРАНЗИСТОРНЫЙ HHBEPTOP

Изобретение относится к электротехнике и может быть использовано . во вторичных источниках питания.

Известны транзисторные инверторы которые для уменьшения мгновенной мощности, выделяющейся при выключении силовых транзисторов и для обеспечения, тем сажам, надежной работы транзисторов, снабжены защитными RS и ЙСD-цепями. Дополнительную RS- и (или)RСО-цепь подключают в таких преобразователях к выводам коллектор — эмиттер каждого силового транзистора В эту цепь ответвляется ток нагрузки в течение времени выключения силового транзистора, при этом снижается мгновенная мощность, рассеиваемая транзистором при выключении,и уменьшается вероятность вторичного пробоя транзистора (1). Недостатком данного преобразователя является относительно большая мощность, рассеивающаяся на резисторах защитных цепей при помощи нагрузки более нескольких киловатт.

Наиболее близким техническим решением к изобретению является инвертор, содержащий транзисторы, формирователь импульсов управления, подключенный к базам транзисторов, дополнительные источникй питания и защитные цепи, состоящие иэ резистора и двух диодов, один из которых подключен параллельно резистору, а второй диод — встречно последовате. льно с первым диодом 121.

Целью изобретения является пОВь>щенке надежности преобразователя.

Поставленная цель достигается тем,что в инверторе точка соединения коллекторов верхних транзисторов

15 з стойки соединена с положител ным ь зажимом первого дополнительного источника питания, отрицательный за" жим которого подключен к точке соединения защитны!с цепей упомянутых транзисторов, а точка соединени эмиттеров нижних транзисторов стойки и точка соединения защитных цепей соей динены соответственно с отрицател ным ь положительным зажимом второго дополнительного источника.

Кроме того, транзисторный инвертор снабжен двумя пороговыми уст- . р9йствами, выходы которых через схе му ИЛИ подсоединены к блокирующему входу формирователя импульсов управ961079 ления, а входы - к соответствующему дополнительному источнику.

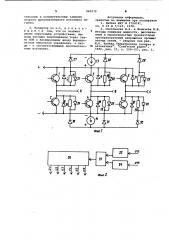

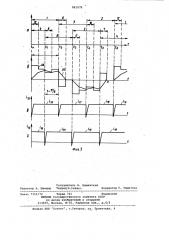

На фиг. 1 приведена схема, поясняющая работу устройства;,на фиг.2 схема управления устройством на примере схемы трехфазного инверто- 5 ра, где V1, V2, VÇ, Ч4, Ч5, Чб сигналы управления транзисторами

1 - б, а V13, Ч14 - напряжения дополнительных источников 13 и 14 пи- тания; на фиг. 3 - эпюры характер- 10 ных напряжений и токов при работе трехфазного инвертора для продолжительиости открытого состояния трано зисторов 3 = 120; на фиг. Зс приведена диаграмма работы полупроводнико- g вых элементов силовой цепи транзисторного инвертора; на фиг. Зд — эпюры напряжения фазыЛ(0 А ) и ее тока (IA); на фиг. 34, a — эпюры токов дополнительных источников питания I<> и I„4 . где 1, 1 6, \и, ср (д, ао токи, протекающие через дИоды 15 — 20 соответственно.

Схема транзисторного инвертора (фиг. 1) содержит силовые транзисторы

1 — 6, обратные диоды 7 - 12, первый и второй дополнительные источники 13 и 14 питания, соединенные через защитные цепи, состоящие из резисторов

15 — 20, первых .диодов 21 — 26 и встречно-последовательных диодов 27 - З0

32 соответственно с положительным или отрицательным зажимом источника

TIHTcLHHH

Транзисторный инвертор имеет также устройство управления, состоящее из35 двух пороговых устройств 33 и 34, схемы ИЛИ 35 и формирователя 36, вырабатывающего. импульсы управления транзисторами 1 — б.

Работа схемы происходит следующим 40 образом.

За исходное состояние примем момент времени и, когда открыты транзисторы 1 и 4 (фиг. 2, Зд,о, 2), при этом токи дополнительных источников 45 питания протекают по. цепям: положительный зажим дополнительного источника 13 питания — транзистор 1 резистор 15 — диод 27 — отрицательный зажим дополнительного истсчника

14 питания — диод 31 — резистор 19 транзистор 4 — отрицательный зажим дополнительного источника 14 питания» В момент времени с„ = 7Г/6 к переход база — эмиттер транзистора 4 прикладывается запирающее напряжение.

Транзистор 4 закрывается, при этом ток нагрузки, ответвляясь в цепь 19, 25, 31, запирает диод 31. Как следст-. вие, мгновенная мощность, выделяющаяся в транзисторе 4, на этапе вы- 60 ключения,не достигает больших значений, что защищает транзистор 4 от возможности вторичного пробоя.

В этот же момент времени включается транзистор б (фиг. 3 ), подго- 65 тавливая к работе защитную цепь 20

31., 32. Включение и выключение тран зисторов 2, 4 и 6 происходит в мо,менты времени, t>, t (Ъиг. 34) и защитные цепи 20, 26 и 32 ; 18, 24 и 30; 31, 19 и 25 подключаются поочередно к дополнительному источнику "4 питания, обеспечивая снижение мгновенной мощности на этапе выклкчения в транзисторах 6, 2 и 4 соответственно.

Аналогично, со сдвигом Х/б в моменты времени t<, t4, t6 к дополнительному источнйку 13 подключаются защитные цепи 16; 2 и 28; 17, 23 и 29; 15, 21 и 27, обеспечивая снижение мгновенной мощности на этапе выключения в транзисторах 3, 5 и 1 соответственно.

В случае неисправностей в одном из дополнительных источников 13,. 14 питания или пропадании напряжения на них, срабатывают пороговые устройства

33 или (и) 34, блокируя через схему

ИЛИ 35 подачу импульсов отпирания транзисторов 1 — 6.

Включение двух дополнительных источников питания для обеспечения работы двух групп защитных цепей вместо одного дополнительного источника питания на каждый силовой транзистор позволяет увеличить надежность работы транзисторного инвертора, а также улучшить его массогабаритные показатели.

В общем случае число фаз инвертора может быть больше и меньше трех, транзисторы могут быть составными, может быть применено управление с другими возможными длительностями открытого состояния транзисторов Л

Формула изобретения

1. Транзисторный инвертор, содержащий транзисторы, формирователь импульсов управления, подключенный к базам транзисторов, дополнительные источники питания и защитные цепи, состоящие из резистора и двух диодов, один из которых подключен параллельно.-резистору, а другой последователь-. но с ним и встречно с первым диодом, отличающийся тем, что, с целью повышения надежности работы транзисторного инвертора, точка соединения коллекторов верхних транзисторов стойки соединена с положительным зажимом первого дополнительного источника питания, отрицательный зажим которого подсоединен к точке соединения защитных цепей указанных транзисторов, а точка соединения эмиттеров нижних транзисторов стойки и точка соединения защитных цепей подключена соответственно к отрнца961079 тельному и положительному зажимам второго дополнительного источника питания, 2. Инвертор по п.1, о т л и ч а— ю шийся тем, что он снабжен двумя пороговыми устройствами, выходы которых подсоединены через схему ИЛИ к блокирующему входу формирователя импульсов управления, а входы — к соответствующему дополнительному источнику.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ У 2724741, кл. H 02 М 7/122, 1978.

2. Охотникова В.A. и Фомичева В.В.

Методы снижения мощности, рассеиваемой в высоковольтных транзисторах преобразователей напряжения промап ленных сетей. — Сборник под ред.

Ю.И. Конева.".Ýëåêòðîííàÿ техника в

10 автоматике". "Советское радио", 1980, вып. 11, с. 100-105, рис. 1 ° !

9б1079

Составитель Н. Цишевская

Редактор A. Шандор ТехредМ.Рейвес Корректор Г. Решетник

Закаэ 7310/72 Тираж 721 Подписное

ВНИИПИ Государственного комитета СССР

IIo делам иэобретений и открытий

113035, Москва, К-35, Раушская наб., д.4/5 филиал ППП "Патент", г,Ужгород, ул. Проектная, 4