Трехканальный аналоговый мажоритарный элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соцналмстнческмх

Республик

Опубликовано 23.09.82. Бюллетень Мв 35

Дата опубликования описания 23 .09. 82 (5l)M. Кл.

Н 03 K 19/23

1ЬеудзрстееикыИ коиктет

СССР оо делен иеобретеник н открытой (53) УДК621. 374 (088.8) (72) Авторы изобретения (71) Заявитель (54) ТРЕХКАНАЛЬНЫЙ АНАЛОГОВЫЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ

Изобретение относится к аналоговой технике и может быть использовано для увеличения надежности прецизионных устройств с непрерывным выходным сигналом.

Известно устройство, содержащее и диодных мостов (где n — число резервируемых приборов, нечетно и более двух), 2п балансных резисторов и источник напряжения постоянного тока, выполняющее операцию усреднения большинства сигналов, выходящих за пределы допустимых отклонений (1 J.

Недостатком известного устройства является большая потребляемая мощность.

Известен трехканальный аналоговый мажоритарный элемент, содержащий три канала управления, каждый из которых состоит из элемента сравнения, плюсо20 вой вход которого подключен к соответствующей входной шине, а минусовой — к плюсовому входу элемента сравнения последующего канала управления, 2 инвертора и логического элемента

2И-2ИЛИ-НЕ, выход которого является соответствующим выходом устройства(2).

Недостаток этого устройства заключается в том, что благодаря высокой чувствительности элементов сравнения, помехи, возникающие в резервируемых источниках входных сигналов устройства величиной до 5-10 МВ, отслеживаются элементами сравнения, что в свою очередь сказывается на реше- „ нии, выбираемом логическими элементами,и приводит к неоправданным переключениям резервируемых источников сигналов.

Целью изобретения является повышение помехоустойчивости трехканального аналогового мажоритарного элемента.

Для достижения поставленной цели с трехканальном аналоговом мажоритарном элементе, содержащем три канала управления, каждый из которых состоит из элемента сравнения, плюсовой

3 96114 вход которого подключен к соответствующей входной шине, а минусовой - к плюсовому входу элемента сравнения последующего канала управления, и логического элемента 2И-2ИЛИ-НЕ, выход которого является соответствующим выходом устройства, в каждый канал управления введен Dt-триггер, при этом информационный вход Dt-триггера подключен к выходу элемента сравне- щ ния соответствующего канала управления, а тактовый вход Dt-триггера каждого канала управления подключен к шине тактовых сигналов, прямой выход . 0t-триггера подключен к одному из 1 входов первого элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ собственного канала, и к одному из входов второго элемента И, входящего a состав элемента 2И-2ИЛИ-HE последующего 2О канала, а инверсный выход Dt-триггера подключен к второму входу второго элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ собственного канала, и к второму входу первого элемента И, у входящего в состав элемента 2И-2ИЛИНЕ последующего канала.

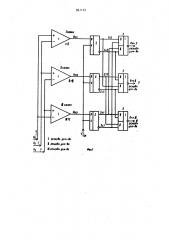

М фиг, 1 представлена электрическая схема предлагаемого устройства; на фиг. 2 - временная диаграмма рабо- з,1 ты устройства.

Каждый из трех каналов устройства содержит элемент 1 сравнения, Dtтриггер 2 и элемент 2И-2ИЛИ-HE 3.

Плюсовой вход каждого из элементов 1

35 подключен к соот ветствующей входной шине 4-6. Минусовой вход элемента 1 первого канала управления подключен к плюсовому входу элемента l второго канала управления, соответственно, 4О минусовой вход элемента 1 второго канала управления - к плюсовому входу элемента 1 третьего канала управления, а минусовой вход элемента

1 третьего канала управления - к

45 плюсовому входу элемента 1 первого канала управления. Тактовый вход каждого из 0t-триггеров 2 под-. ключен к шине 7 тактовых сигналов, а информационный вход — к выходу элемента 1 собственного канала.

Прямой выход Dt-триггера 2 в каждом канале управления подключен к одному из входов первого элемента И, входящего в состав элемента 2И-2ИЛИ- .НЕ собственного канала, и к одному из входов второго элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ последующего канала, а инверсный выход

7 4

Dt-триггера 2 подключен к второму входу второго элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ последующего канала. Выходы элементов 2И-2ИЛЙ НЕ являются соответственно выходами

8-10 устройства. . Устройство работает следующим образом.

Входные напряжения с резервируемых устройств (U<, U>, 0 3) поступают соответственно на шины 4-6 для сравнения между собой по величине и на входы "+" и "-" элементов 1 сравнения, на выходах которых формируются. логические уровни, при этом на выходе формируется логический "0", если большее из сравниваемых напряжений поступает на вход "-", и "1", если большее из сравниваемых напряжений поступает на вход "+".

Результаты попарного сравнения трех напряжений (U „-U ), (u -03) и (u3-u„), т. е. выходные сигналы элементов сравнения Осс.! Uññ1è Uññ3 поступают на информационные входы соответствующих Dt-триггеров 2, которые служат для компенсации внешних помех и пульсаций сигналов элементов

1 сравнения. Помехи присутствуют в цепях резервируемых устройств и в момент равенства сравниваемых напряжений усиливаются элементами сравнения, и передаются на выход мажоритарного устройства. Кроме этого, возможно возникновение генерации и в элементах сравнения ввиду их большой чувствительности. Использование 0t-триггеров, которые тактируются синхрочастотой с периодами следования намного большей, нежели пульсация напряжения в элементах сравнения, позволяет демпфировать как внешние помехи, так и собственную генерацию, возникающую в элементах 1 сравнения.

Так, например, в выходном напряжении цифро-аналоговых преобразователей всегда присутствуют всплески в моменты смены кодовых состояний. В этом случае на тактовые входы 0t-триггеров должны поступать синхроимпульсы с частотой следования, не совпадающей со сменой кодовых состояний, что и поясняется временной диаграммой (фиг. 2).

Смена кодовых состояний отслеживается в выходных напряжениях резервируемых устройств Uq, U g и 0 с периодом следования "Т" в виде всплесков, а в момент равенства этих на5 9611 пряжений они появляются на выходе элемента 1 сравнения в виде пульсаций (для случая U U > на выходе

Осс ) . Запись информации в Dt-триггерах осуществляется при поступлении импульсов CU на шину 7, имеющих также период следования Т, но сдвинутых относительно смены кодовых состояний, при этом выходная информация триггеров Q„, Q>, Q > не имеет не- о однозначности и сигналы на включение

I II1 резервированних устройств с выходов элементов 2И-2ИЛИ-НЕ 3 также не имеют неоднозначности.

В моменты времени t<-t < (точка 2 15 на фиг. 2) триггер 2 первого канала управления может иметь два состояния. при этом включается либо I, либо II резервированное устройство, но на точность передачи информации это не рв влияет, поскольку U < = 02. Аналогич но, точность передачи информации не нарушается для момента времени t -t (точка 3 на фиг. 2). В то же время всплески сигналов на выходах элементов сравнения в других точках (точки

1 и 4) даже при наличии больших помех (как 0 ) не сказываются на работу устройства в целом.

Таким образом, при правильном выбо.зв ре частоты следования импульсов синхронизации, поступающих на тактовые входы Dt-триггеров, можно полностью исключить влияние помех на работу аналогового мажоритарного элемента. 35

Формула изобретения

Трехканальный аналоговый мажоритарный элемент, содержащий три канала

47 6 управления, каждый из которых состоит из элемента сравнения, плюсовой вход которого подключен к соответствующей входной шине, а минусовой к плюсовому входу элемента сравнения последующего канала управления, и логического элемента 2И-2ИЛИ-НЕ,,выход которого является соответствующим выходом устройства, о т л и ч аю шийся тем, что, с целью повышения помехоустойчивости, в каждый канал управления введен Dt-триггер, при этом информационный вход Dt-xpwrrepa подключен к выходу элемента сравнения соответствующего канала управления, а тактовый вход Dt-триггера каждого канала управления подключен к шине тактовых сигналов, прямой выход

Dt-триггера подключен к одному из входов первого элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ собственного-канала, и к одному из входов второго элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ последующего канала, а инверсный выход Dt-триггера подключен к второму входу второго элемента И, входящего в состав элемента 2И-2ИЛИ-НЕ собственного канала, и к второму входу первого элемента И, входящего в соствв элемента

2И-2ИЛИ-НЕ последующего канала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ю 190664, кл. G 06 F 7/02, 1958.

2. Авторское свидетельство СССР

II 558432, кл . Н 05 К 10/00, 1976.

961147

ИСС1

Исс ссз

СИ

ВНИИПИ Заказ /319/76 Тираж 959 Подписное филиал ППП "Патент", г. Ужгород, ул. Проектная,